The fastest Verilog/SystemVerilog simulator!

Posted _

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了The fastest Verilog/SystemVerilog simulator!相关的知识,希望对你有一定的参考价值。

Verilator is the fastest Verilog/SystemVerilog simulator.

Verilator is invoked with parameters similar to GCC or Synopsys\'s VCS. It "Verilates" the specified Verilog or SystemVerilog code by reading it, performing lint checks, and optionally inserting assertion checks and coverage-analysis points. It outputs single- or multi-threaded .cpp and .h files, the "Verilated" code. The user writes a little C++/SystemC wrapper file, which instantiates the "Verilated" model of the user\'s top level module. These C++/SystemC files are then compiled by a C++ compiler (gcc/clang/MSVC++). The resulting executable performs the design simulation. Verilator also supports linking its generated libraries, optionally encrypted, into other simulators.

Verilator:

- 有源码 git clone https://github.com/verilator/verilator

- Outperforms many commercial simulators

- Wide industry and academic deployment

- Out-of-the-box support from Arm, and RISC-V vendor IP

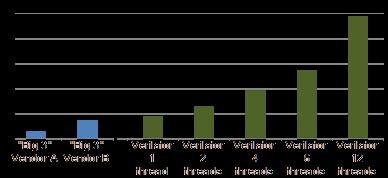

iverilog生成"汇编",vvp从汇编生成字节码,然后解释执行。On a single thread Verilator is about 100 times faster than interpreted Verilog simulators such as Icarus Verilog. Another 2-10x speedup might be gained from multithreading (yielding 200-1000x total over interpreted simulators). 但是: Icarus is a full featured interpreted Verilog simulator. If Verilator does not support your needs, perhaps Icarus may.

我一直幻想的东西有人做了,我再幻想另一个: CLogic - Concise Logic,or China Logic. 先照抄Verilog的RTL (Register Transfer Level)部分,但是begin,end换,endmodule换,然后模仿Chisel加功能。词法和语法分析用flex, bison或python的ply来做,CLogic编译器可以用python来写。CLogic编译器的输出是.v文件,然后再用Verilator/Icarus进一步处理。

可行性分析:

- Chisel只有高阶的RTL,然而它是产品不是玩具。

- Chisel源码1,477KB,不是非常巨大的工程。The Chisel Book说Verilog有历史包袱,Chisel小而简单。

- 窃以为RISC-V的精华是它的指令集,Chisel是个败笔。有本书说Verilog比VHDL流行的原因是Verilog语法简单,相对好学。Chisel是个Scala库,Scala的语法鬼画符一样。电路有多重继承吗? extends敲起来不麻烦吗?Scala里可以把一段代码当函数参数,给人能自定义关键字(如when)的错觉,但终究不是100%自由度,===不啰嗦吗?val w = Wire(UInt())要按8次Shift键。简明地描述接线是重点,有必要另造一个语言。

- 但Chisel很有学习价值,比如我是在学Chisel的过程中知道Verilator的。

以上是关于The fastest Verilog/SystemVerilog simulator!的主要内容,如果未能解决你的问题,请参考以下文章