日常记录Verilog

Posted 嘘、小点声

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了日常记录Verilog相关的知识,希望对你有一定的参考价值。

秒的换算

https://baike.baidu.com/item/%E7%A7%92/2924586

1s=10^3ms(毫秒)=10^6μs(微秒)=10^9ns(纳秒)=10^12ps(皮秒)=10^15fs(飞秒)=10^18as(阿秒)=10^21zm(仄秒)=10^24ym(幺秒)

时间单位1ns,10fs精度

`timescale 1ns/10fs

@和wait的区别

两个概念,但是还有点相同的地方。主要是用法的差异。@应该是某时刻点的一种触发,wait似乎是等待一段时间。

在竞争关系中,使用wait可以缓解事件偶尔未被触发。

https://blog.csdn.net/qq_41894346/article/details/104964478

在Verilog中当一个线程在一个事件上发生阻塞的同时,正好另一个线程触发了这个事件,则竞争就出现了。如果触发线程先于阻塞线程,则触发无效(触发是一个零宽度的脉冲)。

Systemverilog 引入了triggered()函数,用于检测某个事件是否已被触发过,包括正在触发。线程可以等待这个结果。

event a; //使用关键字event来声明一个事件a initial begin #1; ->a; end initial begin #1; @a; //第一个进程在1ns后触发了事件a,那么第二个进程在1ns的时候等待a,有可能等的到,有可能等不到,产生竞争 end initial begin #1; wait(a.triggered); //使用wait来等待事件a,这种方式是一定可以等到a的,这是和使用@来等待的区别 end

例子2

https://blog.csdn.net/Michael177/article/details/120807670

triggered()函数,用于检测某个事件是否已被触发过,包括正在触发。线程可以等待这个结果,而不用在@操作符上xx。

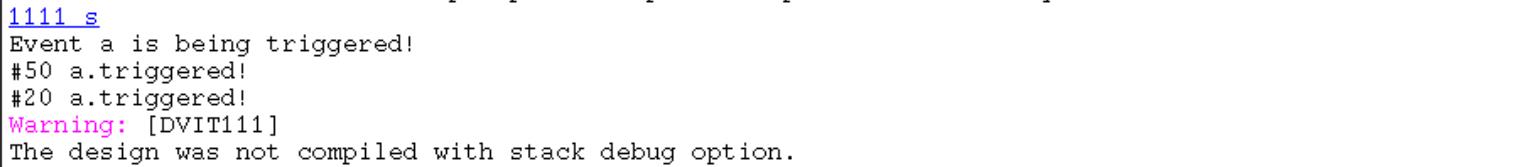

module event_test(); event a; initial begin #50; ->a; $display("Event a is being triggered!"); end initial begin #20; wait(a.triggered); $display("#20 a.triggered!"); end initial begin #50; wait(a.triggered); $display("#50 a.triggered!"); end initial begin #60; wait(a.triggered); $display("#60 a.triggered!"); end endmodule

parameter、interger、reg

https://blog.csdn.net/wuguozeng1989/article/details/46682125

1. integer类型的变量作为有符号数使用,而reg类型的变量则作为无符号数使用。

2. integer的位宽为字的位数,最小为32位

https://blog.csdn.net/qq_16923717/article/details/81067096

3. parameter是常量,不是变量,所以不允许在运行时修改它的值,即不能在组合逻辑或者时序逻辑中对其进行赋值。

Le vent se lève! . . . il faut tenter de vivre!

Le vent se lève! . . . il faut tenter de vivre!

以上是关于日常记录Verilog的主要内容,如果未能解决你的问题,请参考以下文章