ARM DMA Controller PL330 使用经验分享

Posted light-weight-ip

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ARM DMA Controller PL330 使用经验分享相关的知识,希望对你有一定的参考价值。

总体简介

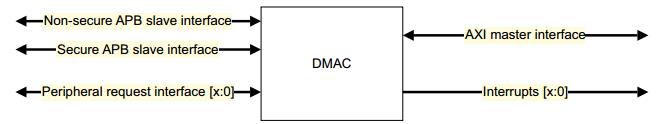

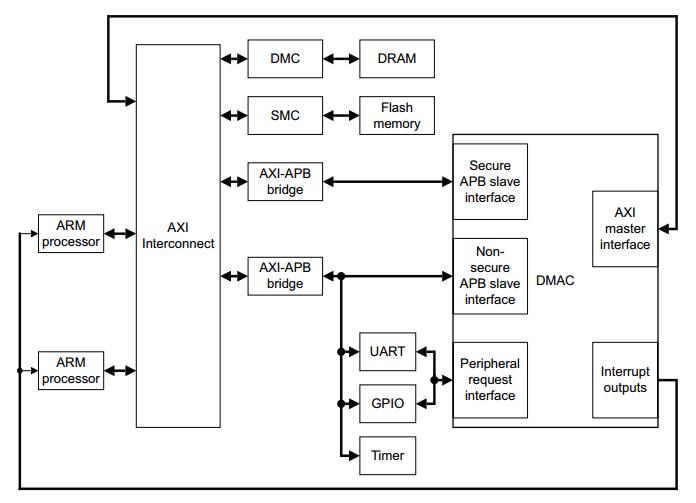

DMAC提供一个AXI主接口来执行DMA传输,并提供两个APB从接口来控制其操作。DMAC采用TrustZone技术,其中一个APB接口运行在secure状态,另一个运行在非secure状态。 secure策略是ARM的TrustZone技术一部分。

整个DMA操作受一个小的指令集控制,这是与传统链表BD模式的不同之处。

由图中可以看出,其支持外设如UART或者GPIO主动trigger发起。

主要特性

▲AXI、APB接口

▲支持mem2me,mem2perh,perh2mem

▲支持scatter-gather BD模式

▲通道security可配

▲丰富的中断/事件源

可配置

AXI数据线宽度

通道数配置

内部buffer深度配置

读指令队列深度

写指令队列深度

外设请求接口数量

中断/事件数量

DMAC Diagram

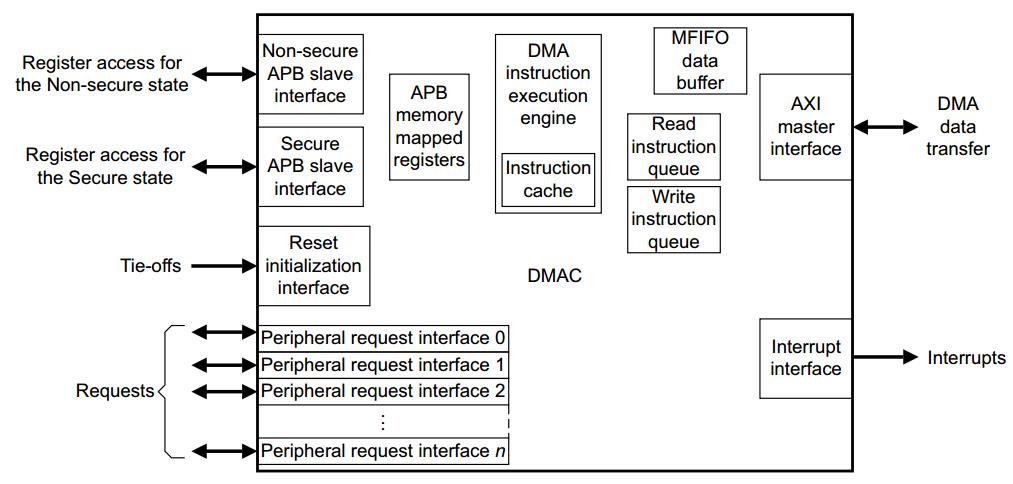

DMAC里面包含一个指令处理模块,指令被存储在指令cache中。最多可以配置为8个通道,每个通道都可以执行一个独立的DMA操作,每个通道线程之间采用轮询仲裁。

MFIFO用于存储读/写的数据

读指令队列深度、写指令队列深度、MFIFO的深度会影响DMA的效率

apb接口可以访问状态寄存器也可以执行DMAC中的指令

apb的地址空间被限定在4KB

接口及功能

apb的时钟与axi为同一个时钟域,且接同一个时钟,但是其提供一个pclken可以控制apb的时钟速率,pclken必须是aclk的整数分频。

DMAC不支持独占或者lock访问,arlock[1:0]、awlock[1:0]需要tie low;不支持wrapping操作,arburst[1]、awburst[1]需要tie low;awcache[2],awcache[3]需要tie low;

ID_MSB与通道数量关联。DATA_MSB和STRB_MSB与配置的数据宽度关联。AWID、WID、ARID将于channel num关联起来,比如通道4发出的请求,其ID将为b100

DMAC会控制ARLEN和ARSIZE根据指令的长度和总线宽度的关系。

指令缓存长度≤AXI数据总线宽度

•ARLEN = 1

•ARSIZE = 以字节为单位的指令缓存长度。

指令缓存长度> AXI数据总线宽度

•ARLEN = 以字节为单位的指令缓存线长度与AXI数据总线宽度之比

•ARSIZE = 以字节为单位的AXI数据总线宽度。

用于设置DMAC的boot地址,boot_from_pc用于指示DMA manager的状态是stopped或exccuting

指令、source data、dst data都是从一个AXI走。

单channel内部带watchdog 防止过长占用总线

DMAC使用前,需要进行一系列软件初始化,这个就不再展开。

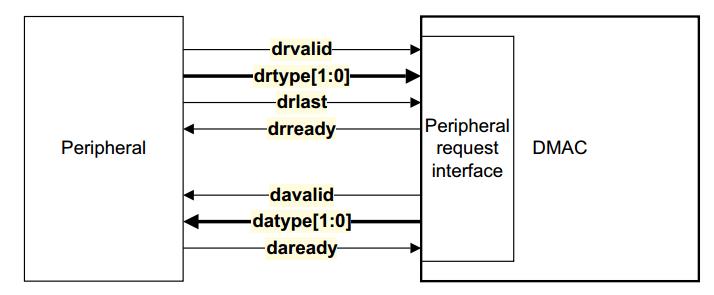

外设请求接口主要采用valid和ready握手协议

drtype[1:0]:

single传输请求

burst传输请求

承认flush请求

datype[1:0]:

single传输完成

busrt传输完成

flush请求

外设请求可以被mapping到任意的DMA channel去

DMA分通道线程和管理线程

一些禁止操作

边界不能跨越4K

不能出现wrapping burst

DMAC不支持非对齐的fix burst

不能发起一次资源长度大于MFIFO的请求,有可能会导致watchdog abort

通过使用得出,ARM的DMA与自身的平台耦合过深,只能用于ARM平台的IP开发

ARM Cortex M7:缓存清理可以覆盖 DMA 设备所做的更改吗?

【中文标题】ARM Cortex M7:缓存清理可以覆盖 DMA 设备所做的更改吗?【英文标题】:ARM Cortex M7: can a cache clean overwrite changes made by DMA device? 【发布时间】:2021-09-28 05:15:44 【问题描述】:我正在为 STM32H743 SoC 中的 DMA 总线主设备开发驱动程序,由 Cortex M7 CPU 驱动。假设我有两个内存位置,x 和 y,它们映射到同一缓存行,它位于正常的可回写缓存内存,并假设以下事件序列:

-

以

x = x1, y = y1 开头,缓存行无效。

CPU 读取y

DMA 设备集x = x2,在内存中

CPU 集y = y2

CPU 清理缓存行。

5.完成后,从DMA设备的角度来看,x = ?

我认为 DMA 会看到 x = x1,这是我的推理:

y 时,缓存行被拉入缓存。它读取x = x1, y = y1,并被标记为有效。

DMA 然后更新内存中的x,但更改不会反映在缓存行中。

当 CPU 设置y = y2 时,缓存行被标记为脏。

当 CPU 清理缓存行时,由于它是脏的,它会被写回内存。

当它被写回内存时,它会读取x = x1, y = y2,从而覆盖

DMA 更改为 x。

这听起来像是一个很好的推理吗?

【问题讨论】:

【参考方案1】:简而言之,如果我的问题是正确的,那么你的描述是正确的。

从问题中不太清楚“两个内存位置,x 和 y”是什么。

根据您在描述中使用它们的方式,我认为它类似于 2 个指针。

int* x, y;

并且“以x = x1, y = y1开头”表示为该指针分配地址,例如

x = (int*)(0x2000); // x = x1

y = (int*)(0x8000); // y = y1

现在回答您的问题:“在 5. 完成后,从 DMA 设备的角度来看,x = ?”

所以在第 3 步之后,x = x2, y = y1 在内存中,x = x1, y == y1 在缓存中。

在第 4 步之后,x = x2, y = y1 在内存中,x = x1, y = y2 在缓存中。

内存中x/y指针的DMA访问值,缓存中x/y指针的CPU访问值。因为缓存和内存不同步(缓存是脏的)在那个阶段CPU和DMA会得到不同的值。

最后在第 5 步之后... 这取决于。缓存控制器通过缓存线、某种大小的内存区域(如 32 字节、64 字节等)(可能更大或更小)进行操作。因此,当 CPU 清理/刷新包含某个地址的缓存行时,它会将整个缓存行的内容刷新到内存中。内存中的任何内容都会被覆盖。

基本上有2种情况:

x 和 y 指针都在同一个缓存行中。这意味着缓存中的值将覆盖内存,您是对的,x = x1, y == y2 将在内存和缓存中完成。

x 和 y 指针位于不同的缓存行中。很简单,只有一个变量会受到影响,另一个缓存行仍然是脏的。

【讨论】:

感谢您的回复。实际上,当我写例如x = x1,我的意思是 *x = x1,抱歉,不清楚。在我写的步骤中,DMA 和 CPU 只改变 *x 和 *y,而不是 x 和 y。尽管如此,我相信你的观点仍然成立,因为 CPU 和 DMA 正在访问地址 x 和 y 的内存/缓存。如果 x 和 y 包含的地址在同一缓存行中,那么在这种情况下,清理操作将覆盖 DMA 所做的更改。以上是关于ARM DMA Controller PL330 使用经验分享的主要内容,如果未能解决你的问题,请参考以下文章