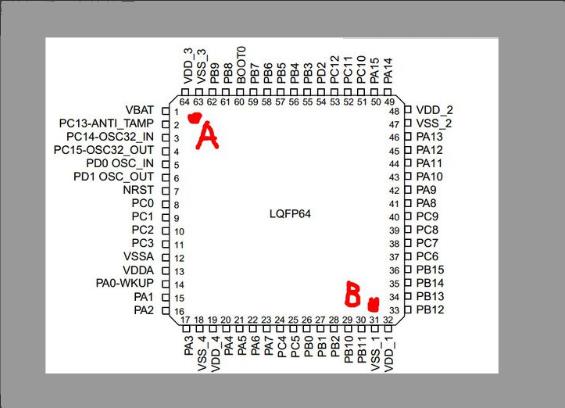

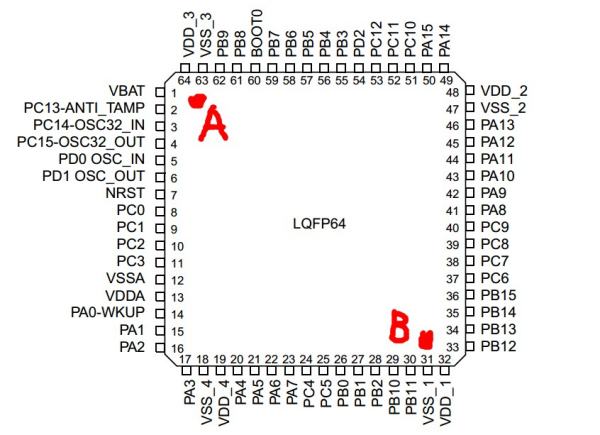

stm32 那个管脚是1管脚,A还是B

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了stm32 那个管脚是1管脚,A还是B相关的知识,希望对你有一定的参考价值。

A。

一般这种4面有脚的芯片,若分不清楚的,可以正对丝印,下面一排引脚的左边第一个为1号,上图A、B对应数据手册中的位置下如图:

扩展资料:

注意事项

1、上拉指的是IO口在悬空时为高电平,下拉为低电平,浮空和开漏随IO变化,推挽则具有比较好的驱动能力。

2、推挽输出:单片机引脚可以直接输出高电平电压,高低电平都可以输出,既可以向负载灌电流,又可以从负载吸收电流,带负载能力比较强。

3、开漏输出:不输出电压,低电平接地,高电平不接地。如果外接上拉电阻,则在输出高电平时,电压会被拉到上拉电阻的电源电源。

4、浮空输入:输入什么信号就是什么信号。

5、stm32管脚配置

GPIOMode_TypeDef GPIO mode定义及偏移地址

GPIO_Mode_AIN = 0x0, //模拟输入

GPIO_Mode_IN_FLOATING = 0x04, //悬空输入

GPIO_Mode_IPD = 0x28, //下拉输入

GPIO_Mode_IPU = 0x48, //上拉输入

GPIO_Mode_Out_OD = 0x14, //开漏输出

GPIO_Mode_Out_PP = 0x10, //推挽输出

GPIO_Mode_AF_OD = 0x1C, //开漏复用

GPIO_Mode_AF_PP = 0x18 //推挽复用

参考技术AA。一般这种4面有脚的芯片,若分不清楚的,可以正对丝印,下面一排引脚的左边第一个为1号,上图A、B对应数据手册中的位置见下图

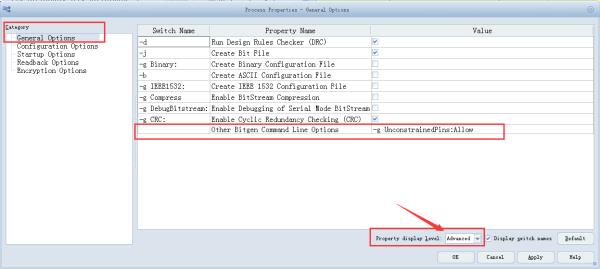

Xilinx 的ISE中怎样对一部分管脚不进行锁定,不进行约束

由于在.UCF文件中有几个管脚未进行LOC,在生成.bit文件时总是出现Bitgen 342的error。麻烦问一下ISE中怎样对一部分管脚不进行锁定,也就是不进行约束。

补充:1. 可能由于软件问题,在PlanAhead中未发现Project Manager box。

2. -g UnconstrainedPins:Allow 这个switch找不到

右键 Generate Programming这一项,选择在右下角Property display Level一栏,

选择Advanced,然后如下图填上-g UnconstrainedPins:Allow 就可以了。

谢谢,就是这个答案。赞!

本回答被提问者和网友采纳 参考技术B 这个是不行的,追问完全可以啊,只不过需要在ise中设置一下,可以跑过。但是烧到板子上可能有伤害而已

参考技术C 随便找个不用的管脚锁定一下啊。追问嗯可以

以上是关于stm32 那个管脚是1管脚,A还是B的主要内容,如果未能解决你的问题,请参考以下文章