8080并口时序

Posted powerforme

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了8080并口时序相关的知识,希望对你有一定的参考价值。

介绍

8080并口协议有多种类型,主要通过bus_interface的线数进行区分,主要有8-bit、16-bit、9-bit、18-bit等四种模式。

第一类:

MCU-Interface Mode Register/Content GRAM

8080 8-bit mode D[7:0] D[7:0],WRX,RDX,CSX,D/CX(RS)

8080 16-bit mode D[7:0] D[15:0],WRX,RDX,CSX,D/CX(RS)

8080 9-bit mode D[7:0] D[8:0],WRX,RDX,CSX,D/CX (RS)

8080 18-bit mode D[7:0] D[17:0],WRX,RDX,CSX,D/CX(RS)

第二类:

MCU-Interface Mode Register/Content GRAM

8080 16-bit mode D[8:1] D[7:0],WRX,RDX,CSX,D/CX(RS)

8080 8-bit mode D[17:10] D[15:0],WRX,RDX,CSX,D/CX(RS)

8080 18-bit mode D[8:1] D[8:0],WRX,RDX,CSX,D/CX (RS)

8080 9-bit mode D[17:10] D[17:0],WRX,RDX,CSX,D/CX(RS)

端口含义

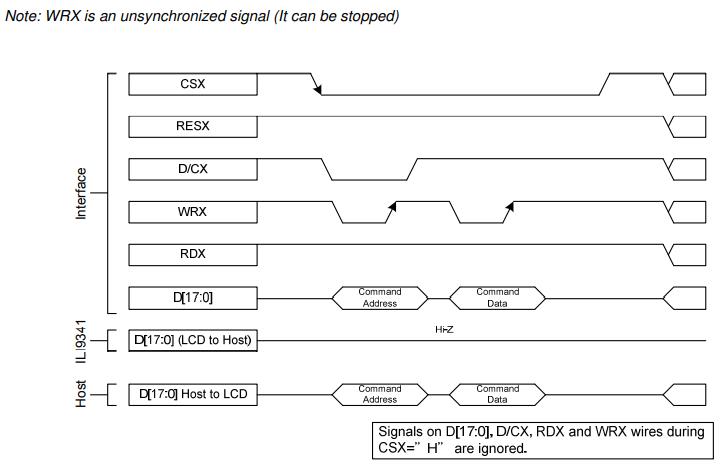

CSX 片选信号,低电平有效,在高电平期间其他信号线均无效。

D/CX(RS) 命令数据线,当发送为命令时为0,发送为数据时为1。

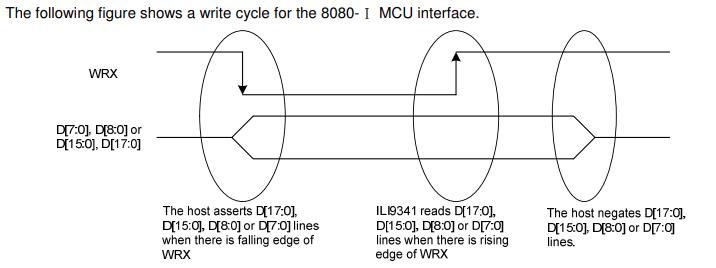

WRX 写信号线;在写模式下,在低电平期间完成数据的准备工作,在上升沿捕捉数据;在读模式下始终保持高电平。

RDX 读信号线;在读模式下,在低电平期间进行数据的准备工作,在上升沿捕捉数据;在写模式下始终保持高电平。

D[x:0] 信号线;

写模式时序图:

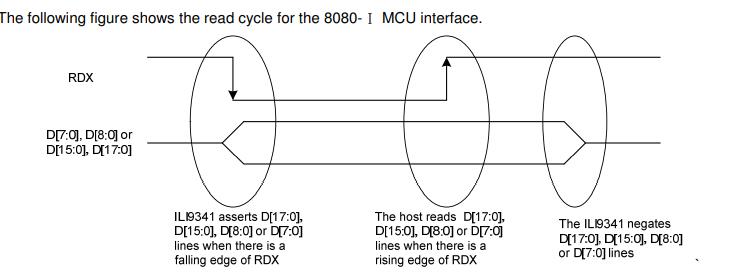

读模式时序图:

需要注意:从图中可以看出读数据时,需要两个RDX的上升沿才能读出正确数据,第一个RDX上升沿的数据为无效数据,第二个RDX上升沿才为有效值。

第8讲 异步并行接口时序设计

① 学习异步并行接口的读写时序操作,掌握异步并口的时序描述方法;

② 复习inout双向端口的Verilog HDL描述方法及仿真方法;

③ 掌握收/发双向通讯方式的仿真方法。

(1)异步并口的应用及优缺点

并口的最大缺陷:拥有多路数据总线和地址总线,因为走线长度、用线材料存在差异,所以,当信号的频率提高后,会存在线路延迟不同的现象,从而造成各路信号到达目标端口的时间不同,导致信号出现大量的毛刺和不稳定。

其次,并口占用的I/O口多,且难以满足高频信号的传输要求。

因此,当信号频率很高的时候,往往从用的是串行传输的方式,而当频率较低时(只有数十兆赫兹时),可采用并口的传输方式。

(2)写操作的时序图

图1 写操作时序图

异步并口的异步是指主机不输出时钟信号给从机用作它们之间的通讯,异步并口的并口是指主-从机之间的数据线(此例为16根)和地址线有多根(此例为8根),且主-从机之间的数据交互是并行的。

如图1所示,cs_n为异步并口的片选信号,低电平有效;rd_n为读使能信号,低电平有效;we_n为写使能信号,低电平有效;data为数据总线,位宽为16bit;addr为地址总线,位宽为8bit。

如图1所示,当cs_n为低电平时,FPGA被主机片选中,当FPGA检测到we_n信号被拉低时,即进入到异步并口的写状态,数据通过data数据总线送入FPGA,并按照addr地址总线上的地址值将数据存放到指定存储空间上(如:RAM、FIFO等)。

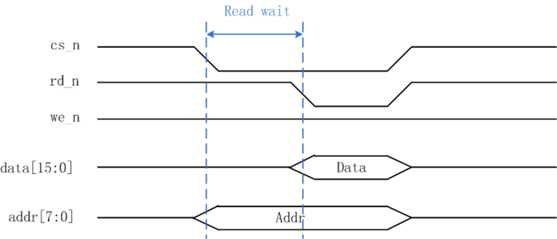

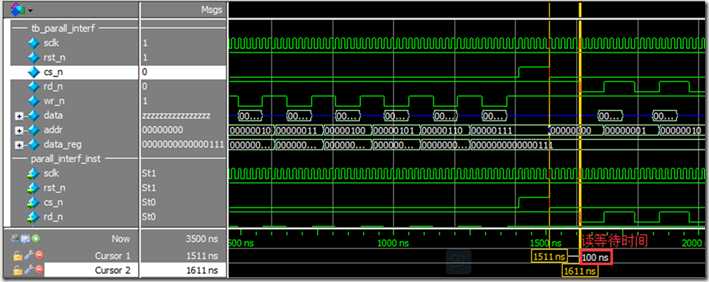

(3)读操作的时序图

图2 读操作时序图

图2为异步并口的读操作时序,当cs_n为低电平时,FPGA被主机片选中,当FPGA检测到rd_n信号被拉低时,即进入到异步并口的读状态,FPGA按照addr地址总线上的地址值从指定存储位置上将数据读出并送到data数据总线上,以供主机设备读走。

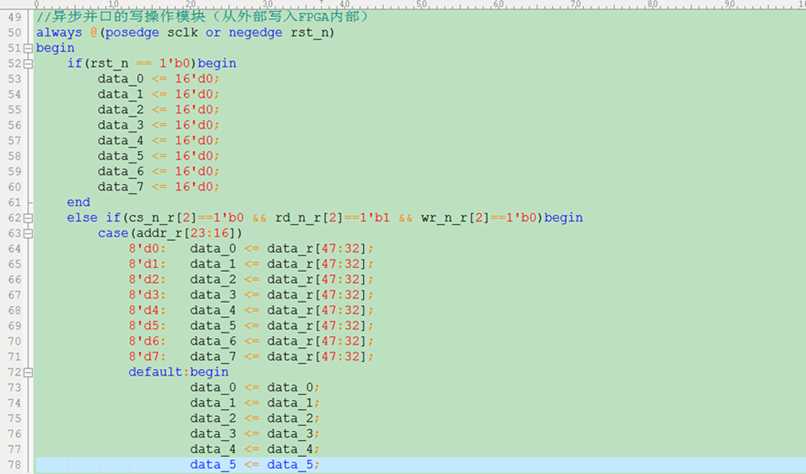

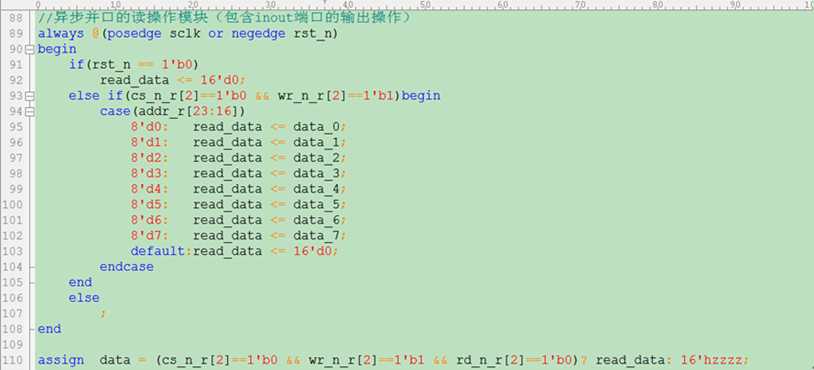

【代码实现】

异步并口虽然没有同步时钟信号,但是,也不能全用组合逻辑的方式来描述,因为时序逻辑具有更高的稳定性,能给数据采集留以充分的建立时间和保持时间,从而使得读/写操作能在数据稳定后稳定进行。而组合逻辑电路的输出是随输入信号的变化而实时变化的,若主-从机之间的信号稍不稳定,即会导致读/写操作的错误。

因此,本例依然采用时序逻辑电路为主的描述方式,将cs_n、rd_n、wr_n等输入信号采到sclk系统时钟域来,然后在系统时钟sclk的控制下有序地工作。当然,像这种异步时钟域会存在亚稳态的现象,因此,为了降低亚稳态发生的概率,我们采用“打节拍”的方式稳定输入的信号,统一用sclk系统时钟给输入信号多打两拍(延迟两个时钟周期)。

综合以上分析可知,本例要设计的代码应包含以下三个部分:

(1) 用系统时钟sclk给输入信号多打两拍,稳定输入信号;

(2) 异步并口的写操作模块(从外部写入FPGA内部);

(3) 异步并口的读操作模块(包含inout端口的输出操作)。

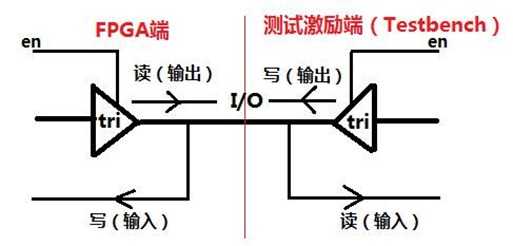

【关于inout双向端口的描述与测试】

图3 inout双向端口测试模型

如图3所示,展示了本例所采用的测试模型,对于FPGA芯片来说,异步并口的读操作就是数据输出,写操作就是数据的输入;而对于测试激励端来说,异步并口的写操作就是数据输出,读操作就是数据的输入。

因此,应将FPGA端的程序设计如下:

inout tri [15:0] data, //双向数据总线

assign data = (cs_n_r[2]==1‘b0 && wr_n_r[2]==1‘b1 && rd_n_r[2]==1‘b0)? read_data: 16‘hzzzz;//读操作输出数据

对于写操作输入数据,则直接将data数据总线上的数据送入给FPGA的寄存器。

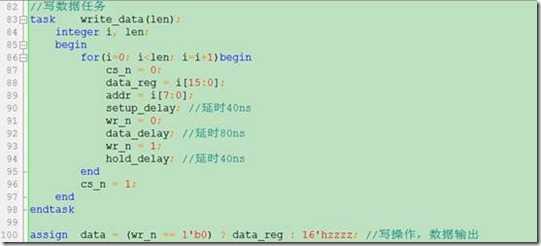

而应将测试激励端的程序设计如下:

tri [15:0] data;

reg [15:0] data_reg;

assign data = (wr_n==1‘b0) ? data_reg : 16‘hzzzz;//写操作输出数据

对于读操作输入数据,则直接读取data数据总线上的数据即可。

【Testbench搭建】

(1)声明建立时间、保持时间、数据采样时间以及读等待时间等延时任务,以便模拟异步并口的读写时序;

(2)读数据任务

(3)写数据任务

(4)仿真流程控制

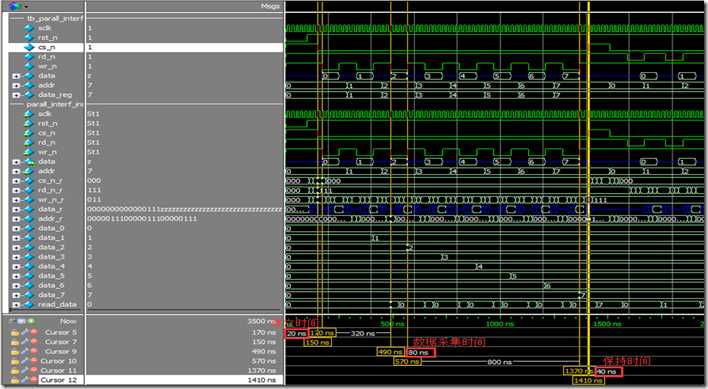

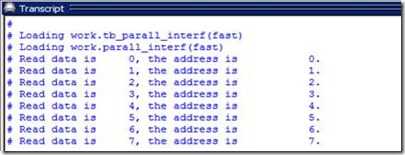

【实验结果】

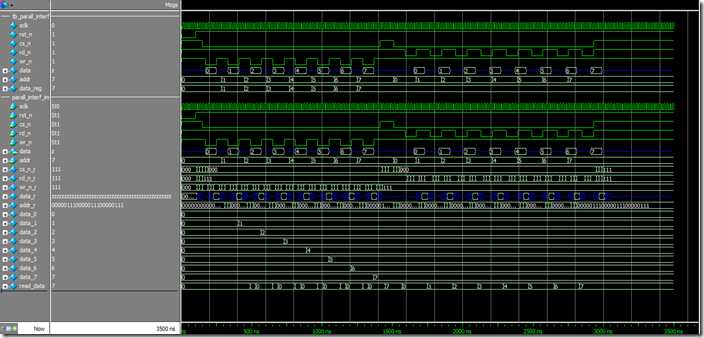

图4 打节拍延时60ns

图5 建立时间、数据采集时间、保持时间

图6 读等待时间

图7 Transcript窗口信息

图8 仿真波形整体图

以上是关于8080并口时序的主要内容,如果未能解决你的问题,请参考以下文章