LDO工作区网上说明比较混淆,以下为准

Posted icmaxwell

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了LDO工作区网上说明比较混淆,以下为准相关的知识,希望对你有一定的参考价值。

电源硬件设计----线性调压器与LDO

1 线性调压器与LDO的介绍

1.1 线性调压器的工作原理

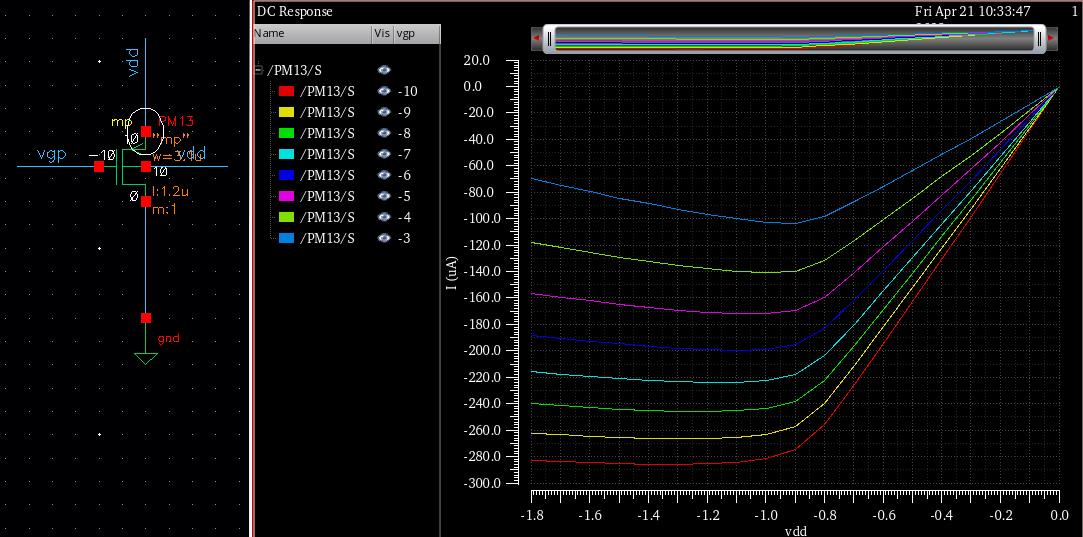

输入功率与输出功率的差值作为损耗耗散在三极管器件上,如图所示:

三极管工作在线性区,控制电压降VCE达到电功率的调节

1.2 线性调压器的优缺点

优点:

- 非常

少的外部元器件 - 很

高的电源抑制比(PSRR) - 较

低的成本 低噪声输出- 很

小的静态电流

缺点: 压降比较大导致效率较低

1.3 线性调压器与LDO的区别

- LDO全称为Low Drop Out

- Drop out voltage(Vdo)是指为了维持稳压所需要的

最小压降 - “LDO”定义没有特定的数值表征

- 一般线性调压器的Drop out voltage

电压在0.5V以下,可称之为LDO

2 线性调压器与LDO的拓扑结构

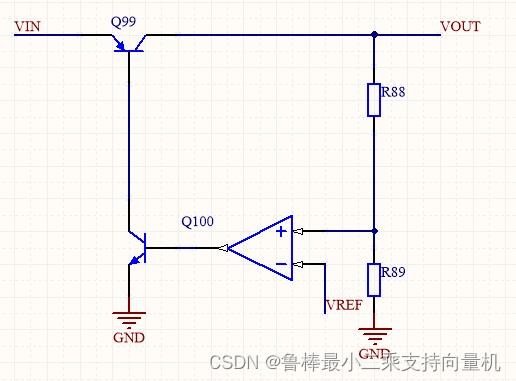

2.1 NPN型线性稳压器

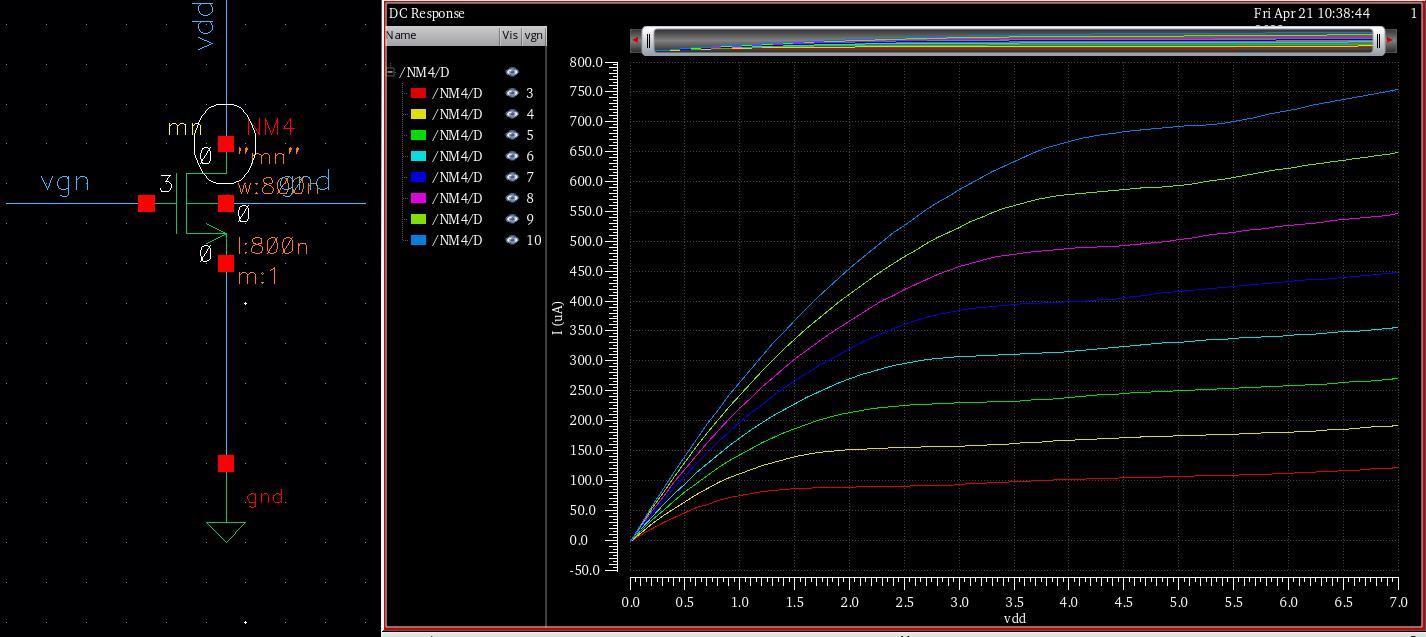

NPN型线性稳压器如图所示:

特点:

- 高性能

- 非常低的工作电流

- 对输出电容几乎没有要求

- 较高的drop-out电压(1.5-2.5V)

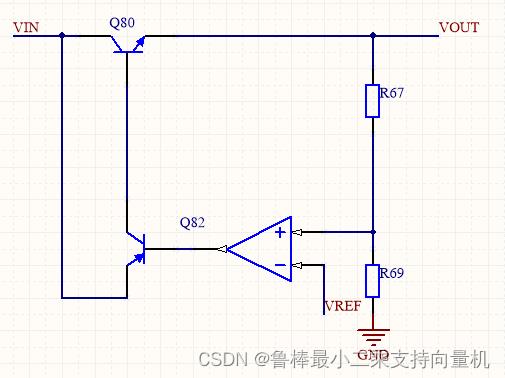

2.2 PNP-LDO线性稳压器

PNP-LDO线性稳压器如图所示:

特点:

- 高性能

- 较低的drop-out电压(<1V)

- 较高的静态电流

- 工作电流随着负载增加而增加

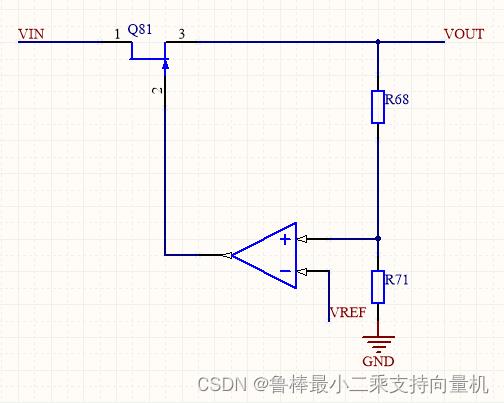

2.3 Quasi-LDO线性稳压器

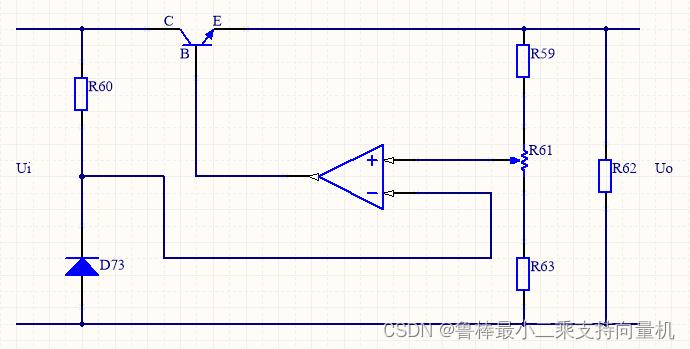

Quasi-LDO线性稳压器如图所示:

特点:

- 对输入输出电容容量要求较低

- drop-out电压比传统NPN线性稳压器低

- 具有比PNP-LDO线性稳压器更好的负载调整率

2.4 CMOS-LDO线性稳压器

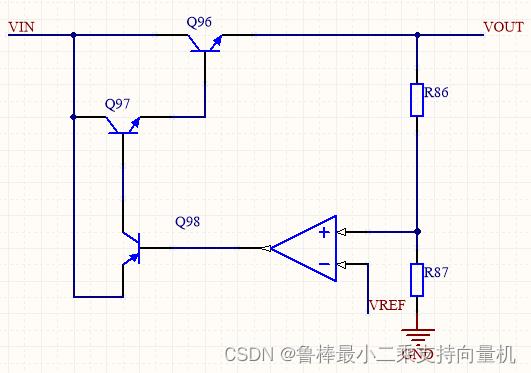

CMOS-LDO线性稳压器如图所示:

特点:

- 非常低的drop-out电压

- 非常低的静态电流与工作电流

- 工作电流与负载无关

3 线性调压器与LDO的参数

3.1 关键的DC参数

- 精度(Accuracy): 实际输出电压值与理论计算输出电压值之间多接近的范围

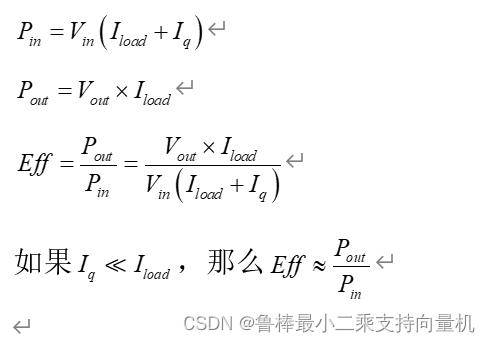

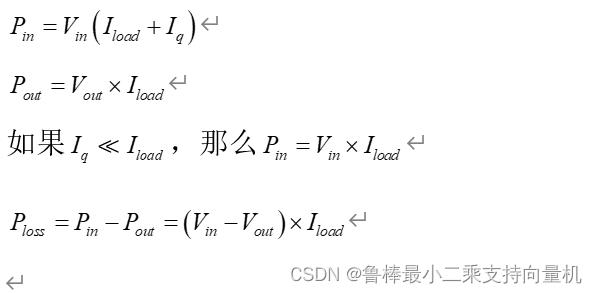

- 效率(Efficiency): LDO的效率相对于开关电源来说是很低的,需要更大的散热器来帮助耗散热能,该描述并不完全正确,LDO的效率与工作条件相关。效率计算公式如下:

- 压降(Drop-out voltage): 1、该指标为了维持输出电压满足一定精度要求所需的最低输入电压与输出电压的差值;2、该电压只有在输入电压逐渐接近输出电压的时候才体现出来;3、如果Vin<Vout+Vdo,LDO将不能再有效调节输出电压

- 静态电流(Quiescent current): 指稳压器在无负载情况所需要维持自身正常运作的电流,包含内部控制电路工作电流以及双极型晶体管所需要的偏置电流

- 热相关(Thermal)

3.2 关键的AC参数

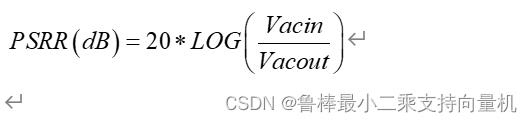

- 电源抑制比(PSRR): 1、PSRR全称Power Supply Rejection Ratio;2、表征线性稳压器对于

输入电压纹波噪声的抑制能力;3、PSRR受频率、电压、负载、外部器件、PCB布局等因素影响。PSRR计算公式如下:

- 噪声(Noise): 1、规定带宽内的总积分噪声,用uVrms表示;2、噪声谱密度曲线,噪声与频率的关系;3、通过加入

低通滤波可以有效减少输出噪声

4 LDO的设计与选择

4.1 LDO的设计选择

- 第一步: 基于输入电压与输出电压范围以及负载范围来确定合适Vdo的LDO方案

- 第二步: 基于系统对性能的具体要求选择1、

根据噪声的要求,选择PSRR,噪声等相关指标;2、是否有待机功耗,选择合适静态电流,工作电流等指标;3、是否有输出电容类型的要求,如全陶瓷电容等选择合适拓扑结构 - 一定要确定LDO封装是否满足散热要求

4.2 Drop-out电压影响

- 需要尽量避免设计使得LDO进入Drop-out影响区域

- 如果过选择MOS型的LDO,需要考虑RDSON的温度特性对Drop-out的影响

- 受Drop-out电压影响的参数: 当LDO进入Drop-out影响区域时1、PSRR会减小到几乎为0;2、动态性能变差;3、线性调整率也会超出规格;4、静态电流会增加;5、输出效率会提升

4.3 输出电容影响

对于应用中经常遇到的LDO振荡问题,几乎都是由输出电容引起的,以下为常见的几种导致振荡的原因:

- ESR太大: 1、比较差的Tantalum电容有较高的ESR;2、通常电解电容在低温的时候也会有比较大的ESR

- ESR太小: 1、很多表贴的陶瓷电容都有非常小的ESR;2、Tantalum,OSCON,SP,POSCAP,film等电容也具有很小的ESR

- 0.001uF到0.1uF的陶瓷Bypass电容往往也容易导致不稳定

高ESR的影响:

- 高ESR导致零点移动到较低频率

- 导致环路带宽提升,使得PPWR极点对0dB处的相应具有更大的影响从而导致环路的不稳定性

低ESR的影响:

- 低ESR使得零点移往高频处

- 移往高频处的零点无法在0dB以上有效抵消功率极点与内部补偿极点的影响,从而导致环路的不稳定

4.4 热设计的参数

LDO热设计所需要了解的主要参数:

-

LDO的损耗: 损耗计算公式如下:

-

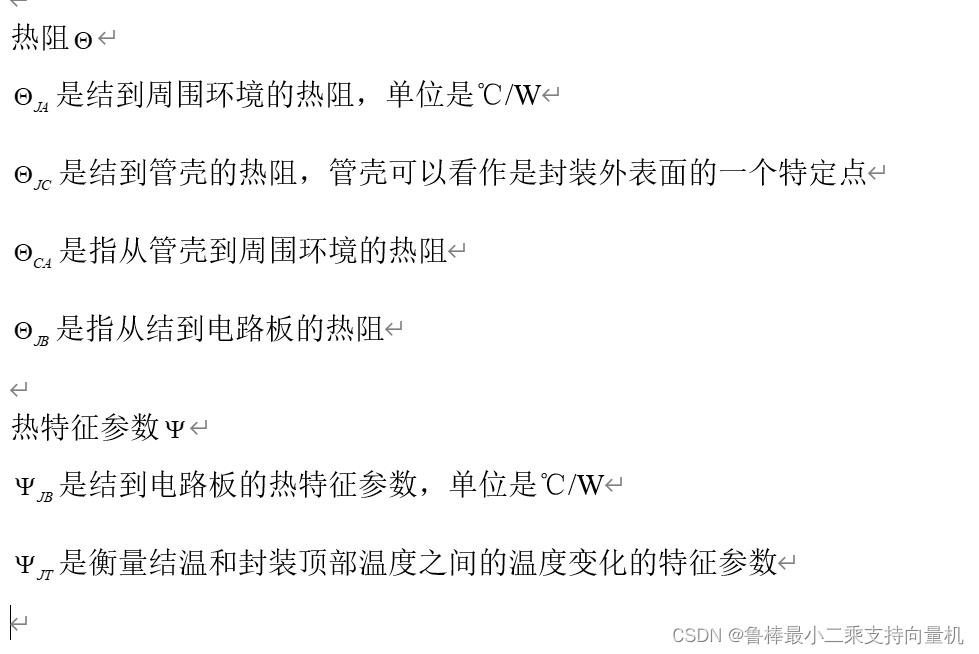

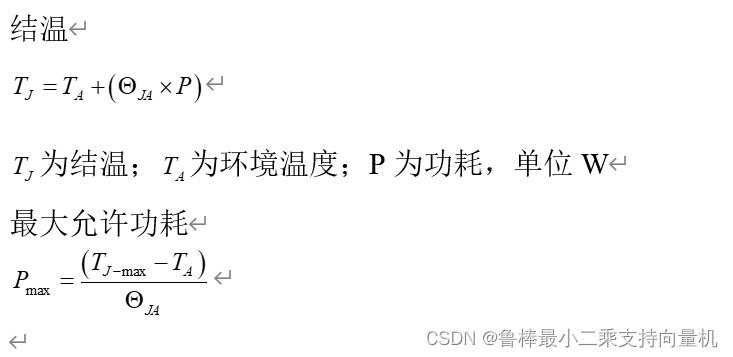

LDO的封装的不同热阻数据: 热阻的两种表达方式1、热阻Theta;2、热特征参数Psi。详细解释如下所示:

-

所处的最高环境温度

-

LDO的最大推荐工作结温,LDO热计算公式如下:

5 LDO测试注意事项

5.1 LDO环路测试

LDO环路测试难点:

- LDO环路具有非常高的增益

- 需要高精度的设备做测试

- 低频区域几乎无法测试准确的增益

LDO环路测试的方法: 1、变压器;2、高精度信号注入器。为了确保测试准确性,需要两种方式交叉验证

5.2 LDO PSRR测试

PSRR测试可以把LDO看作一个滤波器

PSRR测试准备:

- 需要一个受控纹波源

- 需要一个合适的缓冲器电路板或放大器源

PSRR测试注意事项: 选择合适的注入纹波

- 不能使LDO进入Vdo模式,否则将会使得LDO工作在失控模式

- 注入纹波不能太小,否则测量精度将变低,

一般在200-300mV - 输入电容会衰减高频纹波,需要尽可能的

减小输入电容

希望本文对大家有帮助,上文若有不妥之处,欢迎指正

分享决定高度,学习拉开差距

以上是关于LDO工作区网上说明比较混淆,以下为准的主要内容,如果未能解决你的问题,请参考以下文章