NPU的算法,架构及优势分析

Posted 吴建明

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了NPU的算法,架构及优势分析相关的知识,希望对你有一定的参考价值。

NPU的算法,架构及优势分析

什么是NPU?NPU都有哪些优势?

现在刚好是神经网络和机器学习处理需求爆发的初期。传统的CPU/GPU也可以做类似的任务,但是针对神经网络特殊优化过的NPU单元,性能会比CPU/GPU高得多。渐渐的,类似的神经网络任务也会由专门的NPU单元来完成。

NPU(嵌入式神经网络处理器/网络处理器)是一种专门应用于网络应用数据包的处理器,采用“数据驱动并行计算”的架构,特别擅长处理视频、图像类的海量多媒体数据。

NPU也是集成电路的一种,但区别于特殊用途集成电路(ASIC)的单一功能,网络处理更加复杂、更加灵活,一般可以利用软件或硬件依照网络运算的特性特别编程从而实现网络的特殊用途,在一块芯片上实现许多不同功能,以应用于多种不同的网络设备及产品。

NPU的亮点在于能够运行多个并行线程 —— NPU通过一些特殊的硬件级优化,比如为一些真正不同的处理核提供一些容易访问的缓存系统,将其提升到另一个层次。这些高容量内核比通常的“常规”处理器更简单,因为它们不需要执行多种类型的任务。这一整套的“优化”使得NPU更加高效,这就是为什么这么多的研发会投入到ASIC中的原因。

NPU处理器模块

NPU处理器专门为物联网人工智能而设计,用于加速神经网络的运算,解决传统芯片在神经网络运算时效率低下的问题。NPU处理器包括了乘加、激活函数、二维数据运算、解压缩等模块。

乘加模块用于计算矩阵乘加、卷积、点乘等功能,NPU内部有64个MAC,SNPU有32个。

激活函数模块采用最高12阶参数拟合的方式实现神经网络中的激活函数,NPU内部有6个MAC,SNPU有3个。

二维数据运算模块用于实现对一个平面的运算,如降采样、平面数据拷贝等,NPU内部有1个MAC,SNPU有1个。

解压缩模块用于对权重数据的解压。为了解决物联网设备中内存带宽小的特点,在NPU编译器中会对神经网络中的权重进行压缩,在几乎不影响精度的情况下,可以实现6-10倍的压缩效果。

NPU:手机AI的核心载体

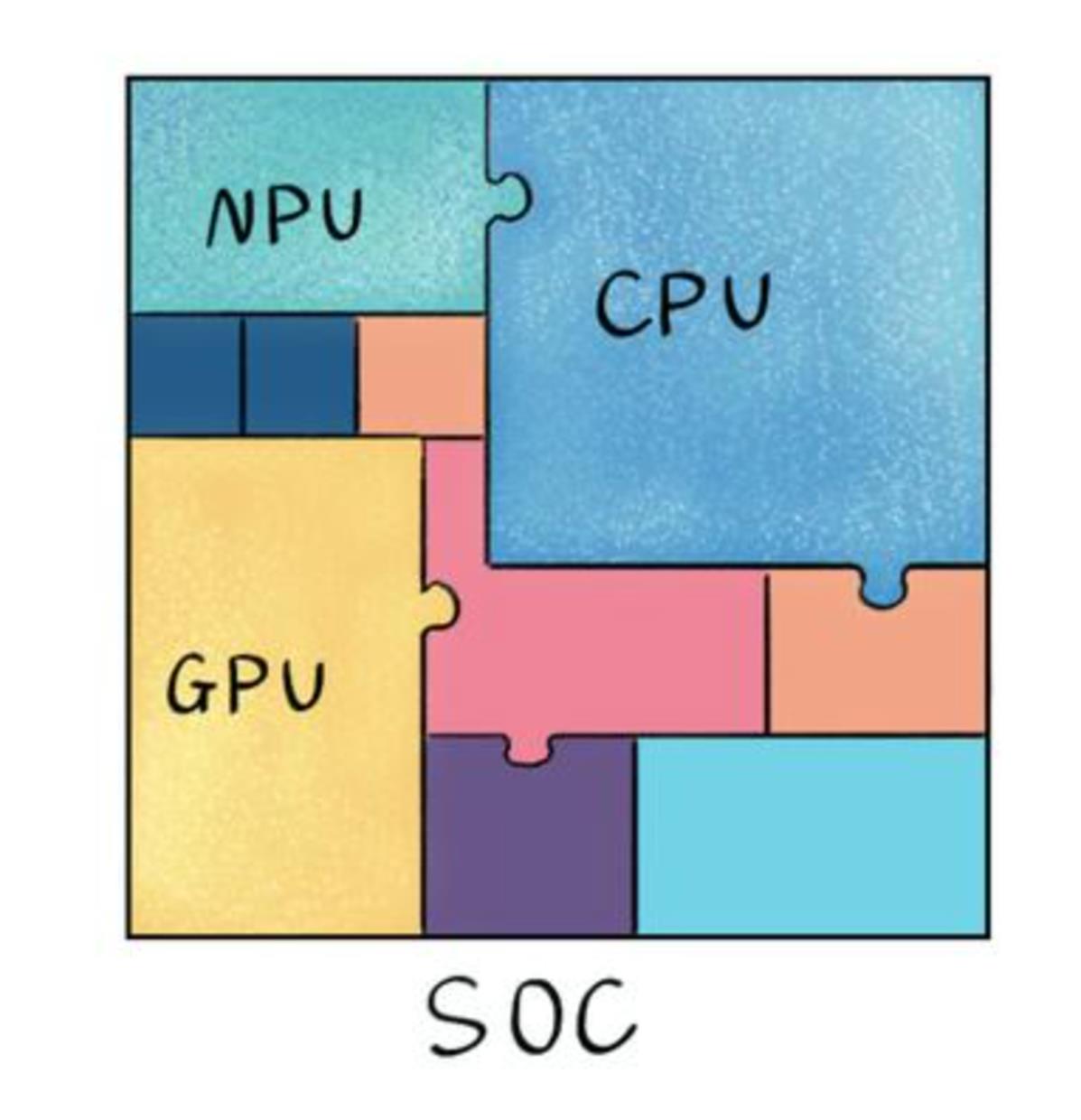

大家都知道,手机正常运行离不开SoC芯片,SoC只有指甲盖大小,却“五脏俱全”,其集成的各个模块共同支撑手机功能实现,如CPU负责手机应用流畅切换、GPU支持游戏画面快速加载,而NPU就专门负责实现AI运算和AI应用的实现。

手机上带AI功能这事还得从华为说起,华为是第一个将NPU(neural-network processing units嵌入式神经网络处理器)用于手机上,更是第一个将NPU集成到手机CPU上的公司。

2017年,华为推出自研架构NPU,相比传统标量、矢量运算模式,华为自研架构NPU采用3D Cube针对矩阵运算做加速,因此,单位时间计算的数据量更大,单位功耗下的AI算力也更强,相对传统的CPU和GPU实现数量级提升,实现更优能效。

华为采用外挂的方式最早将寒武纪的NPU用于Mate10,一年之后,华为将寒武纪NPU的IP集成到了980上,又一年之后,华为抛弃了寒武纪在990上采用了自研的达芬奇NPU。Galaxy中的NPU也是内置于移动处理器中,以利用先进的神经网络并为Galaxy S20/S20 +/S20 Ultra和Z Flip提供更高水平的视觉智能。NPU为场景优化器提供动力,增强了识别照片中内容的能力,并提示相机将其调整为适合主体的理想设置。现在,它也比以前的Galaxy模型更准确。它还使前置摄像头能够模糊自拍照的背景并创建散景效果。不仅如此,NPU还可以帮助设备上的AI Bixby Vision。

NPU与GPU的关系

NPU工作原理是在电路层模拟人类神经元和突触,并且用深度学习指令集直接处理大规模的神经元和突触,一条指令完成一组神经元的处理。相比于CPU和GPU,NPU通过突触权重实现存储和计算一体化,从而提高运行效率。

NPU是模仿生物神经网络而构建的,CPU、GPU处理器需要用数千条指令完成的神经元处理,NPU只要一条或几条就能完成,因此在深度学习的处理效率方面优势明显。实验结果显示,同等功耗下NPU的性能是GPU的118倍。

各芯片架构特点总结

CPU —— 70%晶体管用来构建Cache,还有一部分控制单元,计算单元少,适合逻辑控制运算。

GPU —— 晶体管大部分构建计算单元,运算复杂度低,适合大规模并行计算。主要应用于大数据、后台服务器、图像处理。

NPU —— 在电路层模拟神经元,通过突触权重实现存储和计算一体化,一条指令完成一组神经元的处理,提高运行效率。主要应用于通信领域、大数据、图像处理。

FPGA —— 可编程逻辑,计算效率高,更接近底层IO,通过冗余晶体管和连线实现逻辑可编辑。本质上是无指令、无需共享内存,计算效率比CPU、GPU高。主要应用于智能手机、便携式移动设备、汽车。

CPU/GPU/NPU/FPGA各自的特点

CPU作为最通用的部分,协同其他处理器完成着不同的任务。GPU适合深度学习中后台服务器大量数据训练、矩阵卷积运算。NPU、FPGA在性能、面积、功耗等方面有较大优势,能更好的加速神经网络计算。而FPGA的特点在于开发使用硬件描述语言,开发门槛相对GPU、NPU高。

NPU的实际应用场景

拍照时通过NPU实现AI场景识别,并利用NPU运算修图

NPU判断光源和暗光细节合成超级夜景

通过NPU实现语音助手的运行

NPU配合GPU Turbo预判下一帧实现提前渲染提高游戏流畅度

NPU预判触控提高跟手度和灵敏度

NPU判断前台后台网速需求差异配合实现Link Turbo

NPU判断游戏渲染负载智能调整分辨率

把降低游戏时AI的运算负载交给NPU以省电

NPU实现CPU和GPU的动态调度

NPU辅助大数据广告推送

通过NPU实现输入法AI智能联想词的功能

相关信息

APU:Accelerated Processing Unit, 加速处理器,AMD公司推出加速图像处理芯片产品。

BPU:Brain Processing Unit, 地平线公司主导的嵌入式处理器架构。

CPU:Central Processing Unit 中央处理器, 目前PC core的主流产品。

DPU:Dataflow Processing Unit 数据流处理器,Wave Computing 公司提出的AI架构。

FPU:Floating Processing Unit 浮点计算单元,通用处理器中的浮点运算模块。

GPU:Graphics Processing Unit 图形处理器,采用多线程SIMD架构,为图形处理而生。

HPU:Holographics Processing Unit 全息图像处理器, 微软出品的全息计算芯片与设备。

IPU:Intelligence Processing Unit,Deep Mind投资的Graphcore公司出品的AI处理器产品。

MPU/MCU:Microprocessor/Micro controller Unit,微处理器/微控制器,一般用于低计算应用的RISC计算机体系架构产品,如ARM-M系列处理器。

NPU:Neural Network Processing Unit,神经网络处理器,是基于神经网络算法与加速的新型处理器总称,如中科院计算所/寒武纪公司出品的diannao系列。

RPU:Radio Processing Unit 无线电处理器,Imagination Technologies 公司推出的集合集Wifi/蓝牙/FM/处理器为单片的处理器。

TPU:Tensor Processing Unit 张量处理器,Google 公司推出的加速人工智能算法的专用处理器。目前一代TPU面向Inference,二代面向训练。

VPU:Vector Processing Unit 矢量处理器,Intel收购的Movidius公司推出的图像处理与人工智能的专用芯片的加速计算核心。

WPU:Wearable Processing Unit 可穿戴处理器,Ineda Systems公司推出的可穿戴片上系统产品,包含GPU/MIPS CPU等IP。

XPU:百度与Xilinx公司在2017年Hotchips大会上发布的FPGA智能云加速,含256核。

ZPU:Zylin Processing Unit,由挪威Zylin公司推出的一款32位开源处理器。

阿里达摩院:含光NPU的算法与架构

阿里巴巴达摩院高级研究员金榕以及含光800设计者、平头哥研究员焦阳在2019杭州云栖大会上,深入介绍了含光NPU的算法与架构。以下是金榕及焦阳的分享内容文字整理,经编辑。

金榕:首先,深度学习在所有领域都发生了质的变化,一个很明显的例子是语音识别从最初的需要依赖用户语音到今天基本上随便做一个语音输入都可以很成功,视觉是另外一个非常好的例子,今天深度学习可以从过去只能几百类或者上千类的识别到轻松几百万类甚至几千万类的识别,并且有很高的精度。

同时,今天看见在市面上有很多视觉识别公司,利用了深度学习技术,把视觉技术真正地应用在各种产品上,比如人脸识别就是非常成功的例子,非常值得一提的就是阿里城市大脑,利用视觉技术自动监控交通和安全的行为,使得视觉分析不再依靠原先的特殊设备,从而能够广泛地应用在城市的各个角落上。

自然语言和翻译严格意义上是深度学习较晚进入的领域,但是今天深度学习对这两个领域产生了质的变化。如果大家有幸用过以前的谷歌翻译和今天的谷歌翻译,可以看到非常本质的区别,其中最主要的原因就是由深度学习带来的。

简单的科普,要想把深度学习技术实用化,至少需要考虑三件重要的事情:首先要定义要学习的函数,这就是今天神经网络做的事情;第二是需要很多数据,也就是大数据;第三就是优化的问题,需要在定义的函数空间,利用数据找到一个最合适的解,从而最佳适配数据。

今天,深度学习真正实用要至少克服两大挑战(从计算的角度):第一是如何让复杂的模型更高效率和高效能运行;第二是模型需要吞吐大量数据,如何在大量数据量呑吐的情况下还能保持很好的实时性。例如,就深度语言模型而言,今天非常流行的BERT language model,几乎成为所有自然语言处理核心的模型,而今天实际上用的Bert模型还是平均的Bert模型,但它至少有几亿的参数,如果采用大型Bert的话,至少参数要翻一个数量级。

另外一个跟自然语言处理有关的就是机器翻译。今天机器翻译一般都是用Deep Transformer的结构,这是一个非常深的至少60多层的结构,它为了更好捕捉上下文信息,需要所谓的Multi-head Attention机制,这些都让模型极其复杂,使得运行模型的计算成本非常高。

而在语音识别中,最近几年一个大趋势叫做End2End语音识别模型,与过去的区别是什么呢?早期的语音识别模型都是先识别发音,形成声音模型(Acoustic Model),然后再把发音转变成句子(Language Model),但今天由于计算能力的大幅度增强而只需要一个流程即可,从语音输入直接到整个句子输出形成End2End模型。一般来讲,一个End2End的模型至少是几十个G大小。

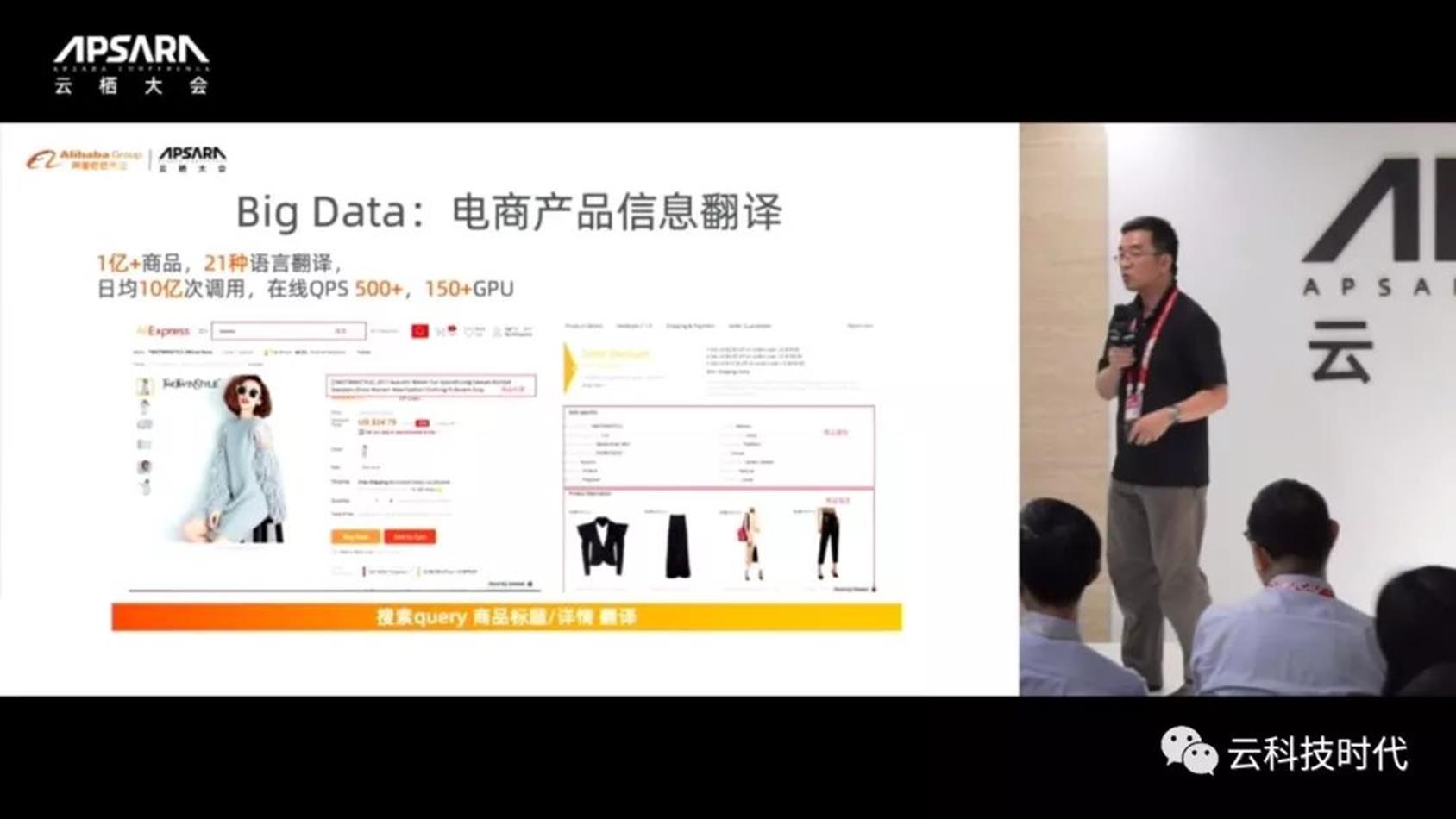

说完了模型的大小,再提一下数据的问题。今天阿里有很多场景都需要用AI技术来支撑整个业务,而今天的数据量也是过去无法比拟的。以翻译为例,翻译在今天阿里很多跨界业务中都起着核心作用,包括阿里很多海外业务都需要翻译,就是把中国的商品翻译成相应国家的语言。每天大概需要翻译一亿+的商品,通常需要21种语言的翻译,每天翻译的调用量在10亿的级别,是非常大的使用量。

诸位也许有机会用到拍立淘,这是一个非常简单的产品,对任何有兴趣的物体拍一张照片,系统会自动识别这个商品并链接到商品页面,拍立淘大概每天有2000多万的用户、每天上传图片至少是4亿到5亿,需要一个极大的计算引擎去处理这么大量的图片,而且这还是在线的用量,离线处理量更大、约在百亿级别的水平。

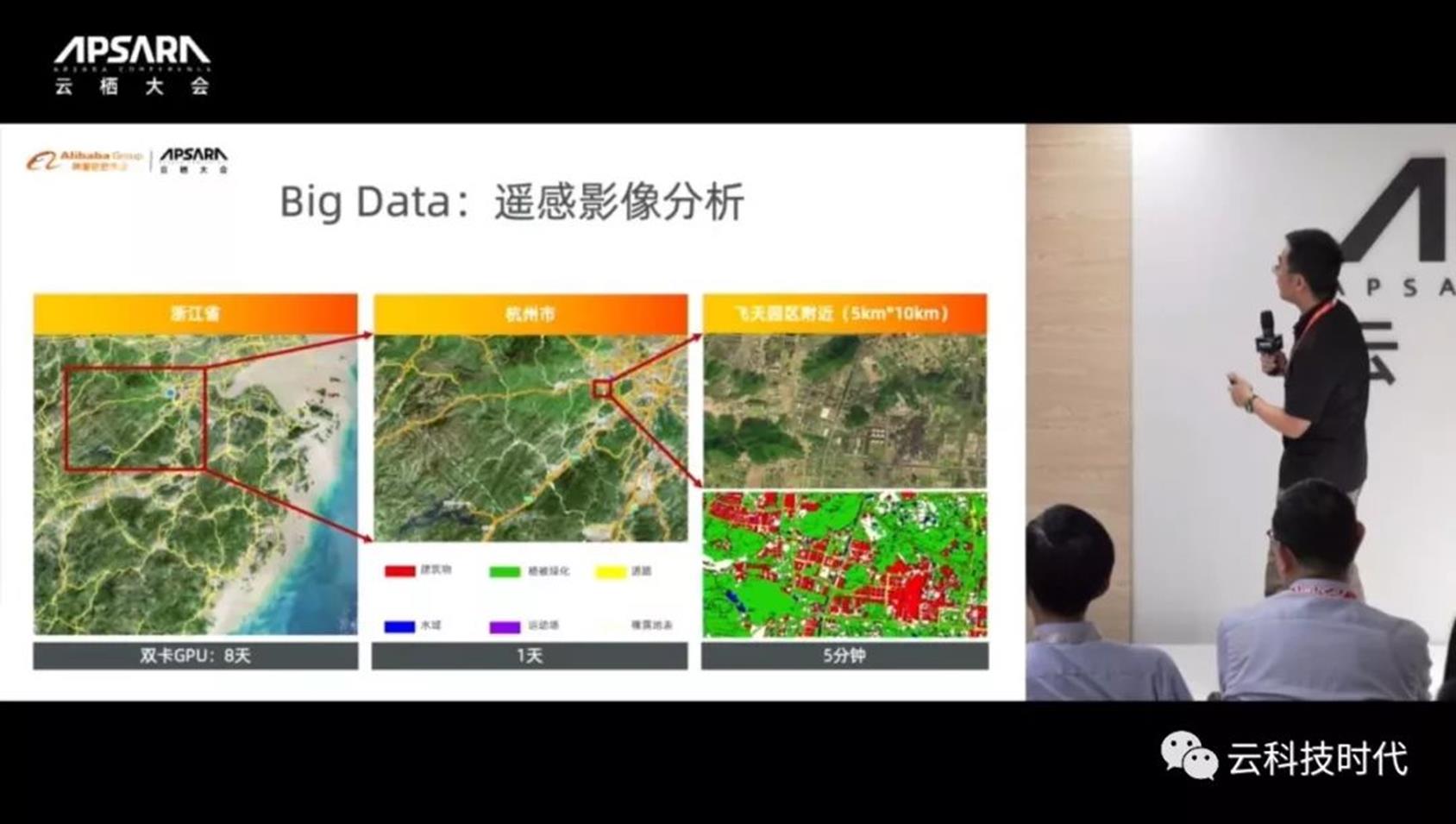

另外一个值得一提的数据就是遥感影像数据,例如进行某地遥感数据分析,包括路网信息、建筑信息、地貌信息等等,浙江一个省可能就需要2个GPU、8天的时间才能把所有需要处理和识别的任务处理好,即使是一个小园区也需要好几分钟才能把其中的建筑、地貌以及地图识别出来。所以,可以想象如果扩展到整个地图,将是一个海量工程。

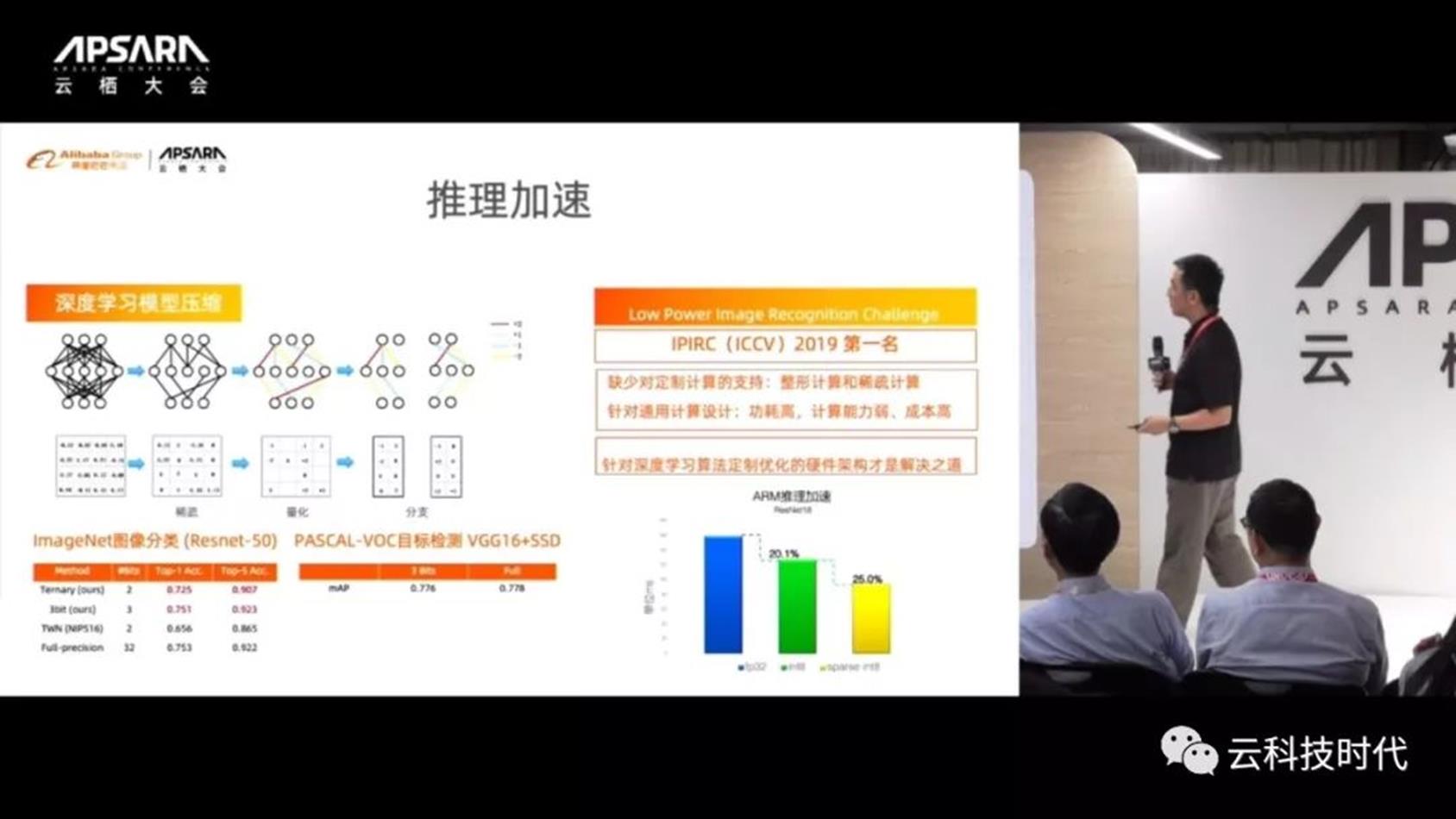

今天作为阿里的AI核心团队,面对这样的计算挑战,面对大数据的问题,我们做了不少工作,包括大量的推理加速工作,一个主要努力是模型压缩,例如对Fully Connected Network(FCN)可以试着去掉一些连接等,从而减少计算量,提高计算的吞吐能力。

我们还在做所谓的低功耗图像识别,这时候需要设计design神经网络架构的搜索方式,找到更合适的神经网络架构,从而更好的完成低功耗识别。所有这些都有一个问题,那就是所有的改变都发生在软件层和算法层,而如果没有底层硬件层的支持,这些改变也不会发挥最大效果,一个最突出的例子就是Sparse Connectivity,大家可以看到如果把神经网络算法从全连接Full Connected变成稀疏连接Sparse Connectivity的话,从理论上应该可以得到很大的加速,但是如果没有底层硬件的支持,这样一个加速将会受限。

由于这些原因,我们跟焦阳的团队合作,希望能够把上面最好的神经网络算法结构与底层最好的硬件支持结合起来,从而交付一个最强大的计算引擎。所以下面请焦阳介绍含光800芯片。

焦阳:我们团队在设计这款NPU的时候,能够在比较短的时间有比较大的进步,实际上在很大程度上是与阿里巴巴达摩院算法团队合作(金榕、华先胜、王刚等),团队在人工智能领域有多年的积累,如果没有这种积累就很难想象NPU会在很短的时间迅速找到方向,包括到底要怎样的设计、要解决什么样的问题、要设计什么样的架构才能突破传统的CPU和GPU优势,以及怎么样通过软硬件一体化的方法找到一条新的道路。

我刚加入阿里的时候,实际上一段时间比较苦恼,就是做什么样芯片以及怎么做的问题,在达摩院算法团队的帮助下,比较快地渡过学习曲线。

算法角度不仅是一种对人工智能算法的理论研究,也做了很多实践上的探索。入手的时候,要对神经网络本身以及业务算法有很深入的了解,这种了解如果没有阿里达摩院团队在之前的时间积累是不可能达到的。

当初在做这款NPU的时候几个重要的思考点:一是为什么要做一个云上的大芯片,云上大芯片的考虑是什么呢?阿里巴巴云计算是快速增长的业务,在国内是属于非常领先的位置,云计算是我们的强项。所以,通过硬件设计如果能帮助云快速地拓展业务、降低计算成本、提供海量计算能力,实际上是非常核心的一步。尤其在今天云计算业务的前提下,需要硬核往下走,否则很难在算力提升和成本下降方面有很大的突破,这是当时考虑的一个点。

大芯片考虑是这样的,我们希望在一个很高算力的水平上做一款NPU,而不是做一款中端或者低端的芯片,这个考虑是什么呢?最重要的目的是阿里巴巴的芯片不是短期的商业化或者销售片,更多是要赋能将来真正实现技术突破,把云计算的成本降下来。

而与算法团队的合作,让我们也意识到真正能把算法和软硬件一体进行设计,必须要解决算法中的一些痛点,这些痛点是什么呢?包括刚才金榕老师提到的像Bert这种大模型,在算力和存储等各方面的要求非常高,传统的计算平台很难满足这样的需求,所以必须要通过一个较大算力的芯片,才能真正能帮助业务往前走。

商业模式是非常重要的一个思考,我们不是单纯做技术,更多是商业模式的考虑。商业模式就是怎样通过技术带给业务一种新的能力,这个能力是什么呢?就是能够实现新的功能或别人没有做的功能或者以前因为硬件限制等种种原因没有做的功能,要通过芯片技术帮助到业务,这是我们的想法。

另外再就是第一颗芯片为什么要做一个推理(inference)芯片,而不是训练(training)芯片,我们当时跟算法团队一起讨论下来的结论是说无论从阿里巴巴还有整个业界来看,一个很强的趋势是当training到一定程度时,真正下一步实际上更多的是inference,尤其在云上的inference,我们认为是非常重要的一个开发领域。

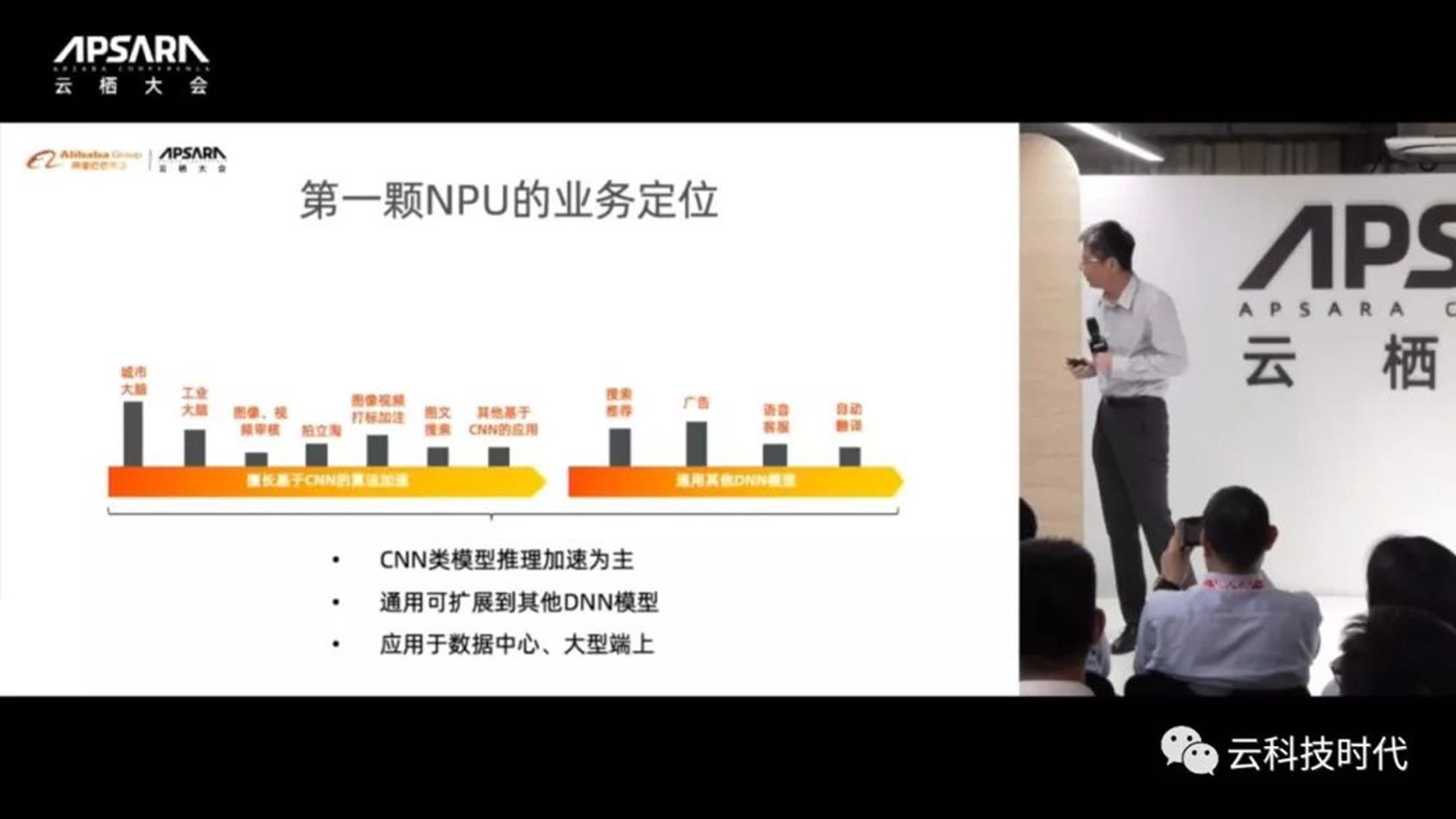

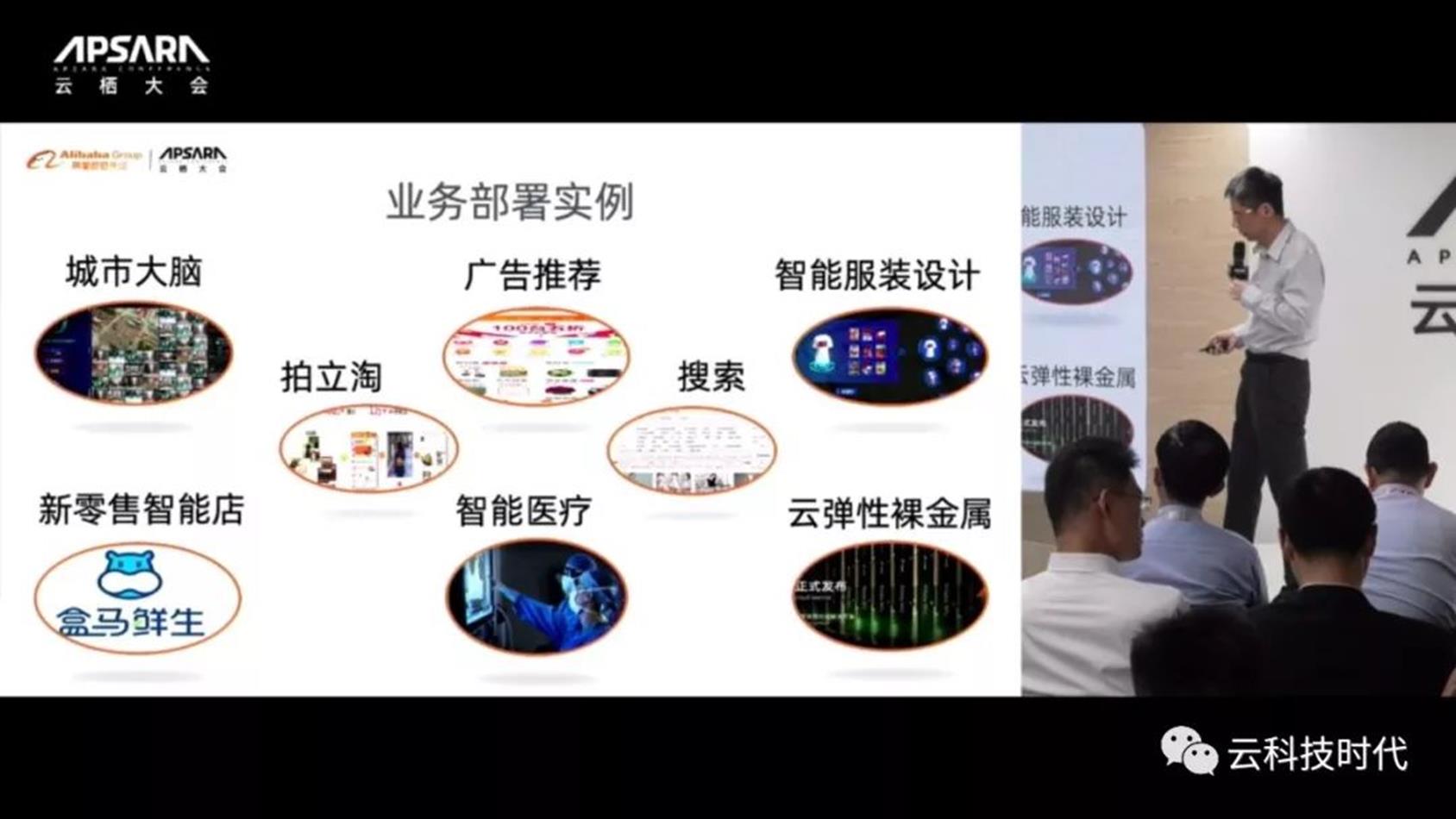

第一款NPU的主要目标业务,像城市大脑这种业务,包括视觉、视频分析等,这些业务有一个重要的特点是在提供算力后能大幅提高计算效力,让业务量达到一个突破,从而给云计算增加更多的流量,无论是用户流量还是计算量的增长,这才是真正解决通过硬件设计来帮助业务发展的目标。

第三,我们当初考虑到底做什么样的加速,阿里巴巴与其它互联网公司不一样的地方,像传统的互联网公司都会做搜索、广告等业务,是比较传统的互联网模式,而阿里巴巴除了有搜索和广告业务之外还有更多丰富的其它视觉类的业务,比如淘宝图片搜索、智能城市、智能工厂等应用,是更多CNN类应用、视觉类的应用场景。

这些算法牵扯到CNN算法以及DNN加速,我们通过业务上的了解之后,决定了CNN的加速可能对NPU是一个重点方向,同时要保证比较好的通用性,能把芯片扩展到将来新模型的适配。

那么,这款芯片结合业务上的思索,主要的特点是什么呢?

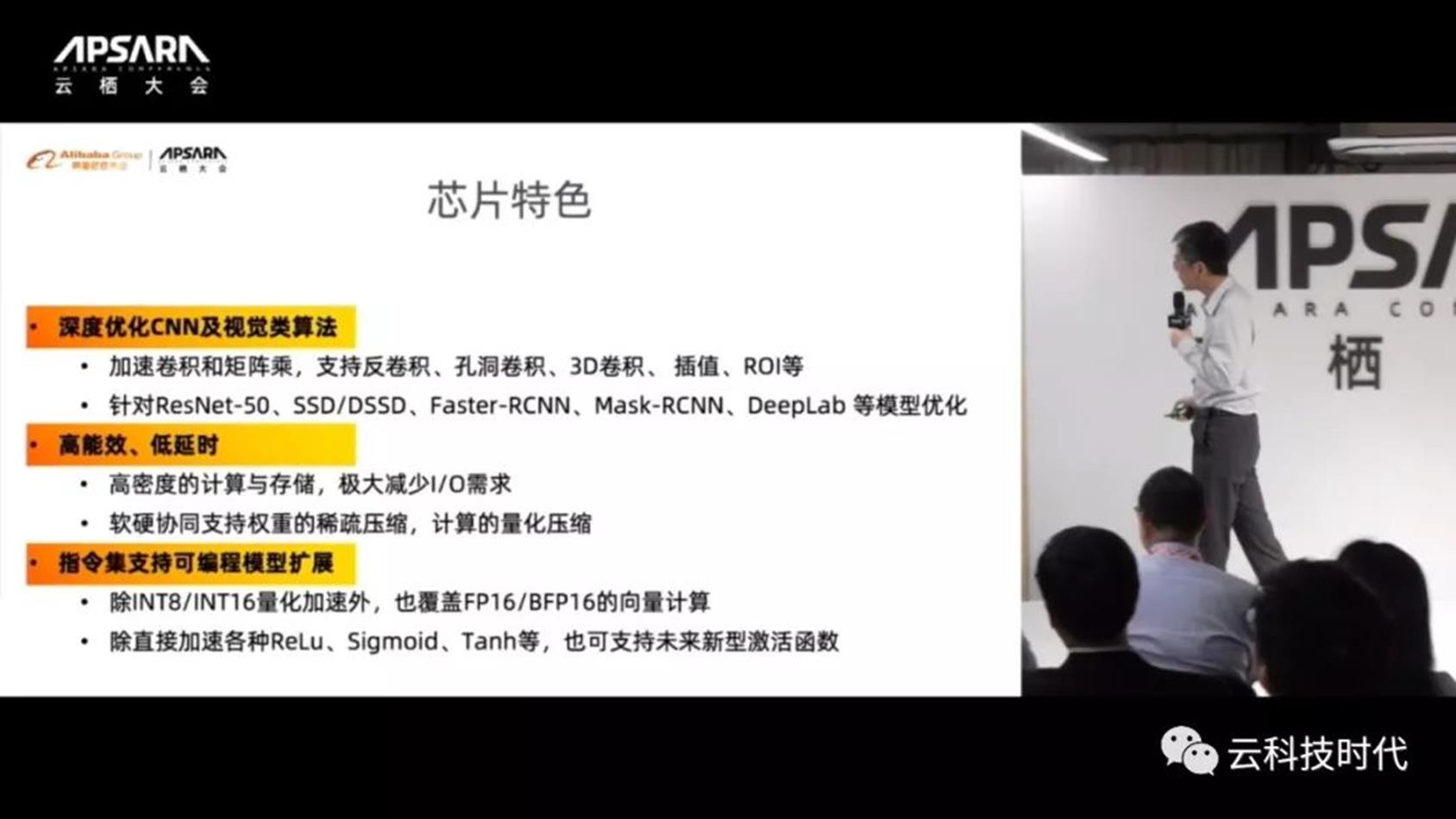

针对CNN类的,我们加速所有的卷积类,包括各种各样的卷积、反卷积、孔洞卷积、3D卷积等,还包括插值和ROI等;这些无论在分类网络、分割网络还是检测网络,都是常用的算子,我们对这些算子做了特殊的优化。

同时我们观察CNN网络,从ResNet逐渐发展到一个更复杂的网络结构,包括后来出现的Mask-RCNN和DeepLab这样的分割网络,从整个网络架构做深入分析,提炼出来架构上的特定优化策略。

我们的架构里还提到了重要的一点就是低延时和高能效,这个通过什么实现的呢?通过数据结构进行了特定分析,让数据在存储和访问的时候有非常高的效率,减少对内存I/O的需求。这块尤其对CNN类的卷积操作进行了很深入的优化,对数据进行复用,存取后进行指令算子融合,这样保证在单位内存访问下可以大幅提升计算密度,这是主要的创新。

第二,结合与算法团队合作的模型压缩和量化处理,这部分基本上用一种比较创新的办法,就是对整个全神经网络做了量化处理,对神经网络中间的激活函数等计算,在保持比较高精度的基础上,在存储上把精度降下来,这样可以减少内存带宽,这些都是我们在架构上的尝试。

第三,在通用可编程上做了尝试。当初设计架构的时候有一些新的网络算法还没有出现,包括后期看到的Mask-RCNN、DeepLab等,还是后来搜索用到的新型网络;我们在设计阶段经过算法上的尝试,保证了整个架构有一定的扩展性。

在高精度部分,混合精度也是一个主要的特色,混合精度8比特量化加速,主要处理CNN类的网络,对其它的非CNN神经网络需要比较高精度,我们增加了INT16的量化加速,同时有一个比较高精度的浮点向量处理器,包括激活函数、向量处理等都是用比较高的浮点运算支持的,这样保证架构在设计完成之后,对非CNN网络的适配,精度都可以达到需求。

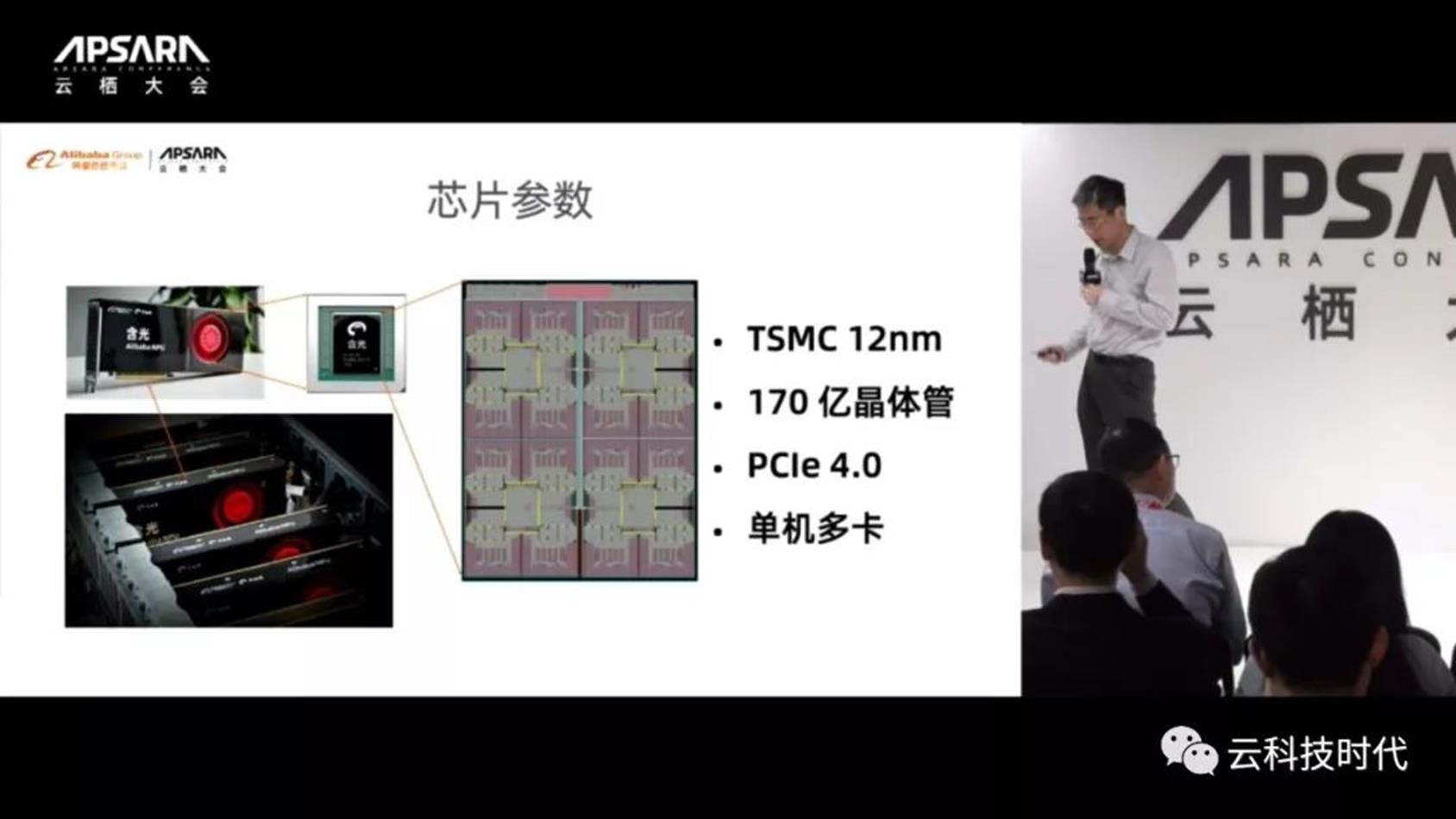

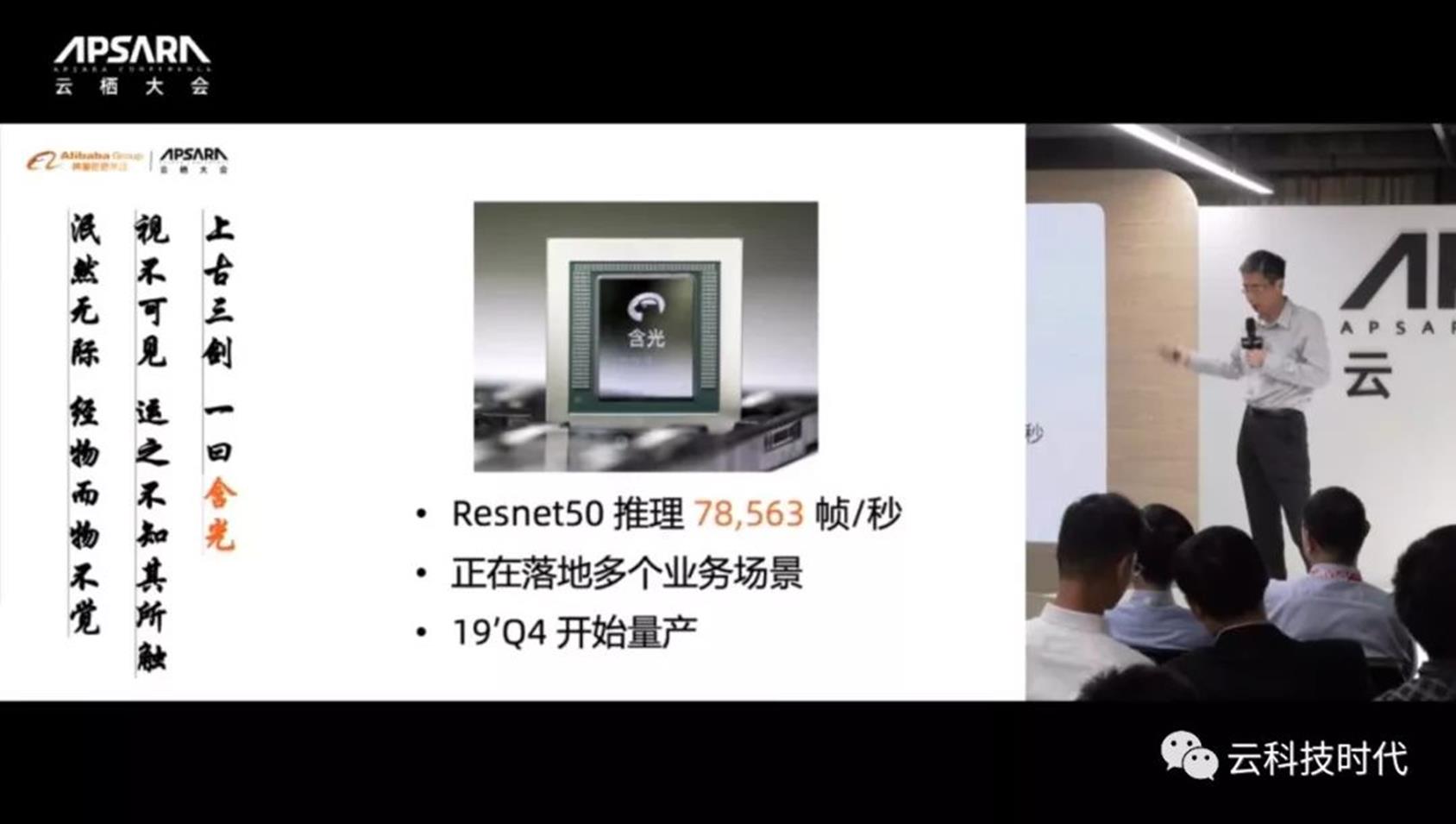

含光NPU的板卡散热设计,将来在阿里云的部署上会采用被动散热的板卡,这样可以减少板卡的体积,进一步降低成本。在服务器里面,展区有插着8卡NPU的服务器已经跑起来了。含光NPU的整个版图,可以看到是4个核的设计,整个面积接近170亿晶体管,是TSMC12纳米的工艺,采用PCle 4.0。

我们通过比较有效的片上压缩处理和流水线的处理,目前在PCle 3.0已经达到今天78000的ResNet成绩,说明带宽还没有用完,还有一倍的带宽可以用,目前已经用PCle 3跑到了峰值性能了。

大家看到含光800是4核设计,中间有命令处理器和高速互联的4核之间的网络,4核完全是同样的设计,这样设计的好处是可以在设计之后,由于良率提升的需求,可以任意四个核心有一个或者多个核心出现坏损的情况下,还不会影响整个芯片的工作,这也是我们在架构设计时特别处理的。

每个核的设计有什么呢?包括有本地内存local memory,非常接近Tensor计算核,也就是计算尽量位于存储边上,每次读出来的data可以被高度复用,再做融合算子的计算,这就是为什么含光NPU可以把功耗降到比较低的重要原因。

Tensor Array是非常有效的,我们是INT8和INT16实现的,所以它的功耗非常低,而且设计结构与Systolic Array不一样,用FLOP数量非常少,这样对功耗也有很大的帮助。

中间是向量处理器(Vector Engine),向量处理器实际上可以提供多到Floating 24bit的精度,是非常高的精度,中间的sequencer还带有各种各样的Special Function Unit(特殊函数单元),指各种各样的激活函数,比如Sigmod、LogEXP等丰富的特殊函数,这实际上有点类似于GPU的特殊函数,所以有一定的扩展性,将来可以支持新的激活函数。

这个sequencer讲一下,它是由一个高效的硬件决定,这个实际上在软件Schedule的基础上做了硬件的Scheduling,是一个多方式的机制,可以看到在做Tensor Core Operation的同时还会做Bias Normalization,以及Special Function激活函数,这样可以用pipeline的方式并行处理。

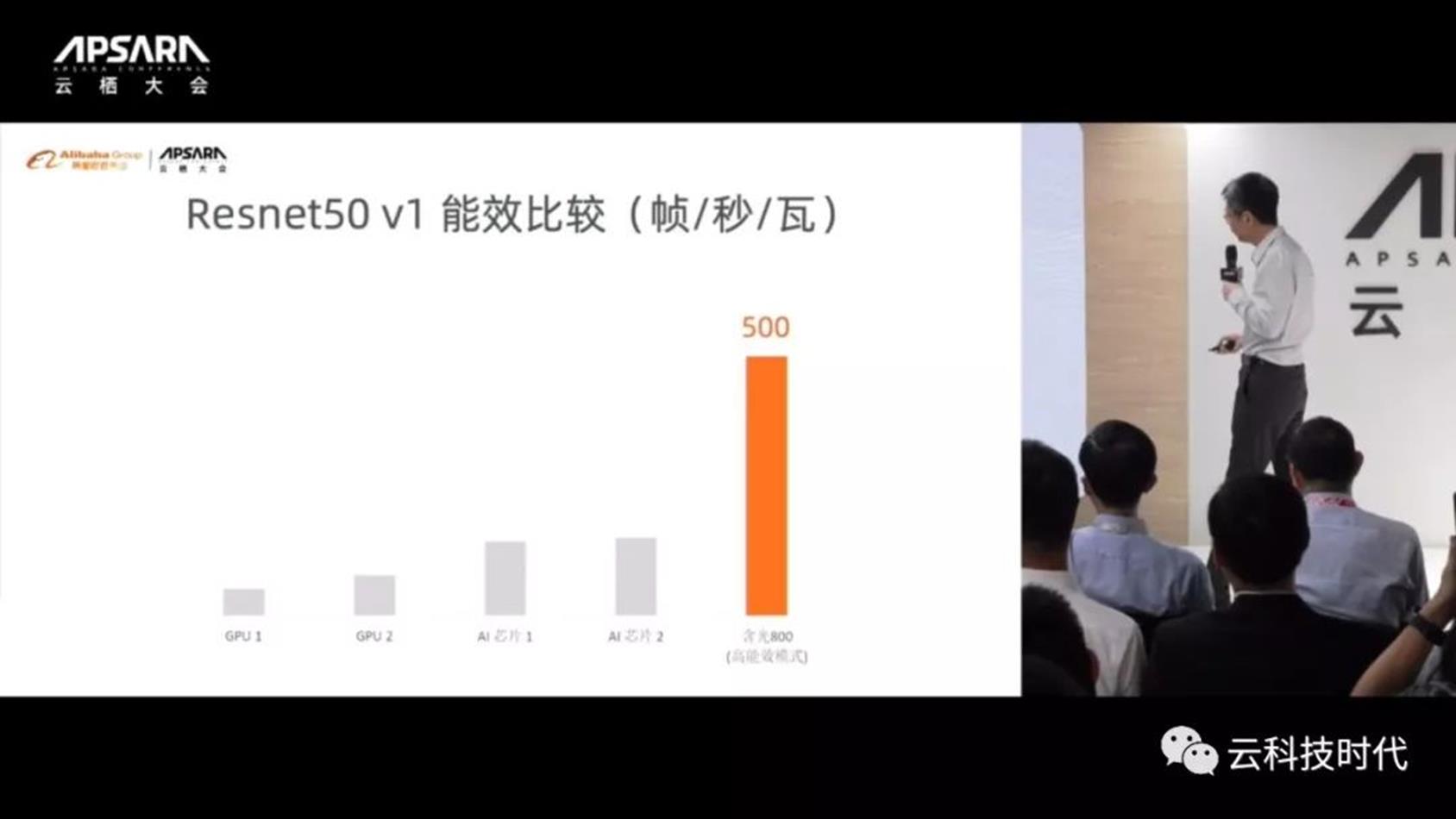

看一下Resnet50的分数,强调一下我们有两种模式,一种叫高性能模式,一种叫高能效或者低功耗模式,图中是在高性能模式下跑出来的成绩,在这个模式下跑分数的功耗是276W,实际上比英伟达的还算低了,其它的两个是GPU、后面两个是比较新的AI芯片。

去年我们在设计的时候有一个小的故事,我们设立了多少倍的目标,那个目标就是最左边的那个,所以已经达到去年说的目标了。

我觉得更重要是单位功耗性能。一般来做高性能的芯片,往往能效比较差。这张图告诉我们,实际上架构的有效性非常好,单位功耗下产生的性能还是比其它的几家公司芯片有很大的优势,这个是在高性能模式下跑出的成绩。

应用的场景有数据中心,将来也希望覆盖边缘服务器,甚至一些大型端上的应用。我们设计芯片的特点跟其它芯片公司不太一样,我们不能有很多型号一次量产出来,所以只有一次流片的机会,尽量把同样的一块芯片用到多个不同的场景,这是我们当初设计的一个理念。

解释一下,四个核的跑在数据中心里,如果一个核、两个核、三个核的芯片怎么办呢?也可以用,就用到端上、边缘服务器的场景产品,实际上功耗可以降下来,如果没有那么多核或者不需要多核的话,可以并出来那种单核、双核的配置,这样可以实现很低的功耗,75W、50W甚至25W,但是算力还是相当好的,所以还是非常吸引人的。

大家看到276W可以跑到78000,但是通过降电压降频的话,100W多一点还可以跑到53000,这是非常有效的一个模式。所以,建议大部分的应用场景是用高能效的模式。

讲一下各种落地的业务。第一个最重要的就是城市大脑,目前在交通场景有很多交通摄像头,大家看到一个城市或者小区里面有上千甚至上万个摄像头,这样对处理视频的能力和算力要求非常高,含光NPU非常适用这种场景。这里主要的业务算法是什么呢?包括这么几个部分,第一部分先做目标识别,就是目标检测,这部分算法一般是基于SSD和Fast R-CNN、YOLO这些算法,主要是检测图像里的移动物体,比如机动车、非机动车等,从图中找出来。第二部分再做Tracking,Tracking是跟踪物体跑到哪里,运行轨迹是什么样的。目前这部分还是用CPU在做,我们现在与达摩院城市大脑团队合作,把这一部分转成CNN的网络,一旦成功的话就可以把算力充分地用起来,解决CPU的瓶颈。第三部分,找到对象之后做特征提取,这部分一般是用DenseNet或者比较深的ResNet网络,特征提取后去做ReID重新识别和分类,这部分业务算法流程基本上是这样的。

第二个也是重要的落地业务,拍立淘。拍立淘用户上传商品照片,照片经过AI的处理,首先做类目检测,判断出它大概属于哪一类产品,可能是鞋子帽子之类,根据类目推测的结果做主体识别,主体识别类似于刚才讲的目标检测算法,一般都是SSD或者是基于ResNet的算法。这部分做完主体检测之后,抠图产生出搜索目标,搜索目标处理后当做搜索的主体进行特征抽取,特征抽取之后形成特征向量进行检索,与数据库里的海量商品数据做比对,找到最接近的商品,然后把商品返回给用户,大概是这样的流程。这里涉及的算法,主要三步都是用CNN类神经网络实现的,这一部分在业务上完全可以适配了,目前大概有400M(4亿)的参数,现在完全可以在一个NPU板卡上跑起来了,这是拍立淘。

广告推荐和搜索是下一步想去做的业务,这是两个很典型的MLP网络,实际上不是我们主要的优化网络,但这一步可以验证精度各方面是否达到当初的设计要求,这是我们在积极尝试的两个业务。

智能服装设计是做潮流分析,通过海量数据分析出服装的流行趋势,可以做服装设计。这用到的是一种对抗生成式的网络GAN,GAN网络现在用得比较火的是换脸游戏,里面用到的也是相同的算法。我们当初在设计的时候也不知道有这样类型的神经网络,我们最近进行适配的时候发现基本上都没有什么问题,都可以跑起来,而且性能已经达到对应GPU的大概十几倍,我们原来设计的是ResNet这样类型,基本上在GAN网络上也可以达到类似的性能了。

其它几个包括盒马,这些都是智能店的应用,智能医疗也就是大量图片处理、进行医疗的分析,这些都是一些典型的图像处理应用。

最后一个就是弹性裸金属,把NPU放到云上去,通过云售卖NPU技术。

这个是我们的软件栈,目前的应用包括视觉类、自然语言处理、推荐、搜索这样的应用,主流神经网络框架都支持了;离线做编译、优化、量化处理;以及非常高效的驱动程序,对主流框架对接做执行。

总结一下Resnet的成绩,特别想提到一点是Mask R-CNN的demo(非常酷),可以跑4个video stream的Mask R-CNN,可以全速在跑,是非常不容易的,大家都知道其他GPU,要达到这个是很不容易的。

参考文献链接

https://mp.weixin.qq.com/s/XFtGmGJE9tWCbsPgaCyXJQ

https://mp.weixin.qq.com/s/4ZtqYEcWx4iyir8kFz3ABg

「AI芯片/GPU/NPU/DSP专用处理器」技术特征比较分析最新2022综述论文

点上方人工智能算法与Python大数据获取更多干货

在右上方 ··· 设为星标 ★,第一时间获取资源

仅做学术分享,如有侵权,联系删除

转载于 :专知

微处理器是现代信息系统的核心基础设施. 大数据、人工智能、5G 等技术的快速发展催生了数据量的爆发性增长, 随之对数据处理能力的需求也急剧增长. 专用计算技术被广泛认为是后摩尔时代的计算机体系结构演化的重要方向. 专用处理器技术的发展一直伴生着通用处理器的发展, 数字信号处理技术甚至早于传统意义上的通用处理器. 通用处理器技术的发展, 不仅在商业上取得了巨大的成功, 很多关键技术也被专用处理器吸收借鉴用于提升专用计算的性能、优化可编程性等. 本文主要分析了数字信号处理器(DSP)、图像处理器(GPU)、深度学习处理器(AI 芯片)和网络处理器(NPU)的关键技术特征, 并进一步对专用计算架构未来发展可能涉及的关键点作出了简要的评述.

https://www.sciengine.com/publisher/scp/journal/SSI/52/2/10.1360/SSI-2021-0274?slug=abstract

1 引言

如果不考虑成本因素, 一颗理想的处理器应该可以像 CPU (central processing unit) 一样通用, 像 DSP (digital signal processor) 一样处理数字信号, 像 GPU (graphics processing unit) 一样处理图像数 据, 像 NPU (network processing unit, 网络处理器, 也简称 NP) 一样处理网络数据包, 像 “矿机” 一样 竞争加密货币共识算力, 像神经网络芯片一样运行深度神经网络训练和推理等. 但是, 实现如此万能的 处理器芯片是不现实的, 至少从经济成本角度不具备可行性, 专用化就成为了发展的必然 [1] . 专用处 理器并不是通用 CPU 完全改弦易辙, 而更像是基于通用处理器技术的一种分化. 所以我们看到现代 DSP、基带处理器、网络处理器的很多成功产品都包含一个甚至多个通用 RISC (reduced instruction set computer) 核来做系统管理、运行操作系统、与主机通信, 将协处理器也变成一个具备自我管理能 力的主动设备. 从时间上看, DSP 可能也是出现最早的计算芯片, 在集成电路发明 (1958 年) 之前, 德 州仪器 (TI) 公司已经在大批量生产硅晶体管器件. TI 公司在 1967 年发明手持计算器, 1971 年研制 了单芯片微型计算机. 在此之前的 “DSP” 只能称为利用分立器件信号处理 (processing), 还不是名副其实的 “processor”. DSP 没有被冠名某个 “PU” 的称呼也许正是由于出现过早, 当时 “PU” 的称呼还 没流行起来. CPU 最早出现在 1971 年, GPU 出现在 1993 年 (虽然当时的名称还不叫 GPU), 网络处 理器 (NPU) 出现在 1999 年. 从这些时间关系上看, 我们大体可以看出人们首先是对信号处理有需求, 然后才扩展到其他更普遍的数据处理需求上, 因此有了对通用 CPU 的需求. 再由于应用的驱动, CPU 难以满足性能要求, 进而发展出了 GPU, NPU 等更专用的计算芯片. 从这个意义上看, 通用 CPU 技 术可以视为处理芯片的基本技术, 在此基础上发展了高性能 CPU、现代高效能 DSP [2]、高吞吐 GPU、 高通量 NPU [3] 等各种 “XPU”. 个人认为分析这些 XPU 的结构特征有助于更深刻地理解 “通用” 和 “专用” 的本质差异.

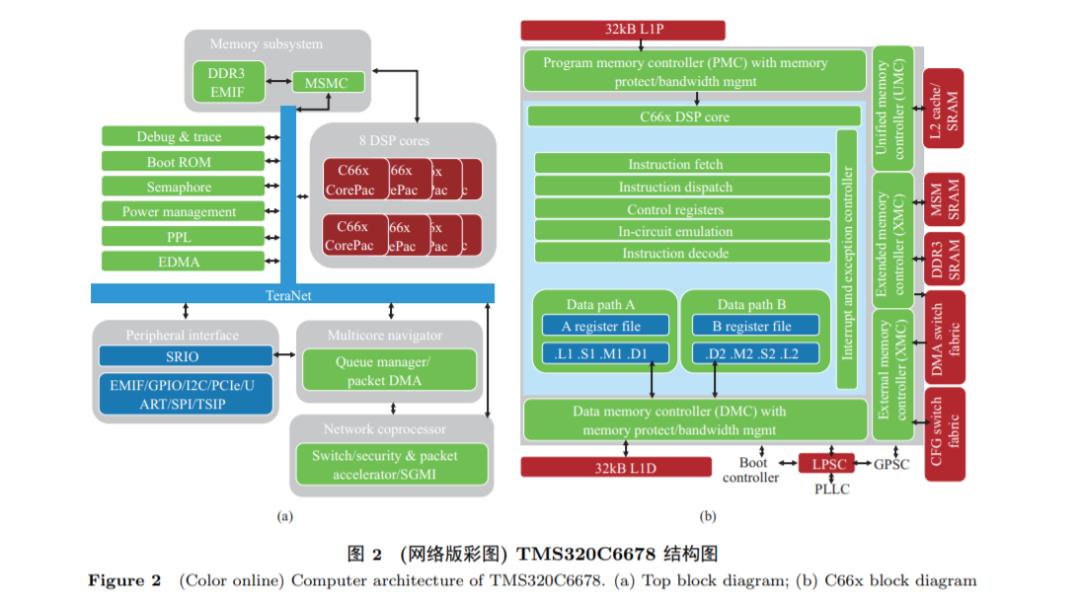

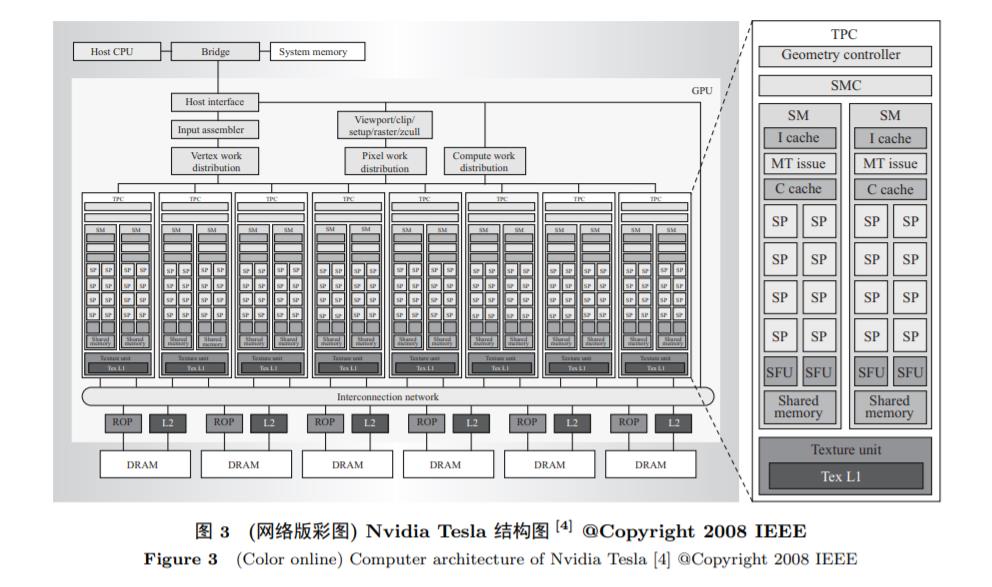

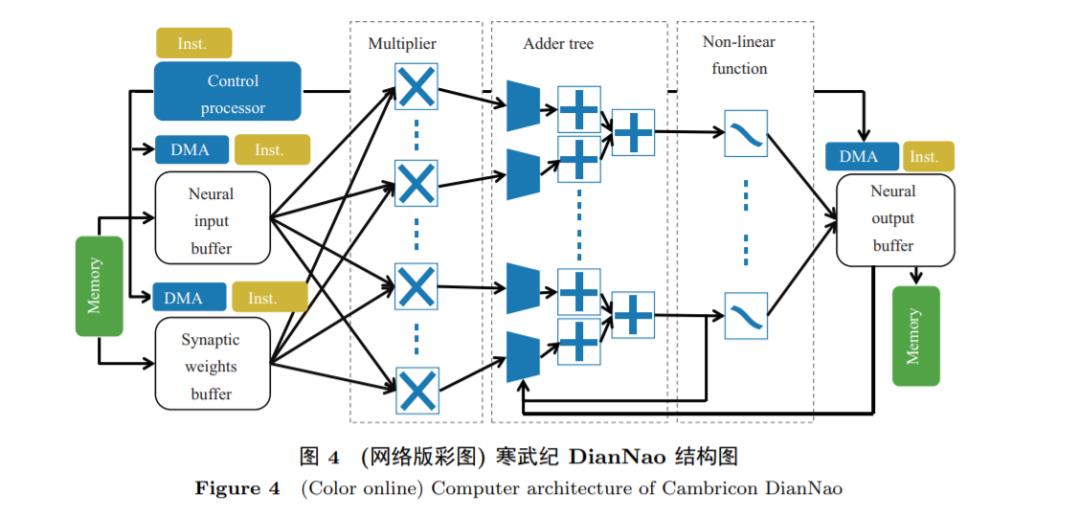

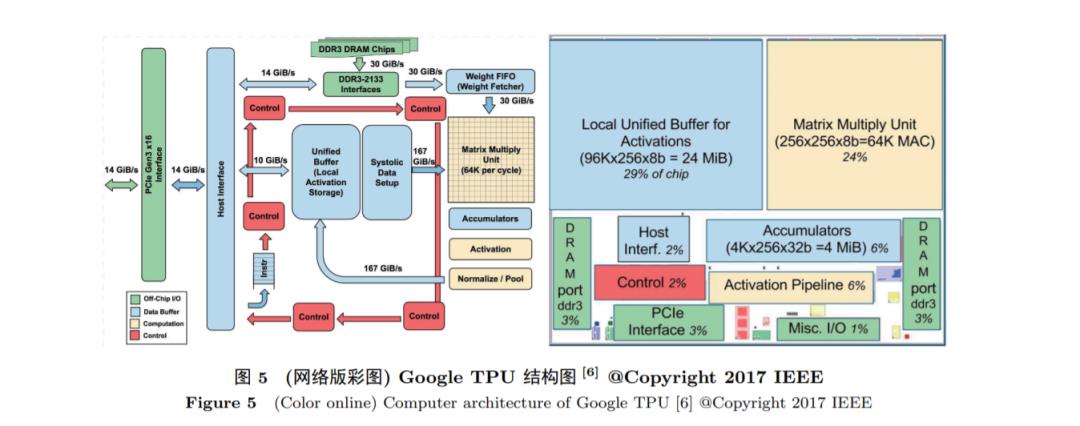

针对专用处理器有很多关键问题, 包括: 芯片在架构上有什么差异, 各自具备什么样的软件生态, 能否取得商业上的成功的决定性因素是什么等, 而答案也莫衷一是. 本文的重点是试图从架构层面去 看待这些不同类别的专用处理器芯片的差异, 帮助我们预测未来架构的发展趋势, 对于专用处理器技 术未来的发展做了些许开放性的讨论, 抛砖引玉. 其次, 本文主要讨论经典专用处理器的演化, 而把通 用 CPU 的发展作为背景而暂不加以专门讨论. 同时, 本文主要以 DSP、GPU、AI 芯片和 NPU (网络 处理器) 为主要参考对象, 其中 DSP 以 TI 公司的 C6000 系列为主要参考, GPU 以英伟达 (Nvidia) 公司的 Tesla 架构为主要参考 [4] , AI 芯片以寒武纪的 DianNao [5] 深度学习处理器和 Google 公司的 TPU (tensor processing unit) [6] 为主要参考, NPU 以迈络思 (Mellanox) 公司 (已经被 Nvidia 公司收 购) 的 NP-5 和因特尔 (Intel) 的 IXP [3] 为主要参考, 均为各个公司比较有代表性的产品. 限于篇幅, 本文尚未将新出现 DPU (data processing unit) [7] 芯片架构纳入讨论, 相关内容将作为未来工作.

专用计算架构的设计难度不亚于通用 CPU, 核心目标就是 “有条件地” 高性能. 无论是一个 3 W 的 DSP, 还是一个 300 W 的 GPU, 也无论是面向哪一个专用领域定制化的设计, 都追求在给定的功 耗、芯片面积约束下实现高性能. 然而, 这个问题的复杂性在于专用计算并不仅仅是设计几个运算单 元, 配合几条数据通路那么简单, 它涉及到 IO 子系统、操作系统内核、网络协议栈、访问安全、虚拟 化、二次开发的方便程度等层面的问题, 其中任何一个层面的问题的专业性都极强, 要能融汇贯通并 能系统地组织起来是一个巨大的挑战. 挂一漏万, 本文的内容只代表笔者的观点.

本文余下内容安排如下: 第 2 节阐述了专用处理器的基本概念, 第 3∼6 节分别介绍了数字信号 处理器 (DSP)、图形处理器 (GPU)、AI 芯片和网络处理器 (NPU) 4 类重要的专用处理器的基本特征, 第 7 节表述了笔者对于专用处理器的几点思考, 据此在第 8 节提出了构建专用处理器系统结构的关 键点, 第 9 节总结全文.

专用处理器的基本概念

专用处理器(或专用加速器), 顾名思义, 就是用于处理“特定应用"的处理器, 相对于通用处理器而言, 这类处理器性能更高、功耗更低、通常价格也更便宜, 但是使用范围也相对有限. 计算芯片产业在过去50年的发展历程中, 比较成功的专用处理器门类只有数字信号处理器(DSP)、图形处理器(GPU)和网络处理器(NPU), 这是20世纪90 年代就已经基本定型的格局. 在过去5年中, 用于处理深度学习的神经网络处理器(AI芯片)也开始快速发展, 比较成功的案例包括Google公司的张量处理器TPU [6]、寒武纪公司的DianNao系列深度学习处理器 [5] 等. 专用处理器的最终目标不是替代通用CPU, 而是与现有的通用CPU技术协作, 即将部分CPU运行效率低下的应用卸载(offloading)到专用加速器上运行, 通过构建异构计算平台来高效地处理计算任务. 从产业生态的视角来看, 相比于通用处理器的硬件与软件分离的“水平"模式, 专用加速器更注重软硬协同的“垂直"发展模式.

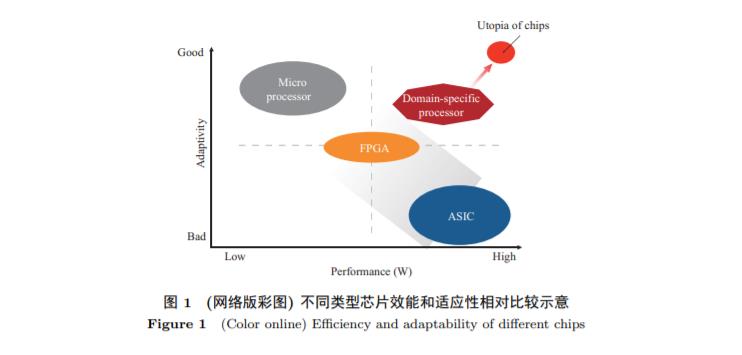

图1从芯片的效能和适应性两个维度来刻画芯片的特征. 这里效能指的是单位功耗下提供的计算能力, 适应性就是通常意义下的通用性. 业界通常将数据处理芯片大体分为三大类: 处理器芯片、ASIC (application specific integrated circuit)芯片和FPGA (field programmable gate array)芯片. 处理器芯片包括CPU, GPU, DSP等, 是用户可编程的芯片; ASIC是面向特定应用(application-specific)的专用集成电路[8], 通常也称之为全定制芯片, 不可编程; FPGA器件属于专用集成电路中的一种半定制电路, 是可“编程"的逻辑列阵, 利用查找表来实现组合逻辑, 但FPGA的“编程"与处理器芯片的软件编程不同, 主要是配置逻辑, 可以理解为硬件编程. 从相对性能来看, ASIC芯片最好, 处理器芯片最差, FPGA介于二者之间; 但是从应用的适应性来看, 处理器芯片最好, FPGA次之, ASIC芯片最差. 值得注意的是这种分类标准并不是按照电路制造工艺, 例如处理器芯片和ASIC芯片本质上都是全定制的集成电路, 处理器芯片本质也是一种ASIC, 但与通常意义上ASIC的最大差别还在于是否具有指令集, 有指令集的就更类似传统的处理器, 反之就归类为ASIC. 此外, 处理器芯片由于其使用广泛、出货量大, 与软件生态联系尤其紧密, 所以将其独立为一个大的类别.

专用处理器芯片的研发追求达到效能和适应性的一个新的帕累托最优(Pareto optimality): 效能接近ASIC, 但是适应性向处理器芯片靠近. 在效能上, 专用加速器通过定制化实现远高于通用处理器芯片的效能; 在适应性上, 从面向特定应用(application-specific)的ASIC范式进化为面向特定领域(domain-specific)的新范式, 不妨称之为“DSIC (domain-specific integrated cirucuit)". DSIC与处理器芯片相比虽然弱化了通用性, 但与ASIC相比也强化了适应性.

无论是DSP、GPU、AI芯片、NPU, 还是现在更新的各种“XPU", 都是处理数据的芯片, 最终都需要执行二进制代码的程序来完成计算. 因此专用处理器设计也大都需要涉及如下6方面内容:(1)约定二进制代码的格式, 即指令; (2)需要将指令变换为机器码, 即汇编; (3)为了提高编程方便程度, 需要将高层程序语言转换为汇编语言, 即编译; (4)为了提高编程的效率, 提供了各种编程环境, 即集成开发环境(integrated development environment, IDE); (5)充分复用高度优化的代码, 即应用程序库; (6)为了方便程序调试, 还需要提供各种仿真工具, 即仿真器(emulator). 所以, 从系统抽象层次来看, 与通用处理器几乎没有区别. 但是不同的DSIC侧重点不同, 有些DSIC只提供API (application programming interface)方式的调用, 例如早期的GPU, 将编译、汇编等过程全都凝结在运行时库中, 从用户角度看, 调用过程与使用OpenCL [9]中的“内建核函数(built-in kernels)"类似, 与调用普通的库函数过程相同; 虽弱化的可编程性, 但是强化了用户使用的便利性. 但也有些DSIC, 如DSP, 使用了大量底层编程, 虽编程难度高, 但方便精确地性能调优.

3 DSP: 灵活的数据格式

DSP也许是最早出现的专用集成电路. DSP的使用范围非常广, 从简单的MP3播放器到最新一代的5G通信都有使用场景. 常见的DSP大多带有丰富的外设接口, 例如PCIe、以太网、UART、I2C等, 尤其在很多嵌入式设备中, 丰富的外设接口对于提高系统的集成度、降低成本和功耗都有很大帮助, 所以很多DSP产品也演变成带有丰富外设接口的SoC (system on chip)芯片, 如图2(a)所示. 但是DSP最大的特点还是进行数字信号处理的核. 大多数DSP由于使用场景多为移动设备, 或者只是作为CPU系统的数据输入前端, 在系统中的地位并不高, 通常在功耗、散热等方面都不可能给予太高容限, 所以功耗敏感、计算位宽对DSP很重要, 定点、浮点, 半精度、单精度、双精度, 16位、24位、32位、40 位等各种数据格式规范“五花八门". 在寻址上, DSP对于数据对齐方式也最灵活, 设置了大量专门的指令对数据进行对齐操作.

TI公司是DSP芯片的龙头, 被媒体评为是半导体行业利润率最高的公司. 2019财年营业总收入144亿美金, 税后净利润高达50亿美金, 利润率高达35%. 作为比较, 同期Intel收入720亿美金, 利润率29%; 英伟达总营收110亿美金, 利润率25%. TI公司的DSP主要分为3大系列: C2000系列, 集成了AD转换、Flash存储等, 主要用于控制马达、变频器等工控产品; C5000系列, 16 位定点, 主要用于便携声音、视频、机顶盒等设备; C6000系列, 采用了VLIW (very long instruction word)架构, 每秒执行指令峰值可达百亿条, 主要用于数字通信、图像增强、传输、加密解密等对性能要求更高的场景. 下面就以比较复杂的C6678为例做简要介绍, 其顶层架构如图2所示.

粗略观察DSP核其实与通常的RISC核没有太多区别, 如图2(b)所示: 都包括了取指令、指令分发、译码、寄存器读写、Load/Store、计算执行等环节, 但微体系结构有非常显著的特色. 例如, 普通采用超长指令字(VLIW)架构、突出的浮点处理能力、指令与数据分离等, 分析如下.

4 GPU: 数据并行的典型代表

GPU是专为图形(graphic)处理设计的专用处理器. 随着多媒体可视化需求的爆发, 传统的CPU是无法应对每秒动辄数百兆的视频渲染等任务. 高清图像、视频数据天然具备数据并行的特征, 可以通过高度的并行性来同时计算像素块中所有像素的色度、亮度等数据. 图3显示的是英伟达公司研发的经典Tesla架构的GPU, 之所以经典, 是因为从这一代架构开始, GPU 开始朝着通用GPU (即GPGPU)发展, 为后续GPU在深度学习领域的广泛应用奠定了基础.

5 AI加速器: 大规模张量处理

随着深度学习算法效果在图像处理中取得突破, 深度学习在越来越多的应用领域被应用. 在过去5年中, 用于处理深度学习的神经网络处理器(AI 芯片)快速发展, 其中比较成功的案例包括寒武纪的DianNao系列深度学习处理器[5] (图4)、Google的张量处理器TPU [6] (图5) 等. AI加速器大多针对机器学习中张量运算展开加速, 多基于SIMD方式实现, 单条指令通常可以完成一个矩阵的乘法运算, 因此也称为张量处理器. 除了张量处理之外, 还会伴有一些激活函数处理等非线性操作, 运算量相对较小, 实现起来也相对简单. 此类加速器重在张量处理, 控制相对简单, 通常不会集成通用处理核.

6 NPU: 为网络数据包处理而生

计算机网络是计算机系统发展过程中的一个伟大发明, 网络是大规模并行计算、分布式计算的必要条件. IBM于1974年发布SNA (system network architecture)系列网络协议, 主要解决IBM 的大型机与外围节点的通信问题. 这些节点并不是完整的计算机, 而是像用于ASCII图像显示终端的IBM-3174控制器、打印机等设备. 1974年之前程序还写在纸带上, 主要处理模式还是批处理; SNA引入以后, 开启了事务处理的先河, 把网络通信中容错任务交给了网络协议来处理, 并且基于SNA后来发展出了应用程序接口(API)等概念. 随着后续几年越来越多的设备开始采用网络来连接, 不同厂商提供了不同的网络, 为了解决不同网络间的互连互通(internetwork communication), 美国标准化组织于1981年提出了经典了开放系统互连(open systems interconnection, OSI) 7层模型[13], 这个参考模型一直沿用至今, 仍未过时.

网络处理器的出现是网络技术发展的必然. 随着OSI模型的普及和广泛接受, 在2000年前后, NPU还是学术界研究的热点领域. 第1颗网络处理器于1999年问世, 随后得到了许多半导体公司、网络设备厂商的关注, 据不完全统计, 前后有30余家厂商完成了500余款NPU的设计, 和现在的各种“XPU"的多样性相比有过之而无不及. IBM、 因特尔、思科、EZChip (于2015年被Mellanox收购)都推出了相应的系列产品, 典型如Intel的IXP系列和Mellanox的NP系列网络处理器.

各家NPU产品虽然各有差异, 覆盖不同的协议层次, 面向不同的协议内容, 但是它们的结构模块具有相似性, 例如都包含的模块包括通用处理器核、队列管理单元、路由管理、缓存管理、IO接口管理等. 值得一提的是, 最近兴起的DPU架构, 有很多特征借鉴了NPU技术, 特别是在对路由、交换、数据包处理的高效支持上, 相关讨论将作为未来工作开展.

7 关于专用处理器的几点思考

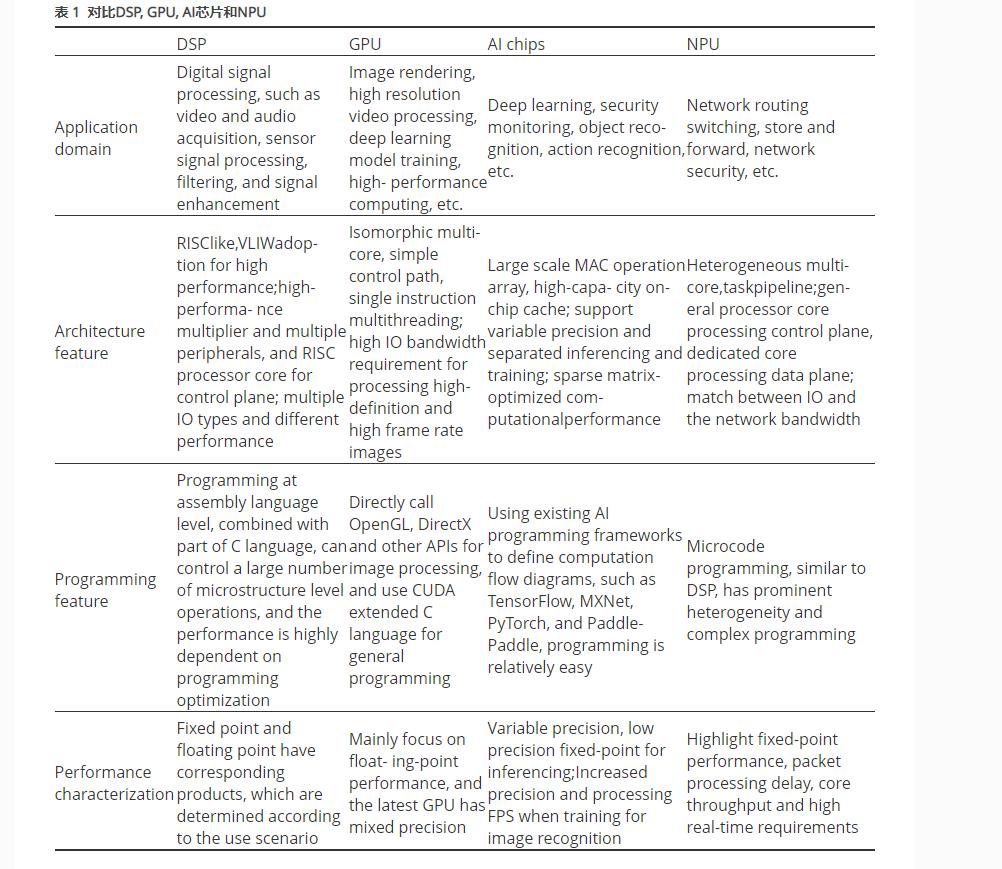

表1对前述的DSP, GPU, AI芯片和NPU从架构特征、编程特点和性能刻画3个维度进行了比较, 概述了这4类专用处理器的主要区别. 分析可以看出, 专用处理器的设计相比于通用CPU而言, 侧重点非常不同. 比如, 不太强调指令集, 也没过多的突出应用生态, 但是非常注重极致的性能优化, 注重与具体计算模式的匹配. 以下是笔者关于专用处理器的本质特征的几点思考, 抛砖引玉.

结论

采用专用处理器芯片是计算系统提升算力、提高效率的有效手段, 业界对于“XPU"概念的广泛关注反映了人们对新型计算芯片期望. 本文以经典的数字信号处理器DSP、图形处理器GPU、 AI芯片、网络处理器(NPU)作为案例, 以这4类专用处理器的结构特征为分析重点, 总结得出DSP最重要的结构特征是支持灵活的数据格式, 能效比优化极致; GPU 是充分利用数据并行的典型, 并且正在朝着通用化的方向发展; AI芯片围绕大规模张量处理, 支持可变精度来优化性能; NPU聚焦网络数据包处理, 构造高通量的流水线. 笔者发现一些在通用CPU中没有得到成功发展的技术, 如VLIW, 在专用处理器中发挥了重要作用; 而通用处理器体系下最重要维度, 如指令系统, 在专用处理器中反而被弱化了. 这些差异进一步引发了笔者从经典体系结构的角度对专用处理器的几点思考. 最后, 本文讨论构建专用处理器系统结构的4个关键点: 即针对数据平面的架构, 融合新存储、传输、封装等新技术, 面向领域专用语言和充分利用好“专用"这个特征来简化系统设计.

---------♥---------

声明:本内容来源网络,版权属于原作者

图片来源网络,不代表本公众号立场。如有侵权,联系删除

AI博士私人微信,还有少量空位

点个在看支持一下吧

以上是关于NPU的算法,架构及优势分析的主要内容,如果未能解决你的问题,请参考以下文章