verilog编程技巧

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了verilog编程技巧相关的知识,希望对你有一定的参考价值。

FPGA/CPLD的设计思想与技巧是一个非常大的话题,由于篇幅所限,本文仅介绍一些常用的设计思想与技巧,包括乒乓球操作、串并转换、流水线操作和数据接口的同步方法。

希望本文能引起工程师们的注意,如果能有意识地利用这些原则指导日后的设计工作,将取得事半功倍的效果!

乒乓操作

“ 乒乓操作 ” 是一个常常应用于数据流控制的处理技巧,典型的乒乓操作方法如图 1 所示。

乒

乓操作的处理流程为:输入数据流通过 “ 输入数据选择单元 ”

将数据流等时分配到两个数据缓冲区,数据缓冲模块可以为任何存储模块,比较常用的存储单元为双口 RAM(DPRAM) 、单口 RAM(SPRAM)

、 FIFO 等。在第一个缓冲周期,将输入的数据流缓存到 “ 数据缓冲模块 1” ;在第 2 个缓冲周期,通过 “ 输入数据选择单元 ”

的切换,将输入的数据流缓存到 “ 数据缓冲模块 2” ,同时将 “ 数据缓冲模块 1” 缓存的第 1 个周期数据通过 “ 输入数据选择单元 ”

的选择,送到 “ 数据流运算处理模块 ” 进行运算处理;在第 3 个缓冲周期通过 “ 输入数据选择单元 ” 的再次切换,将输入的数据流缓存到

“ 数据缓冲模块 1” ,同时将 “ 数据缓冲模块 2” 缓存的第 2 个周期的数据通过 “ 输入数据选择单元 ” 切换,送到 “

数据流运算处理模块 ” 进行运算处理。如此循环。

乒乓操作的最大特点是通过 “ 输入数据选择单元 ”

和 “ 输出数据选择单元 ” 按节拍、相互配合的切换,将经过缓冲的数据流没有停顿地送到 “ 数据流运算处理模块 ”

进行运算与处理。把乒乓操作模块当做一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进

行流水线式处理。所以乒乓操作常常应用于流水线式算法,完成数据的无缝缓冲与处理。

乒乓操作的第二个优点是

可以节约缓冲区空间。比如在 WCDMA 基带应用中, 1 个帧是由 15 个时隙组成的,有时需要将 1

整帧的数据延时一个时隙后处理,比较直接的办法是将这帧数据缓存起来,然后延时 1 个时隙进行处理。这时缓冲区的长度是 1

整帧数据长,假设数据速率是 3.84Mbps , 1 帧长 10ms ,则此时需要缓冲区长度是 38400

位。如果采用乒乓操作,只需定义两个能缓冲 1 个时隙数据的 RAM( 单口 RAM 即可 ) 。当向一块 RAM 写数据的时候,从另一块

RAM 读数据,然后送到处理单元处理,此时每块 RAM 的容量仅需 2560 位即可, 2 块 RAM 加起来也只有 5120 位的容量。

另外,巧妙运用乒乓操作还可以达到用低速模块处理高速数据流的效果。如图 2 所示,数据缓冲模块采用了双口 RAM ,并在 DPRAM

后引入了一级数据预处理模块,这个数据预处理可以根据需要的各种数据运算,比如在 WCDMA 设计中,对输入数据流的解扩、解扰、去旋转等。假设端口

A 的输入数据流的速率为 100Mbps ,乒乓操作的缓冲周期是 10ms 。以下分析各个节点端口的数据速率。

A端口处输入数据流速率为 100Mbps ,在第 1 个缓冲周期 10ms 内,通过 “ 输入数据选择单元 ” ,从 B1 到达 DPRAM1。 B1 的数据速率也是 100Mbps , DPRAM1 要在 10ms 内写入 1Mb 数据。同理,在第 2 个 10ms,数据流被切换到 DPRAM2 ,端口 B2 的数据速率也是 100Mbps , DPRAM2 在第 2 个 10ms 被写入 1Mb数据。在第 3 个 10ms ,数据流又切换到 DPRAM1 , DPRAM1 被写入 1Mb 数据。

仔细分析就会发现到第 3 个缓冲周期时,留给 DPRAM1 读取数据并送到 “ 数据预处理模块 1” 的时间一共是 20ms 。有的工程师困惑于DPRAM1 的读数时间为什么是 20ms ,这个时间是这样得来的:首先,在在第 2 个缓冲周期向 DPRAM2 写数据的 10ms 内,

DPRAM1 可以进行读操作;另外,在第 1 个缓冲周期的第 5ms 起 ( 绝对时间为 5ms 时刻 ) , DPRAM1 就可以一边向500K 以后的地址写数据,一边从地址 0 读数,到达 10ms 时, DPRAM1 刚好写完了 1Mb 数据,并且读了 500K数据,这个缓冲时间内 DPRAM1 读了 5ms ;在第 3 个缓冲周期的第 5ms 起 ( 绝对时间为 35ms 时刻 ) ,同理可以一边向

500K 以后的地址写数据一边从地址 0 读数,又读取了 5 个 ms ,所以截止 DPRAM1 第一个周期存入的数据被完全覆盖以前,DPRAM1 最多可以读取 20ms 时间,而所需读取的数据为 1Mb ,所以端口 C1 的数据速率为: 1Mb/20ms=50Mbps。因此, “ 数据预处理模块 1” 的最低数据吞吐能力也仅仅要求为 50Mbps 。同理, “ 数据预处理模块 2”的最低数据吞吐能力也仅仅要求为 50Mbps 。换言之,通过乒乓操作, “ 数据预处理模块 ”

的时序压力减轻了,所要求的数据处理速率仅仅为输入数据速率的 1/2 。

通过乒乓操作实现低速模块处理高速数据的实质是:通过 DPRAM 这种缓存单元实现了数据流的串并转换,并行用 “ 数据预处理模块 1” 和 “ 数据预处理模块 2” 处理分流的数据,是面积与速度互换原则的体现!

串并转换

串并转换是 FPGA

设计的一个重要技巧,它是数据流处理的常用手段,也是面积与速度互换思想的直接体现。串并转换的实现方法多种多样,根据数据的排序和数量的要求,可以选用

寄存器、 RAM 等实现。前面在乒乓操作的图例中,就是通过 DPRAM 实现了数据流的串并转换,而且由于使用了 DPRAM,数据的缓冲区可以开得很大,对于数量比较小的设计可以采用寄存器完成串并转换。如无特殊需求,应该用同步时序设计完成串并之间的转换。比如数据从串行到并行,数据排列顺序是高位在前,可以用下面的编码实现:

prl_temp<=prl_temp,srl_in;

其中, prl_temp 是并行输出缓存寄存器, srl_in 是串行数据输入。对于排列顺序有规定的串并转换,可以用 case 语句判断实现。对于复杂的串并转换,还可以用状态机实现。串并转换的方法比较简单,在此不必赘述。

流水线操作设计思想

首先需要声明的是,这里所讲述的流水线是指一种处理流程和顺序操作的设计思想,并非 FPGA 、 ASIC 设计中优化时序所用的 “Pipelining” 。

流水线处理是高速设计中的一个常用设计手段。如果某个设计的处理流程分为若干步骤,而且整个数据处理是 “ 单流向 ” 的,即没有反馈或者迭代运算,前一个步骤的输出是下一个步骤的输入,则可以考虑采用流水线设计方法来提高系统的工作频率。

流水线设计的结构示意图如图 3 所示。其基本结构为:将适当划分的 n个操作步骤单流向串联起来。流水线操作的最大特点和要求是,数据流在各个步骤的处理从时间上看是连续的,如果将每个操作步骤简化假设为通过一个 D触发器 ( 就是用寄存器打一个节拍 ) ,那么流水线操作就类似一个移位寄存器组,数据流依次流经 D触发器,完成每个步骤的操作。流水线设计时序如图 4 所示。

流水线设计的一个关键在于整个设计时序的合理安排,要求每个操作步骤的划分合理。如果前级操作时间恰好等于后级的操作时间,设计最为简单,前级的输出直接汇入后级的输入即可;如果前级操作时间大于后级的操作时间,则需要对前级的输出数据适当缓存才能汇入到后级输入端;如果前级操作时间恰好小于后级的操作时间,则必须通过复制逻辑,将数据流分流,或者在前级对数据采用存储、后处理方式,否则会造成后级数据溢出。

在 WCDMA 设计中经常使用到流水线处理的方法,如 RAKE 接收机、搜索器、前导捕获等。流水线处理方式之所以频率较高,是因为复制了处理模块,它是面积换取速度思想的又一种具体体现。

数据接口的同步方法

数据接口的同步是 FPGA/CPLD 设计的一个常见问题,也是一个重点和难点,很多设计不稳定都是源于数据接口的同步有问题。

在电路图设计阶段,一些工程师手工加入 BUFT或者非门调整数据延迟,从而保证本级模块的时钟对上级模块数据的建立、保持时间要求。还有一些工程师为了有稳定的采样,生成了很多相差 90度的时钟信号,时而用正沿打一下数据,时而用负沿打一下数据,用以调整数据的采样位置。这两种做法都十分不可取,因为一旦芯片更新换代或者移植到其它芯片

组的芯片上,采样实现必须从新设计。而且,这两种做法造成电路实现的余量不够,一旦外界条件变换 ( 比如温度升高 ),采样时序就有可能完全紊乱,造成电路瘫痪。

下面简单介绍几种不同情况下数据接口的同步方法:

1. 输入、输出的延时 ( 芯片间、 PCB 布线、一些驱动接口元件的延时等 ) 不可测,或者有可能变动的条件下,如何完成数据同步?

对于数据的延迟不可测或变动,就需要建立同步机制,可以用一个同步使能或同步指示信号。另外,使数据通过 RAM 或者 FIFO 的存取,也可以达到数据同步目的。

把数据存放在 RAM 或 FIFO 的方法如下:将上级芯片提供的数据随路时钟作为写信号,将数据写入 RAM 或者 FIFO,然后使用本级的采样时钟 ( 一般是数据处理的主时钟 ) 将数据读出来即可。这种做法的关键是数据写入 RAM 或者 FIFO要可靠,如果使用同步 RAM 或者 FIFO,就要求应该有一个与数据相对延迟关系固定的随路指示信号,这个信号可以是数据的有效指示,也可以是上级模块将数据打出来的时钟。对于慢速数据,也可以采样异步 RAM 或者 FIFO ,但是不推荐这种做法。

数据是有固定格式安排的,很多重要信息在数据的起始位置,这种情况在通信系统中非常普遍。通讯系统中,很多数据是按照 “ 帧 ”组织的。而由于整个系统对时钟要求很高,常常专门设计一块时钟板完成高精度时钟的产生与驱动。而数据又是有起始位置的,如何完成数据的同步,并发现数据的“ 头 ” 呢?

数据的同步方法完全可以采用上面的方法,采用同步指示信号,或者使用 RAM 、FIFO缓存一下。找到数据头的方法有两种,第一种很简单,随路传输一个数据起始位置的指示信号即可,对于有些系统,特别是异步系统,则常常在数据中插入一段同步码 ( 比如训练序列 ) ,接收端通过状态机检测到同步码后就能发现数据的 “ 头 ” 了,这种做法叫做 “ 盲检测 ” 。

上级数据和本级时钟是异步的,也就是说上级芯片或模块和本级芯片或模块的时钟是异步时钟域的。

前面在输入数据同步化中已经简单介绍了一个原则:如果输入数据的节拍和本级芯片的处理时钟同频,可以直接用本级芯片的主时钟对输入数据寄存器采样,完成输入数据的同步化;如果输入数据和本级芯片的处理时钟是异步的,特别是频率不匹配的时候,则只有用处理时钟对输入数据做两次寄存器采样,才能完成输入数据的同步化。需要说明的是,用寄存器对异步时钟域的数据进行两次采样,其作用是有效防止亚稳态 ( 数据状态不稳定 )的传播,使后级电路处理的数据都是有效电平。但是这种做法并不能保证两级寄存器采样后的数据是正确的电平,这种方式处理一般都会产生一定数量的错误电平数据。所以仅仅适用于对少量错误不敏感的功能单元。

为了避免异步时钟域产生错误的采样电平,一般使用 RAM 、 FIFO 缓存的方法完成异步时钟域的数据转换。最常用的缓存单元是 DPRAM ,在输入端口使用上级时钟写数据,在输出端口使用本级时钟读数据,这样就非常方便的完成了异步时钟域之间的数据交换。

2. 设计数据接口同步是否需要添加约束?

建议最好添加适当的约束,特别是对于高速设计,一定要对周期、建立、保持时间等添加相应的约束。

这里附加约束的作用有两点:

a. 提高设计的工作频率,满足接口数据同步要求。通过附加周期、建立时间、保持时间等约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率,满足接口数据同步要求。

b.

获得正确的时序分析报告。几乎所有的 FPGA设计平台都包含静态时序分析工具,利用这类工具可以获得映射或布局布线后的时序分析报告,从而对设计的性能做出评估。静态时序分析工具以约束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具输出正确的时序分析报告。

Xilinx

和数据接口相关的常用约束有 Period 、 OFFSET_IN_BEFORE 、 OFFSET_IN_AFTER 、

OFFSET_OUT_BEFORE 和 OFFSET_OUT_AFTER 等; Altera 与数据接口相关的常用约束有 Period 、

tsu 、 tH 、 tco 等。 参考技术A 太多了,网上一搜一堆一堆的,自己总结下,看别人的不行。

VGA协议与图像输出Verilog编程

VGA协议与图像输出Verilog编程

VGA简介

1.什么是VGA???

VGA(Video Graphics Array),视频图形阵列,是一种视频传输标准,具有分辨率高、显示速度快、颜色丰富等优点,不支持音频传输

2.VGA显示原理

VGA的数据引脚1、2、3(RED、GREEN、BLUE)输入的不是简单的0、1数字信号,而是模拟电压(0V-0.714V)。当引脚具有不同的电压时,VGA显示器显示不同的颜色。

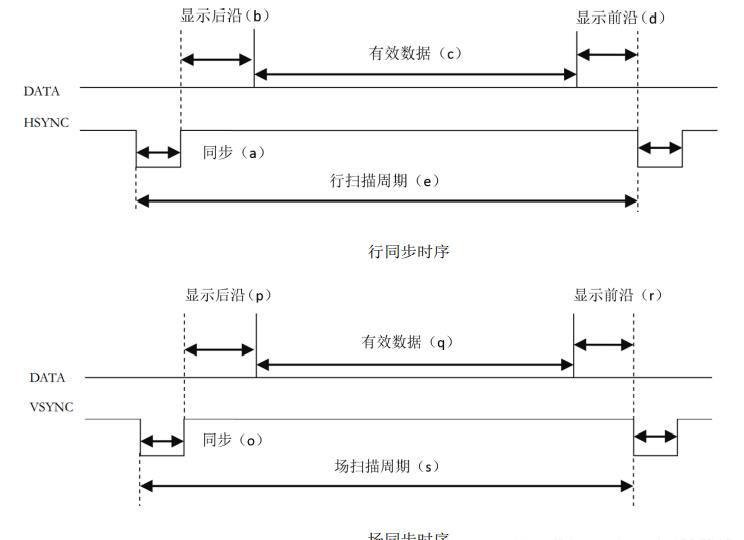

在VGA视频传输标准中,视频图像被分解为红、绿、蓝三原色信号,经过数模转换之后,在行同步(HSYNC)和场同步(VSYNC)信号的同步下分别在三个独立通道传输。VGA在传输过程中的同步时序分为行时序和场时序。

实验内容

1.创建工程(这里就不演示了)

1)首先点击File→New Project Wizard

2)然后选择工程保存路径,并填写工程名,点击Next

3)Family选择Cyclone IV E,芯片选择EP4CE115F29C7,然后点击Next

4)连续点击两次Next ,点击Finish。

2.新建verilog文件

点击File→New…,选择Verilog HDL File,点击OK。

3.复制以下代码:

module VGA_test(

OSC_50, //原CLK2_50时钟信号

VGA_CLK, //VGA自时钟

VGA_HS, //行同步信号

VGA_VS, //场同步信号

VGA_BLANK, //复合空白信号控制信号 当BLANK为低电平时模拟视频输出消隐电平,此时从R9~R0,G9~G0,B9~B0输入的所有数据被忽略

VGA_SYNC, //符合同步控制信号 行时序和场时序都要产生同步脉冲

VGA_R, //VGA绿色

VGA_B, //VGA蓝色

VGA_G); //VGA绿色

input OSC_50; //外部时钟信号CLK2_50

output VGA_CLK,VGA_HS,VGA_VS,VGA_BLANK,VGA_SYNC;

output [7:0] VGA_R,VGA_B,VGA_G;

parameter H_FRONT = 16; //行同步前沿信号周期长

parameter H_SYNC = 96; //行同步信号周期长

parameter H_BACK = 48; //行同步后沿信号周期长

parameter H_ACT = 640; //行显示周期长

parameter H_BLANK = H_FRONT+H_SYNC+H_BACK; //行空白信号总周期长

parameter H_TOTAL = H_FRONT+H_SYNC+H_BACK+H_ACT; //行总周期长耗时

parameter V_FRONT = 11; //场同步前沿信号周期长

parameter V_SYNC = 2; //场同步信号周期长

parameter V_BACK = 31; //场同步后沿信号周期长

parameter V_ACT = 480; //场显示周期长

parameter V_BLANK = V_FRONT+V_SYNC+V_BACK; //场空白信号总周期长

parameter V_TOTAL = V_FRONT+V_SYNC+V_BACK+V_ACT; //场总周期长耗时

reg [10:0] H_Cont; //行周期计数器

reg [10:0] V_Cont; //场周期计数器

wire [7:0] VGA_R; //VGA红色控制线

wire [7:0] VGA_G; //VGA绿色控制线

wire [7:0] VGA_B; //VGA蓝色控制线

reg VGA_HS;

reg VGA_VS;

reg [10:0] X; //当前行第几个像素点

reg [10:0] Y; //当前场第几行

reg CLK_25;

always@(posedge OSC_50)

begin

CLK_25=~CLK_25; //时钟

end

assign VGA_SYNC = 1'b0; //同步信号低电平

assign VGA_BLANK = ~((H_Cont<H_BLANK)||(V_Cont<V_BLANK)); //当行计数器小于行空白总长或场计数器小于场空白总长时,空白信号低电平

assign VGA_CLK = ~CLK_to_DAC; //VGA时钟等于CLK_25取反

assign CLK_to_DAC = CLK_25;

always@(posedge CLK_to_DAC)

begin

if(H_Cont<H_TOTAL) //如果行计数器小于行总时长

H_Cont<=H_Cont+1'b1; //行计数器+1

else H_Cont<=0; //否则行计数器清零

if(H_Cont==H_FRONT-1) //如果行计数器等于行前沿空白时间-1

VGA_HS<=1'b0; //行同步信号置0

if(H_Cont==H_FRONT+H_SYNC-1) //如果行计数器等于行前沿+行同步-1

VGA_HS<=1'b1; //行同步信号置1

if(H_Cont>=H_BLANK) //如果行计数器大于等于行空白总时长

X<=H_Cont-H_BLANK; //X等于行计数器-行空白总时长 (X为当前行第几个像素点)

else X<=0; //否则X为0

end

always@(posedge VGA_HS)

begin

if(V_Cont<V_TOTAL) //如果场计数器小于行总时长

V_Cont<=V_Cont+1'b1; //场计数器+1

else V_Cont<=0; //否则场计数器清零

if(V_Cont==V_FRONT-1) //如果场计数器等于场前沿空白时间-1

VGA_VS<=1'b0; //场同步信号置0

if(V_Cont==V_FRONT+V_SYNC-1) //如果场计数器等于行前沿+场同步-1

VGA_VS<=1'b1; //场同步信号置1

if(V_Cont>=V_BLANK) //如果场计数器大于等于场空白总时长

Y<=V_Cont-V_BLANK; //Y等于场计数器-场空白总时长 (Y为当前场第几行)

else Y<=0; //否则Y为0

end

reg valid_yr;

always@(posedge CLK_to_DAC)

if(V_Cont == 10'd32) //场计数器=32时

valid_yr<=1'b1; //行输入激活

else if(V_Cont==10'd512) //场计数器=512时

valid_yr<=1'b0; //行输入冻结

wire valid_y=valid_yr; //连线

reg valid_r;

always@(posedge CLK_to_DAC)

if((H_Cont == 10'd32)&&valid_y) //行计数器=32时

valid_r<=1'b1; //像素输入激活

else if((H_Cont==10'd512)&&valid_y) //行计数器=512时

valid_r<=1'b0; //像素输入冻结

wire valid = valid_r; //连线

wire[10:0] x_dis; //像素显示控制信号

wire[10:0] y_dis; //行显示控制信号

assign x_dis=X; //连线X

assign y_dis=Y; //连线Y

parameter //点阵字模:每一行char_lineXX是显示的一行,共272列

char_line00=272'hFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF, //第1行

char_line01=272'h00000000000000000000000000000000000000000000000000000000000000000000, //第2行

char_line02=272'h00400C0000000000000000000000000000C008000000000000000000000000000000, //第3行

char_line03=272'h00700E0000000180000000000000000000E00C0000000000000000800180000000C0, //第4行

char_line04=272'h00600C00000003C0000000000000000000C01C0000000000000000FFFF80000001E0, //第5行

char_line05=272'h00600C3003FFFC000000000000000080008018000000000000800080018003FFFE00, //第6行

char_line06=272'h1FFFFFF8000180007FFE7FF003C80380008018007C1F03C803800080018000000000, //第7行

char_line07=272'h00600C0000018000180E18180E3803800104301018040E3803800080018000000000, //第8行

char_line08=272'h00600C00000180001802180C080803800FFE30381804080803800080018000000000, //第9行

char_line09=272'h00600C000001800018031806180802800C0C7FF818041808028000FFFF8000000000, //第10行

char_line0a=272'h007FFC000001800018011806300406C00C0C60300C08300406C00080018000000000, //第11行

char_line0b=272'h00600C000001800018001806300404C00C0CC0300C08300404C00080018000000018, //第12行

char_line0c=272'h00600C000001801018081806200004C00C0C80300C08200004C0008001800000003C, //第13行

char_line0d=272'h007FFC000001803818081806600004C00C0D00300C08600004C0008001803FFFFFFE, //第14行

char_line0e=272'h00600C003FFFFFFC1818180C60000C600C0D4030061060000C6000FFFF8000018000, //第15行

char_line0f=272'h00600C10000180001FF81818600008600C0E20300610600008600080010000018000, //第16行

char_line10=272'h00600C380001800018181FF0600008600C0C10300610600008600008200000418000, //第17行

char_line11=272'h3FFFFFFC0001800018081800600008600FFC1830073060000860000C382000718800, //第18行

char_line12=272'h003208000001800018081800603F1FF00C0C18300320603F1FF0080C307000E18600, //第19行

char_line13=272'h00618C000001800018001800600C10300C0C0C300320600C10300C0C307000C18300, //第20行

char_line14=272'h00C106000001800018001800600C10300C0C08300320600C1030060C30C001818180, //第21行

char_line15=272'h018101C00001800018001800300C10300C0C003001C0300C1030030C30C0038180C0, //第22行

char_line16=272'h030104FC0001800018001800300C30300C0C003001C0300C3030038C318003018060, //第23行

char_line17=272'h0C010E380001800018001800180C20180C0C003001C0180C2018018C330006018070, //第24行

char_line18=272'h187FF0000001800018001800180C20180C0C003001C0180C2018018C36000C018038, //第25行

char_line19=272'h6001000000018000180018000C1060180C0C003000800C106018008C380018018038, //第26行

char_line1a=272'h00010000000180007E007E0003E0F83E0C0C0030008003E0F83E000C301010018010, //第27行

char_line1b=272'h00010000003F800000000000000000000FFC0C60000000000000000C303820738000, //第28行

char_line1c=272'h00010060000F800000000000000000000C0C03E00000000000001FFFFFFC001F8000, //第29行

char_line1d=272'h1FFFFFF00007000000000000000000000C0801C00000000000000000000000070000, //第30行

char_line1e=272'h00000000000000000000000000000000000000800000000000000000000000020000, //第31行

char_line1f=272'h00000000000000000000000000000000000000000000000000000000000000000000; //第32行

reg[8:0] char_bit;

always@(posedge CLK_to_DAC)

if(X==10'd144)char_bit<=9'd272; //当显示到144像素时准备开始输出图像数据

else if(X>10'd144&&X<10'd416) //左边距屏幕144像素到416像素时 416=144+272(图像宽度)

char_bit<=char_bit-1'b1; //倒着输出图像信息

reg[29:0] vga_rgb; //定义颜色缓存

always@(posedge CLK_to_DAC)

if(X>10'd144&&X<10'd416) //X控制图像的横向显示边界:左边距屏幕左边144像素 右边界距屏幕左边界416像素

begin case(Y) //Y控制图像的纵向显示边界:从距离屏幕顶部160像素开始显示第一行数据

10'd160:

if(char_line00[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; //如果该行有数据 则颜色为红色

else vga_rgb<=30'b0000000000_0000000000_0000000000; //否则为黑色

10'd162:

if(char_line01[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd163:

if(char_line02[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd164:

if(char_line03[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd165:

if(char_line04[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd166:

if(char_line05[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd167:

if(char_line06[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd168:

if(char_line07[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd169:

if(char_line08[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd170:

if(char_line09[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd171:

if(char_line0a[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd172:

if(char_line0b[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd173:

if(char_line0c[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd174:

if(char_line0d[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd175:

if(char_line0e[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd176:

if(char_line0f[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd177:

if(char_line10[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd178:

if(char_line11[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd179:

if(char_line12[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd180:

if(char_line13[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd181:

if(char_line14[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd182:

if(char_line15[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd183:

if(char_line16[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd184:

if(char_line17[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd185:

if(char_line18[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd186:

if(char_line19[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd187:

if(char_line1a[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd188:

if(char_line1b[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd189:

if(char_line1c[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd190:

if(char_line1d[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd191:

if(char_line1e[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd192:

if(char_line1f[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

default:vga_rgb<=30'h0000000000; //默认颜色黑色

endcase

end

else vga_rgb<=30'h000000000; //否则黑色

assign VGA_R=vga_rgb[23:16];

assign VGA_G=vga_rgb[15:8];

assign VGA_B=vga_rgb[7:0];

endmodule

4.点击保存按钮,更改文件名为:VGA_test.v

6.设置该文件置顶:Project→Set as Top-Level Entity ,然后编译

编译只要没有错误就可以了,警告不用管。

注意:如果是直接复制的代码,或者直接导入的项目,可能会出现版本不兼容问题,这时候我们需要更改配置文件里的版本,详细操作百度就可以了

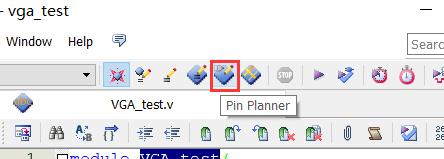

7.配置管脚

点击快捷按钮:Pin Planner

按照如下表所示配置管脚:

| Signal Name | FPGA Pin No. | Description | I/O Standard |

|---|---|---|---|

| OSC_50 | PIN_AG14 | 50 MHz clock input | 3.3 V |

| VGA_B[7] | PIN_D12 | VGA Blue[7] | 3.3 V |

| VGA_B[6] | PIN_D11 | VGA Blue[6] | 3.3 V |

| VGA_B[5] | PIN_C12 | VGA Blue[5] | 3.3 V |

| VGA_B[4] | PIN_A11 | VGA Blue[4] | 3.3 V |

| VGA_B[3] | PIN_B11 | VGA Blue[3] | 3.3 V |

| VGA_B[2] | PIN_C11 | VGA Blue[2] | 3.3 V |

| VGA_B[1] | PIN_A10 | VGA Blue[1] | 3.3 V |

| VGA_B[0] | PIN_B10 | VGA Blue[0] | 3.3 V |

| VGA_BLANK | PIN_F11 | VGA BLANK | 3.3 V |

| VGA_CLK | PIN_A12 | VGA Clock | 3.3 V |

| VGA_G[7] | PIN_C9 | VGA Green[7] | 3.3 V |

| VGA_G[6] | PIN_F10 | VGA Green[6] | 3.3 V |

| VGA_G[5] | PIN_B8 | VGA Green[5] | 3.3 V |

| VGA_G[4] | PIN_C8 | VGA Green[4] | 3.3 V |

| VGA_G[3] | PIN_H12 | VGA Green[3] | 3.3 V |

| VGA_G[2] | PIN_F8 | VGA Green[2] | 3.3 V |

| VGA_G[1] | PIN_G11 | VGA Green[1] | 3.3 V |

| VGA_G[0] | PIN_G8 | VGA Green[0] | 3.3 V |

| VGA_HS | PIN_G13 | VGA H_SYNC | 3.3 V |

| VGA_R[7] | PIN_H10 | VGA Red[7] | 3.3 V |

| VGA_R[6] | PIN_H8 | VGA Red[6] | 3.3 V |

| VGA_R[5] | PIN_J12 | VGA Red[5] | 3.3 V |

| VGA_R[4] | PIN_G10 | VGA Red[4] | 3.3 V |

| VGA_R[3] | PIN_F12 | VGA Red[3] | 3.3 V |

| VGA_R[2] | PIN_D10 | VGA Red[2] | 3.3 V |

| VGA_R[1] | PIN_E11 | VGA Red[1] | 3.3 V |

| VGA_R[0] | PIN_E12 | VGA Red[0] | 3.3 V |

| VGA_SYNC | PIN_C10 | VGA SYNC | 3.3 V |

| VGA_VS | PIN_C13 | VGA V_SYNC | 3.3 V |

8.连接DE2-115 开发板

这里就不附上图片了,主要是实验的时候没有拍照

主要是要配置安装USB-Blaster 驱动,否则就会出问题

这里请参考:https://blog.csdn.net/ssj925319/article/details/115333028

板子连接好后就可以烧录了

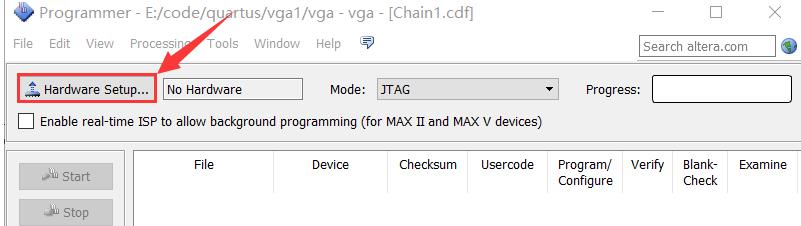

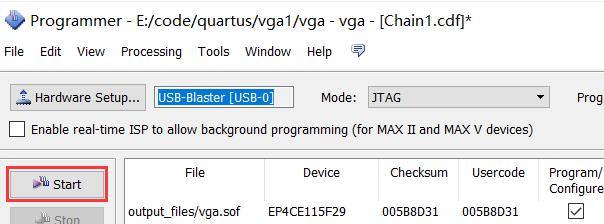

烧录程序

点击Programmer快捷键

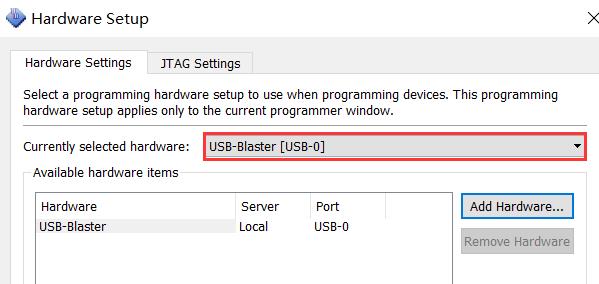

出现如下图界面,点击Hardware Setup…

这里有可能会出现找不到设备的情况,就是因为没有装驱动

选择 USB-Blaster [USB-0],然后Close

添加文件

在 output_files 下找到 .sof 文件,并打开它

点击Start开始下载到开发板上

显示器显示如下

.

.总结:

在做这个实验的时候,环境的配置是很重要的,其中电脑的用户名要是英文的,这样它的路径才不会有中文。一开始我的电脑用户名就是中文,导致后面很多错误出现的莫名奇妙。无奈只好用虚拟机,这下又出现了没有装那个驱动的问题,反正就很烦。最后实在忍不了了,就重装了电脑。。。

.

.

参考:使用 FPGA 开发板采用 Verilog 编程练习基于 VGA 图像显示

以上是关于verilog编程技巧的主要内容,如果未能解决你的问题,请参考以下文章