关于使用FFT ip核 V8.0版

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了关于使用FFT ip核 V8.0版相关的知识,希望对你有一定的参考价值。

问题1:FFT ip核的输入有 实部和虚部 之分,但实际工作中的信号是否大多 只有实部?这样以来在给输入时,虚部输入始终为0?实部的输入由AD采样实际信号后供给?

问题2:FFT ip核的输入输出都是带符号位的数据??是补码的形式??

问题3:FFT ip核 V8.0版是基于DIF的,输入数据是自然顺序,那输出呢??

原则上如果不是解析信号,即信号只有实部或者虚部的话,如果只有实部,虚部为0,频谱应当关于y轴对称,如果只有虚部,实部为0,那么频域是关于零点对称。如果是解析信号的话,那么频谱是不对称的。

上面说的对称是在数学上分析上是正确的,但在实际的运用中存在一个fft移位的问题。也就是说如果用matlab或者quartus运算fft的话,那么如果不做fft移位的话,那么频率数值上将不会出现负频率,也就是N点fft出现的结果数据是从0~n-1个频点的,没有负数,自然也就部会出现关于y轴或者零点对称。

这种结果本身并没有问题,如果你认为错了,那么说明你没有理解fft。做N点fft的话,0~N/2-1是正频率,N/2~N是负频率。所以如果不进行fft移位的话,非解析信号他们的频谱应当是关于N/2点对称或者反对称的。在matlab中可以用fftshift进行移位,在FPGA中就没有这个必要了,知道了数据的含义直接用就可以,移位浪费时间,没有必要。

在Quartus 的FFT IP核中,是一个时钟输出一个数据点,所以从source_sop开始,对应的是数据流的顺序就是你的频率点,但它是按时间顺序输出的,不需要将横坐标专门设置。

这也是最基本的时频分析的基础。 参考技术A 感觉不是很对啊fft

probe

可以吗,怎么使用,坐等楼下解决。

关于ALTERA生成IP核卡住

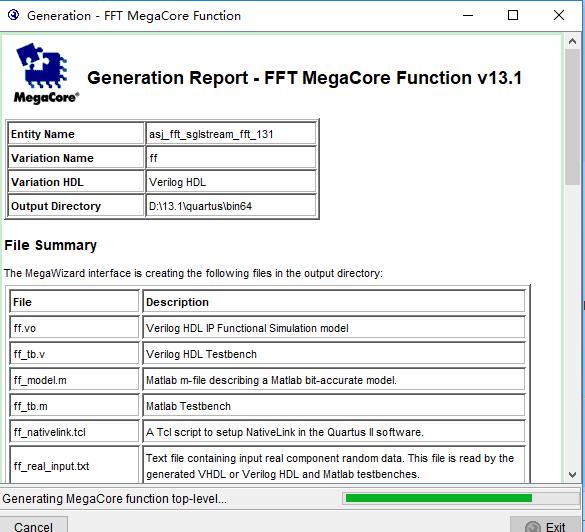

最近搞fft,用的quartus13.1版本,发现quartus和modelism存在各种各样的坑啊,fftIP核大家可能也遇到过ip核

生成到一半就卡住的问题,之前我是通过换系统解决的,但是好景不长,windos自己补了几个补丁之后,IP核又

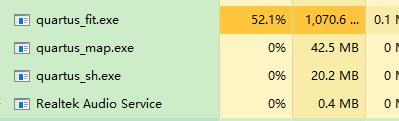

没法用了,其实还有一种方法,就是再fft生成的过程,打开任务管理器,把quartus_map进程给关掉,之后ip核就

可以顺利生成了,可能关掉之后少了部分文件,但是不影响最后结果,我已经下板运行过了。

以上是关于关于使用FFT ip核 V8.0版的主要内容,如果未能解决你的问题,请参考以下文章