lattice ram ip怎么用

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了lattice ram ip怎么用相关的知识,希望对你有一定的参考价值。

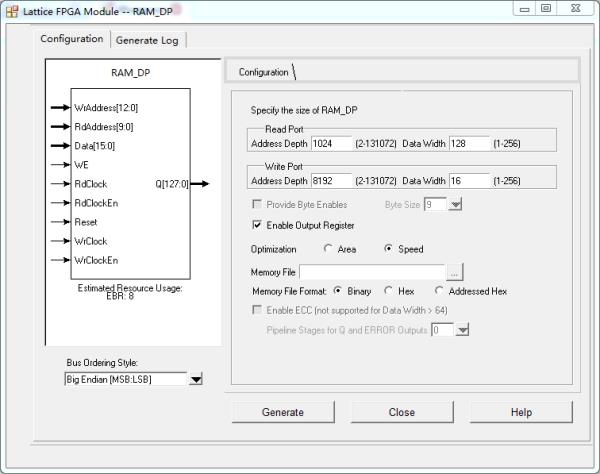

1、建立ip会把,如下设置也行,深度X位宽 代表存储的大小,ram的特点是,通过地址读取。wraddress,在输出。

2、在top文件中,把输入输出分别列出来,通过wire的括号内的变量连接到其它模块中。

vid_rx_ram(

.WrClock(111),

.WrClockEn(000),

.WrAddress(222),

.Data(333),

.WE(444),

.RdClock(555),

.RdClockEn(666),

.RdAddress(777),

.Q(888),

.Reset(~rst_n)

);

参考技术A 你可以把需要下载的IP核说出来,请别人帮你下载,这样直接用别人的账号,我觉得不会有多少人愿意借你用的。ram自己写?用IP?

前言

ram这种东西,可以用ip方便,也可以自己写代码描述它。

以下讨论单口ram;8bit*256

流程

1.IP:

使用IP当然是最方便的事情啦,但可移植性差而且可定制性较差。

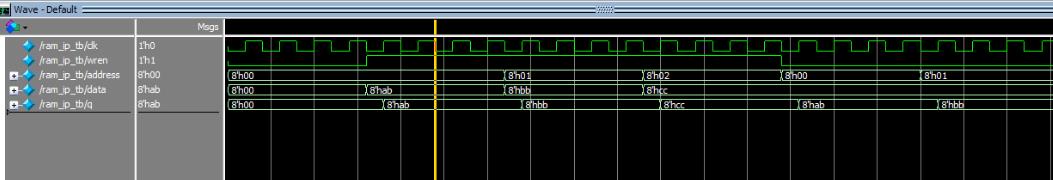

仿真波形:

2.Verilog描述:

描述就得自己写自己调试代码了,不过写好就是一劳永逸啦。。。

开始写了第一版代码:

1 //************************************************ 2 // Filename : ram.v 3 // Author : Kingstacker 4 // Company : School 5 // Email : kingstacker_work@163.com 6 // Device : Altera cyclone4 ep4ce6f17c8 7 // Description : 8bit*256 ram 8 //************************************************ 9 module ram #( parameter DATA_WIDTH = 8,DEPTH = 256,ADDR_WIDTH = 8)( 10 //input; 11 input wire clk, 12 input wire wren, //write high enable; 13 input wire [ADDR_WIDTH-1:0] address, 14 input wire [DATA_WIDTH-1:0] data, 15 //output; 16 output reg [DATA_WIDTH-1:0] q 17 ); 18 reg [DATA_WIDTH-1:0] memory[0:DEPTH-1]; 19 //read; 20 always @(posedge clk ) begin 21 q <= memory[address]; 22 end //always 23 //write; 24 always @(posedge clk ) begin 25 if(wren) begin 26 memory[address] <= data; 27 end 28 end //always 29 endmodule

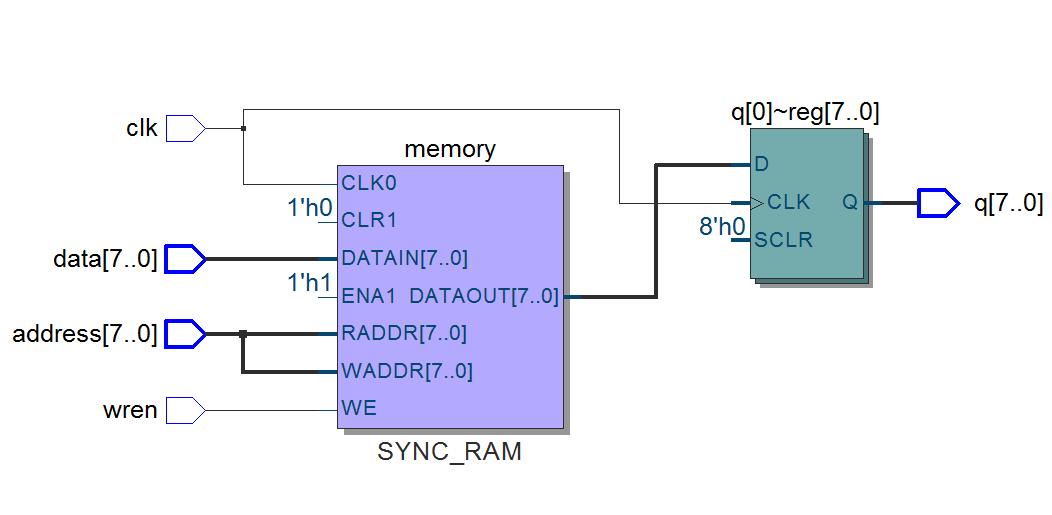

综合RTL:

仿真波形:读写同时的时候会有冲突导致xx。

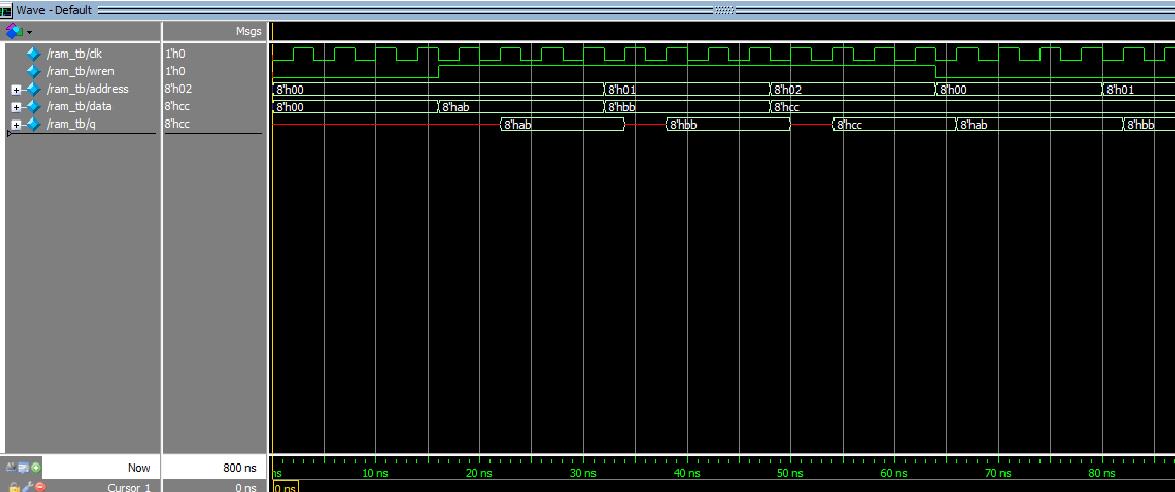

第二版代码:地址寄存一拍。

1 //************************************************ 2 // Filename : ram.v 3 // Author : Kingstacker 4 // Company : School 5 // Email : kingstacker_work@163.com 6 // Device : Altera cyclone4 ep4ce6f17c8 7 // Description : 8bit*256 ram 8 //************************************************ 9 module ram #( parameter DATA_WIDTH = 8,DEPTH = 256,ADDR_WIDTH = 8)( 10 //input; 11 input wire clk, 12 input wire wren, //write high enable; 13 input wire [ADDR_WIDTH-1:0] address, 14 input wire [DATA_WIDTH-1:0] data, 15 //output; 16 output wire [DATA_WIDTH-1:0] q 17 ); 18 reg [DATA_WIDTH-1:0] memory[0:DEPTH-1]; 19 reg [ADDR_WIDTH-1:0] address_reg; 20 //read; 21 always @(posedge clk ) begin 22 address_reg <= address; 23 end //always 24 assign q = memory[address_reg]; 25 //write; 26 always @(posedge clk ) begin 27 if(wren) begin 28 memory[address] <= data; 29 end 30 end //always 31 32 endmodule

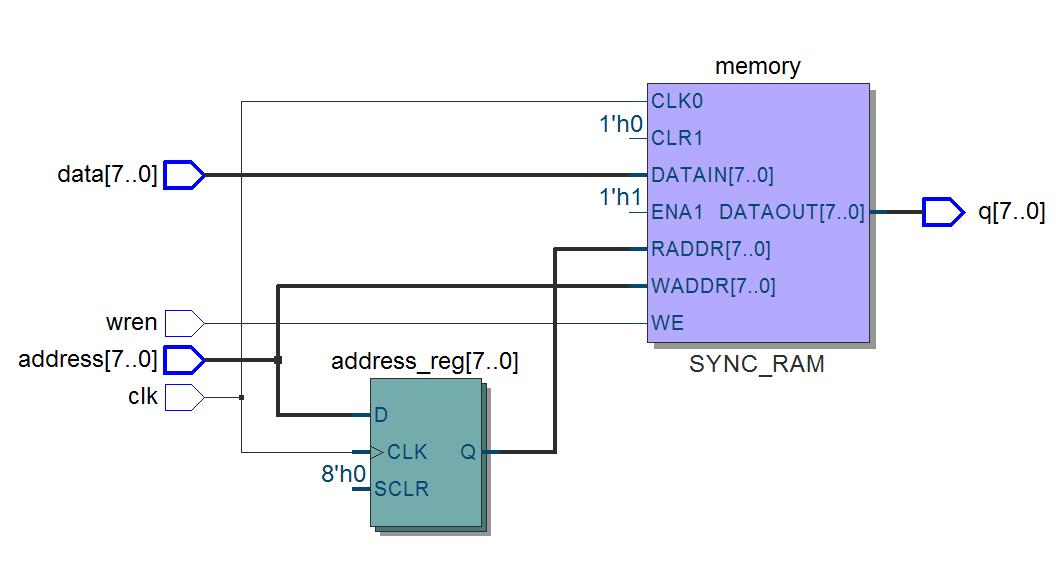

综合rtl:

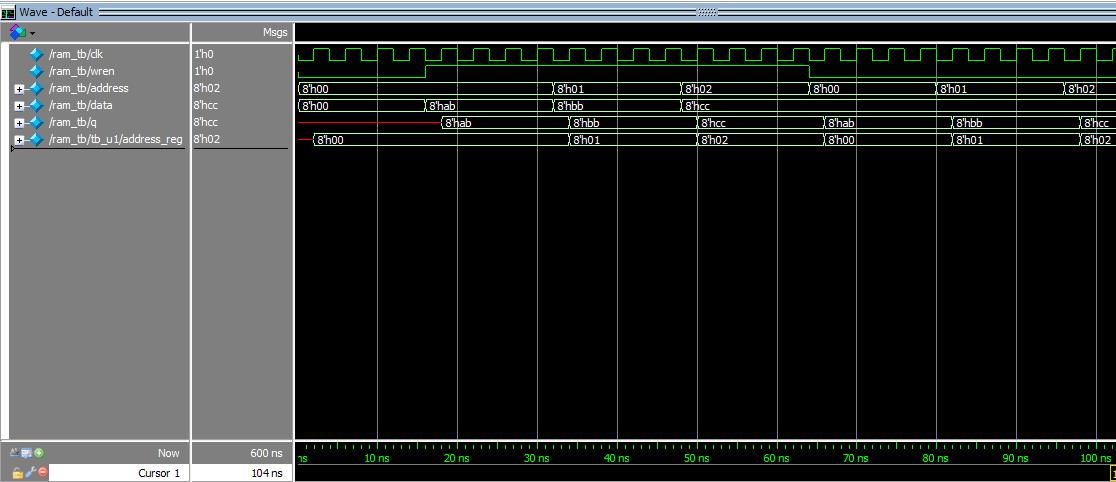

仿真波形:

以上。

以上是关于lattice ram ip怎么用的主要内容,如果未能解决你的问题,请参考以下文章