存储器层次结构

Posted the_scent_of_th_soul

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了存储器层次结构相关的知识,希望对你有一定的参考价值。

接着上次简单的介绍,让我们来继续讨论这些“存储器们”吧。

在上一篇中我提到了传统的DRAM,简单描述了每个DRAM芯片与存储控制器的“交互”过程。下面,我们来看一下多个DRAM芯片是怎样集合在一起工作的。

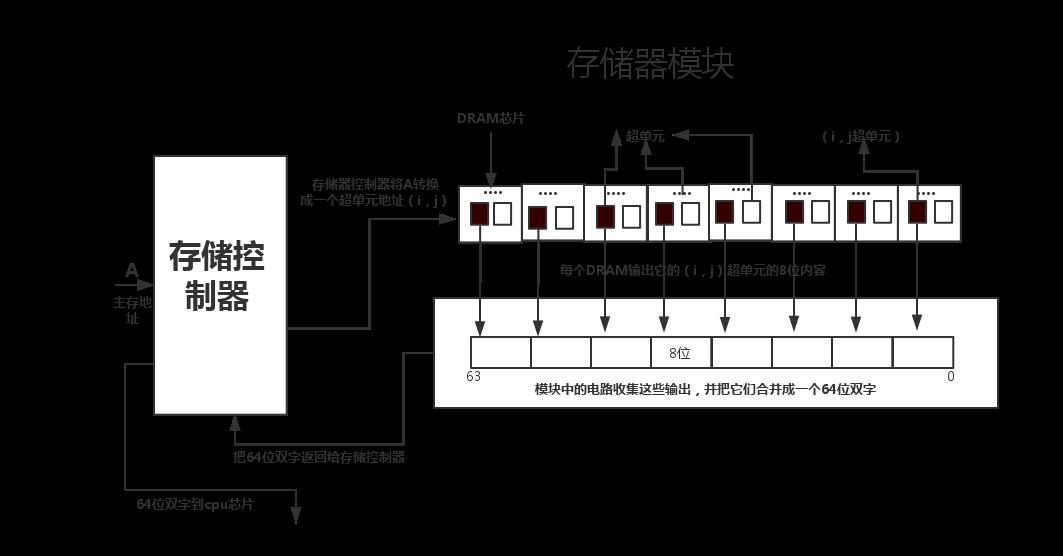

存储器模块:

DRAM 芯片包装在存储器模块中,这个存储器模块是插到主板的扩展槽上的。常见的包装包括168个引脚的双列直插存储器模块(DIMM),它以64位为块传送数据到存储控制器和从存储控制器传出数据,还包括72个引脚的单列直插存储器模块(SIMM),它以32位为块儿传送数据。

为了展示一个存储器模块的基本思想,用一个 8个64Mbit的DRAM芯片的模块做示例,我简单做了一个过程图,如下:

在这里,每个超单元存储主存的一个字节,而用相应超单元为(i,j)的8个超单元来表示主存中字节地址A处的64位双字。

要取出存储器地址A处的一个64位双字,存储控制器将A转换成一个超单元地址(i,j),并将它发送到存储器模块,然后存储器模块再将i和j广播到每个DRAM。作为响应,每个DRAM输出它的(i,j)超单元的8位内容。模块中的电路收集这些输出,并把它们合成一个64位双字,再返回给存储控制器。

另外,通过将多个存储器模块连接到存储控制器,能够聚合主存。在这种情况下,当控制器收到一个地址A时,控制器先选择包含A的模块k,将A转换成它的(i,j)形式,并将(i,j)发送到模块k。

下面,我们来看几个增强的DRAM:

快页模式 DRAM(FPM DRAM):

传统的DRAM将超单元的一整行拷贝到它的内部行缓冲区,使用一个然后丢弃其余的。而FPM DRAM允许对同一行连续地访问,可以直接地从缓冲区得到服务。例如,要从传统DRAM的同一行中读取四个超单元,则存储控制器必须重复发四个RAS/CAS请求,即使行地址i在每个情况中都是一样的。而要从一个FPM DRAM的同一行读取四个超单元,存储器发送第一个RAS/CAS,后面跟三个CAS请求。也就是一个RAS四个CAS。第一个超单元和传统的一样,剩下的三个,只需要根据CAS在行缓冲区获得就行了。显然获得剩下的三个超单元比获取第一个快。

同步DRAM(S DRAM):

像传统DRAM、FPM DRAM 等都是异步的DRAM,相之下,S DRAM 能够比它们更快地输出超单元的内容。

好了,对随机访问存储器(RAM)的简单介绍我们就先进行到这里,下面我们来看一些其他的存储器:

非易失性存储器:

如果断电,DRAM和SRAM会丢失它们的信息,从这个意义上说,它们是易失的。而非易失性存储器是即使在断电后,也仍然保存着它的信息。现在有很多种非易失性存储器。

我们先来看一种常见的非易失性存储器 ROM:

虽然ROM中有的类型既可以读也可以写,但是它们整体上都称为只读存储器。ROM是以它们能够被重写的次数和对它们重写所用的机制来区分的。

常见的ROM 有以下几种:

PROM(可编程ROM):

只能被写一次,PROM的每个存储器单元有一种熔丝,它只能用高电流熔断一次。

可擦可写ROM(EPROM):

有一个透明的石英窗口,允许光达到存储单元。紫外线光照射过窗口,EPROM单元就被清零。对EPROM编程是通过使用一种把1写入EPROM的特殊设备来完成的。EPROM能够被擦除和重编的次数的数量级可以达到1000次。

EEPROM(电子可擦除ROM):能够被编程的次数达到100000。

存储在ROM设备中的程序通常称为固件。当一个计算机系统通电后,它会运行存储在ROM中的固件。PC上的Bios(基本输入/输出系统)的例程就在固件中。还有一些复杂设备,如图形卡和驱动控制器,也依赖固件翻译来自CPU的I/O请求。

总线:

下面我们来先引入一个总线的概念,首先,总线到底是什么?它在计算机系统中又扮演着一个什么样的角色呢?

总线 是贯穿整个系统中的一组电子管道,它携带信息字节并负责在各个部件间传递。也可以说,总线是一组并行的导线,能携带地址、数据和控制信号。通常总线被设计成传送定长的字节块(字)。每个I/O设备都通过一个控制器或适配器与总线相连。

控制器:控制器是置于I/O设备本身的或者系统的主印制电路板(通常称为主板)上的芯片组。

适配器:适配器是一块插在主板插槽上的卡。

控制器和适配器的功能都是在I/O总线和I/O设备之间传递信息。

既然提到这里,就顺便介绍一下主存吧。

主存:主存是一个临时存储设备,在处理器执行程序时,用来存放程序和程序处理的数据。从物理上来说,主存是由一组动态随机存储器(DRAM)芯片组成。

访问主存:

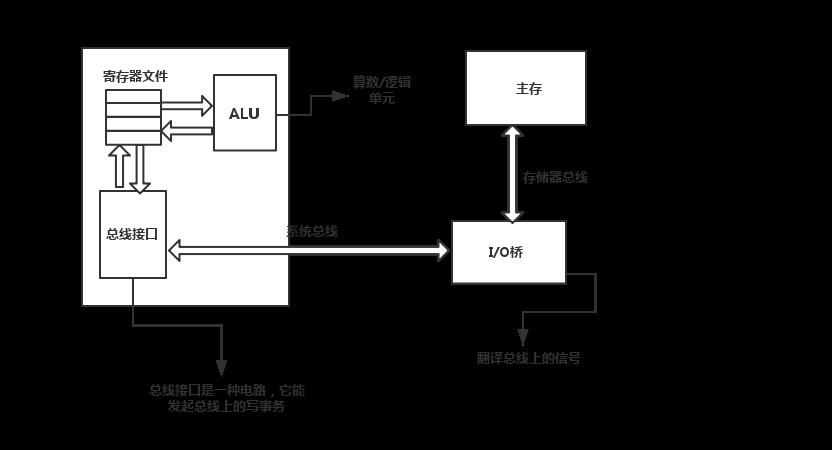

我们先来看一个简单的主存访问模型图:

数据流通过总线的共享电子电路在处理器和DRAM主存之间来来回回。

从主存传送数据到CPU的过程叫做读事务,从CPU传送数据到主存的过程叫做写事务。着一系列传送数据的步骤称为总线事务。

系统总线:连接CPU和I/O桥。

存储器总线:连接I/O桥和主存。

I/O桥:将系统总线的电子信号翻译成存储器总线的电子信号 和将存储器总线信号翻译成系统总线信号。

后面我们将会介绍,I/O桥也将系统总线和存储器总线连接到I/O总线。像磁盘和图形卡这样的I/O设备共享I/O总线。

下面,我们来看一个典型的连接CPU和主存的总线结构图:

根据这个简单的模型图,我们来简单描述一下读事务和写事务的大致过程:

读事务:

当要从内存中读数据到CPU时,假设这里的地址是A,那么读事务的目标就是把A的内容加载到寄存器文件中。

可简单分为四个步骤:

CPU把地址放到系统总线,I/O桥将信号传递到存储器总线。

主存感受到存储器总线上的信号,从存储器总线上读出地址A,从DRAM中的地址A处

(存储控制器地址A转换成超单元地址)取出数据字,放到存储器总线上。

I/O桥将存储器总信号翻译成系统总信号传递给系统总线。

CPU感觉到系统总线上的数据,从总线上读出数据,并拷贝到寄存器文件中。写事务:

和上面的读相逆,这里,寄存器文件的内容被写到地址A,CPU发起写事务。

首先,CPU将地址放到系统总线上。传递给存储器总线。

存储器从存储器总线读出地址,并等待数据到达。

CPU将数据字拷贝到系统总线,传递给存储器总线。

主存从存储器总线读出数据字,并将这些位存储到DRAM中。好了,这里插入的一点关于硬件过程的描述就先到这里。

下一次,我们来具体详细地讨论磁盘的基本构造以及存储方式。

以上是关于存储器层次结构的主要内容,如果未能解决你的问题,请参考以下文章