数字电路基础知识|时钟和时序

Posted IC观察者

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了数字电路基础知识|时钟和时序相关的知识,希望对你有一定的参考价值。

时钟的概念

时钟对数字电路而言非常重要,没有时钟数字电路就没法工作,其全称是时钟频率,一般由晶振来提供时钟频率。

在数字电路中,所有数据、逻辑单元等状态的更新都是以时钟为基础的,时钟频率在数字电路中起着同步的作用。数字芯片的datasheet都有芯片的时序图,该时序图表明了数据应该在什么时候写入、读出以及状态发生变化。只有当同步信号到达时,相关的触发器才会按输入信号相应的改变输出状态,实现数字电路的功能。

时钟源

根据时钟源在数字设计模块中位置的不同,可以将时钟源分为外部时钟源和内部时钟源。

外部时钟源:

RC/LC 振荡电路:利用正反馈或负反馈电路产生周期性变化时钟信号。此类时钟源电路简单,频率变化范围大,但工作频率较低,稳定度不高。

无源/有源晶体振荡器:利用石英晶体的压电效应(压力和电信号可以相互转换)产生谐振信号。此类时钟源频率精度高,稳定性好,噪声低,温漂小。有源晶振中,往往还加入了压控或温度补偿,时钟的相位和频率都有较好的特性。但电路实现相对复杂,频带较窄,频率基本不能调节。

内部时钟源:

锁相环(PLL, Phase Locked Loop):

利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,通过反馈通路将信号倍频到一个较高的固定频率。

时钟存储单元

稍微复杂的数字设计都离不开时钟。时钟也是所有时序逻辑建立的基础。

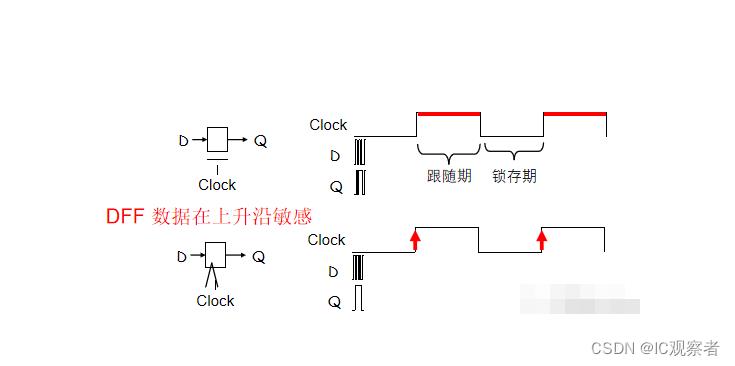

Latch 存储器,数据在时钟高电位时敏感

建立时间、保持时间和传播时间

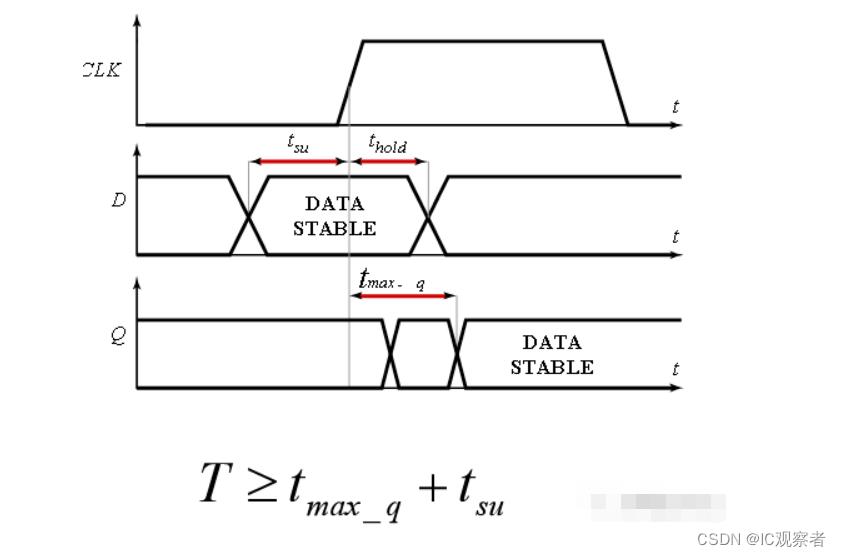

建立时间就是时钟触发事件来临之前,数据需要保持稳定的最小时间,以便数据能够被时钟正确的采样。

保持时间就是时钟触发事件来临之后,数据需要保持稳定的最小时间,以便数据能够被电路准确的传输。

可以通俗的理解为:时钟到来之前,数据需要提前准备好;时钟到来之后,数据还要稳定一段时间。建立时间和保持时间组成了数据稳定的窗口。

更多数电干货查看:IC修真院知识问答

以上就是给大家分享的“数字电路基础知识|时钟和时序”内容,欢迎评论和留言。

以上是关于数字电路基础知识|时钟和时序的主要内容,如果未能解决你的问题,请参考以下文章