关于xilinx中ddr3仿真出现tRFC maximum violation during No Op问题记录

Posted 芯青年0

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了关于xilinx中ddr3仿真出现tRFC maximum violation during No Op问题记录相关的知识,希望对你有一定的参考价值。

文章目录

1.问题描述

在日常的FPGA开发中,ddr常用于对大量数据的存储,在对ddr的仿真过程中,常采用的是官方提供的ddr3_model.sv模块,简单方便。前段时间采用其进行仿真时,出现了app_rdy在进行短暂的读取数据后,一直置低,并且信息窗口报错如下

因为这个问题卡了我好多天,一直得不到解决,后面直接放下,转而去解决其他问题了,近来项目整合,不得不解决问题。于是乎到处问,最后得到一位南理工的同行指点,才算是解决了问题,特此记录在此,给后人排坑。

2.解决方案

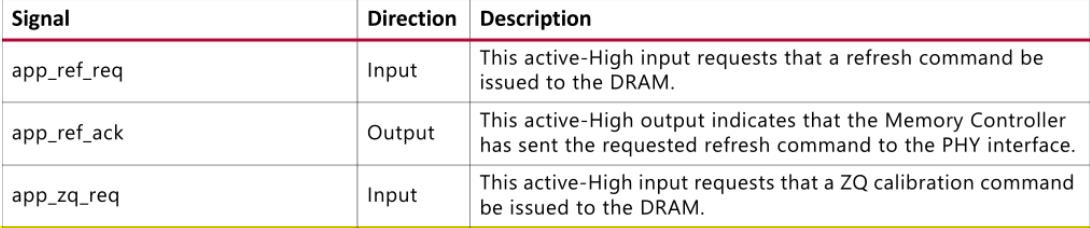

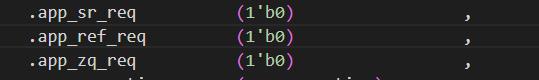

给MIG模块的输入信号app_sr_req置零,其在官方的说明如下

除了app_sr_req信号常会被忽略,还有app_ref_req和app_zq_req信号也常会被忽略,最好也给这两个信号置零

以上是关于关于xilinx中ddr3仿真出现tRFC maximum violation during No Op问题记录的主要内容,如果未能解决你的问题,请参考以下文章