时序检查(上)

Posted KuoGavin

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了时序检查(上)相关的知识,希望对你有一定的参考价值。

文章目录

本章节将介绍静态时序分析所执行的一部分检查,这些检查旨在详尽地验证待分析设计的时序。

- 两项主要的检查是建立时间和保持时间检查。一旦在触发器的时钟引脚上定义了时钟,便会自动推断出该触发器的建立时间和保持时间检查。时序检查通常会在多个条件下执行,包括最差情况的慢速条件和最佳情况的快速条件。通常,最差情况的慢速条件对于建立时间检查很关键,而最佳情况的快速条件对于保持时间检查很关键(尽管也可以在最差情况的慢速条件下执行保持时间检查)。

- 本章节中的示例假定网络延迟为零,这样做是为了简化说明,并且不会更改所介绍的概念。

8.1 建立时间检查(Setup Timing Check)

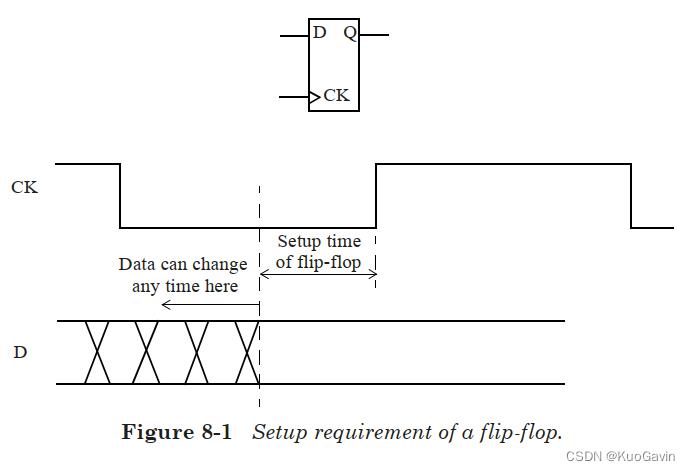

建立时间检查会验证触发器时钟和数据引脚之间的时序关系,从而满足建立时间要求。换句话说,建立时间检查会确保在触发器输入时钟之前,数据在触发器的输入端可用。在时钟的有效沿到达触发器之前,数据应在一定时间内保持稳定,即触发器建立时间,该要求将确保数据可靠地被捕获到触发器中。图8-1展示了典型触发器的建立时间要求,建立时间检查将验证触发器的建立时间要求。

通常,有一个发起触发器(用于发起数据的触发器)和捕获触发器(用于捕获数据的触发器),这个捕获触发器的建立时间要求必须满足。建立时间检查将验证从发起触发器到捕获触发器的最长(最大)路径,这两个触发器的时钟可以相同也可以不同。建立时间检查是从发起触发器中时钟的第一个有效沿到捕获触发器中时钟后面最接近的那个有效沿。建立时间检查将确保上一个时钟周期发起的数据准备好在一个周期后被捕获。

现在研究一个简单示例,如图8-2所示,其中发起触发器和捕获触发器具有相同的时钟。时钟 C L K M CLKM CLKM的第一个上升沿在 T l a u n c h T_launch Tlaunch时间后出现在发起触发器的时钟引脚上,由该时钟沿发起的数据出现在触发器 U F F 1 UFF1 UFF1的 D D D引脚的所需时间为 T l a u n c h + T c k 2 q + T d p T_launch+T_ck2q+T_dp Tlaunch+Tck2q+Tdp。时钟 C L K M CLKM CLKM的第二个上升沿(通常在一个周期后检查建立时间)出现在捕获触发器 U F F 1 UFF1 UFF1的时钟引脚上的时间为 T c y c l e + T c a p t u r e T_cycle+T_capture Tcycle+Tcapture。这两个时间之差必须大于触发器 U F F 1 UFF1 UFF1的建立时间要求,以确保触发器 U F F 1 UFF1 UFF1可靠地捕获数据。

建立时间检查可以数学表达为:

T l a u n c h + T c k 2 q + T d p < T c a p t u r e + T c y c l e − T s e t u p T_launch+T_ck2q+T_dp < T_capture+T_cycle-T_setup Tlaunch+Tck2q+Tdp<Tcapture+Tcycle−Tsetup

( E r r o r Error Error) 建立时间检查的要求也即是: T s e t u p < ( T c a p t u r e + T c y c l e ) − ( T l a u n c h + T c k 2 q + T d p ) T_setup < (T_capture+T_cycle)- (T_launch+T_ck2q+T_dp ) Tsetup<(Tcapture+Tcycle)−(Tlaunch+Tck2q+Tdp)

(

C

o

r

r

e

c

t

Correct

Correct) (上面不对。因为

T

s

e

t

u

p

T_setup

Tsetup是要求,而不是实际时间,应该是

a

r

r

i

v

a

l

t

i

m

e

=

T

l

a

u

n

c

h

+

T

c

l

k

2

q

+

T

d

p

arrival\\, time=T_launch+T_clk2q+T_dp

arrivaltime=Tlaunch+Tclk2q+Tdp要小于

r

e

q

u

i

r

e

d

t

i

m

e

=

T

c

a

p

t

u

r

e

+

T

c

y

c

l

e

−

T

s

e

t

u

p

required\\,time=T_capture+T_cycle-T_setup

requiredtime=Tcapture+Tcycle−Tsetup才能满足建立时间约束,而最晚到达时间

m

a

x

a

r

r

i

v

a

l

t

i

m

e

max\\arrival\\, time\\

maxarrivaltime能够满足上述条件,则全部能够满足,所以总是使用最慢工艺角/max来进行检查。而裕量则是

s

l

a

c

k

=

r

e

q

u

i

r

e

d

t

i

m

e

−

a

r

r

i

v

a

l

t

i

m

e

=

(

T

c

a

p

t

u

r

e

+

T

c

y

c

l

e

−

T

s

e

t

u

p

)

−

(

T

l

a

u

n

c

h

+

T

c

l

k

2

q

+

T

d

p

)

slack=required\\, time-arrival\\, time = (T_capture+T_cycle-T_setup)-(T_launch+T_clk2q+T_dp)

slack=requiredtime−arrivaltime=(Tcapture+Tcycle−Tsetup)−(Tlaunch+Tclk2q+Tdp),且根据以上分析,在进行优化时多对

T

d

p

T_dp

Tdp也就是组合逻辑部分进行delay的优化,使其变小一些。

其中 T l a u n c h T_launch Tlaunch是发起触发器 U F F 0 UFF0 UFF0的时钟树延迟, T d p T_dp Tdp是组合逻辑数据路径的延迟, T c y c l e T_cycle Tcycle是时钟周期, T c a p t u r e T_capture T以上是关于时序检查(上)的主要内容,如果未能解决你的问题,请参考以下文章