求一个fpga高速信号采集设计方案

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了求一个fpga高速信号采集设计方案相关的知识,希望对你有一定的参考价值。

马上做毕业设计,课题是做fpga高速信号的采集,采样率100M,请高手给个大概方案,或者工作框图,我只做采集部分,也就是ad转换,然后给fpga,至于后面的数据处理不用做,谢谢大家

网上有方案是将转换后的数字信号给fpga后,还要通过一个fifo或者sram是怎么回事,如果是低速信号是不是就不用fifo模块了?还有就是高速信号的pcb布线应该注意什么?谢谢

IP核1、控制ADC自动高速转换的状态机。其作用是实现高速100M的信号采样,就是一个循环的时序控制,让ADC转换一次完成之后由FPGA读出数据并将数据交由第二个IP核(FIFO缓存控制IP),然后立刻读取第二次数据。但是需要注意ADC芯片的选择,器转换速率必须要高于100MHZ。

IP核2、FIFO缓存控制核:如果说想要实现采集数据的高可靠性和稳定性的话,FIFO一般来说是必须存在的。FIFO的IP核判断ADC一次采样是否结束,如果结束,将数据存在FIFO的缓存区1。然后在第二次采样的时候让IP核3将缓存区1的数据读走然后清空缓存区1的数据,并同时将第二次读到的采样数据存进缓存区2,然后又将第二次读的数据让IP核3从缓存区2读走,同时ADC采样并存数据到缓存区1。(也就是说,FIFO分为两个缓存区,总是一个用来存储ADC转换后的数据,另一个用来让后面的功能模块读出上一次采样到的数据。两个是同时的。缓存区1和缓存区2交替工作。)

IP核3:处理数字信号的功能模块。你说到了你的任务是ADC转换这一块,所以IP核3你只需要交替读出FIFO两个缓存区的数据就OK。

回答你的补充问题:

1.低速是不是不需要FIFO模块?

答:FIFO其实无论是高速还是低速都可以省掉,只是为了系统的稳定性和采样速率的稳定性、采集数据的高可靠性所以次啊加的FIFO缓存器。

2.高速信号PCB布线应注意什么?

答:

1.电源滤波一定要做好,否则有纹波。

2.正电源(VCC)的所有线路最好用两根地线(GND)将它夹在中间,(如果整个板子都铺铜,这个可以不考虑)。

3.双面板需要将正反两面的走线方向垂直,可以减小EMC。

4.模拟电源和数字电源分开,地也一样。整个板子上的数字电源和模拟电源用两个个0欧电阻连接。(1个电源正,一个地)

5.最好铺铜。追问

肯定是做这方面的高手,留个qq请教下行不?完了我请吃饭,呵呵

追答185732552,两年前做过这个,技术交流。楼主说话要算数啊,我可饿着肚子在回答问题哦!呵呵呵!!!

参考技术A 视频VGA信号-->AD9888把模拟信号转换为RGB数字信号-->FPGA采集把数据送到芯片的FIFO里面-->从FIFO里面读取数据-->送到sram里面-->缓存了一整幅图像-->从sram里面读出图像处理要注意信号的完整性,电磁兼容性啊大了去了,比如说串扰,敷铜接地,对布局布线,哪怕是退偶电容的位置都有关的

基于OMAPL138 +FPGA 48通道采集器的设计与实现

当今局势下,世界人口形势进一步加剧,由于陆地资源和环境的压力,海洋客观上已成为世界后备资源基地及某些主要战略资源的接替区。人类为了更加深入的探索海洋,在水声领域引入数字信号、图像处理技术制造出各种新型声呐基阵。

本论文根据48元声呐基阵声电信号转换后的记录需求设计了一套数据采集器,内容包括采集器的总体方案设计、硬件电路设计和软件程序设计。该数据采集器以FPGA和OMAP-L138处理器为控制核心。在核心控制器完成设计之后,采用6片多路高精度模数转换芯片同步采集48个通道方向上的声电转换信号。为了保证多套系统在水下协同工作设计同步器模块配合实现时间管理,保证所有系统开始采集时刻都为绝对整点时刻。采用大容量SATA硬盘以同步器模块提供的时间信息为名称对采集完成的数据进行存储,为后续的数据处理提供方便,也为检测现场数据的实时性和可靠性提供了支持。在实验室中,对采集器要实现的功能进行了验证,并从多个方面对系统性能进行了检测。经过实际检测,本文设计的数据采集器的功能和实时性能指标符合预期设想,采集存储的数据准确有效,采集器可以投入使用。最后,为了进一步确定采集器的稳定性,项目团队分别在水池和三亚海域进行了外场实验,实验的成功完成证明了采集器工作稳定。

1 评估板简介

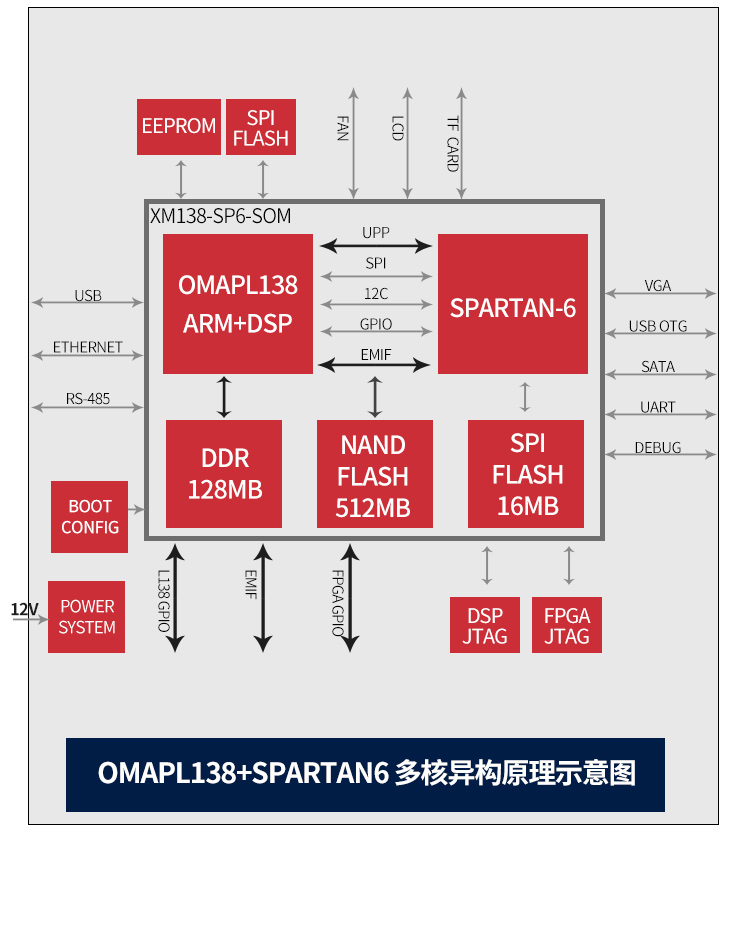

基于TI OMAP-L138(定点/浮点 DSP C674x+ARM9)+ Xilinx Spartan-6 FPGA处理器;

OMAP-L138 FPGA 通过uPP、EMIFA、I2C总线连接,通信速度可高达 228MByte/s;OMAP-L138主频456MHz,高达3648MIPS和2746MFLOPS的运算能力;

FPGA 兼容 Xilinx Spartan-6 XC6SLX9/16/25/45,平台升级能力强;

开发板引出丰富的外设,包含千兆网口、SATA、EMIFA、uPP、USB 2.0 等高速数据传输接口,同时也引出 GPIO、I2C、RS232、PWM、McBSP 等常见接口;

通过高低温测试认证,适合各种恶劣的工作环境;

DSP+ARM+FPGA三核核心板,尺寸为 66mm*38.6mm,采用工业级B2B连接器,保证信号完整性; Ø

支持裸机、SYS/BIOS 操作系统、Linux 操作系统。

图1 开发板正面和侧视图

XM138F-IDK-V3.0 是一款基于深圳信迈XM138-SP6-SOM核心板设计的开发板,采用沉金无铅工艺的4层板设计,它为用户提供了 XM138-SP6-SOM核心板的测试平台,用于快速评估XM138-SP6-SOM核心板的整体性能。

XM138-SP6-SOM引出CPU全部资源信号引脚,二次开发极其容易,客户只需要专注上层应用,大大降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。不仅提供丰富的 Demo 程序,还提供详细的开发教程,全面的技术支持,协助客户进行底板设计、调试以及软件开发。

2 典型运用领域

数据采集处理显示系统

智能电力系统

图像处理设备

高精度仪器仪表

中高端数控系统

通信设备

音视频数据处理

图2 典型应用领域

3 软硬件参数

开发板外设资源框图示意图

图3 开发板接口示意图

图4 开发板接口示意图

以上是关于求一个fpga高速信号采集设计方案的主要内容,如果未能解决你的问题,请参考以下文章