从零开始学习 UVM10.9UVM TLM —— TLM Analysis Port

Posted ReRrain

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了从零开始学习 UVM10.9UVM TLM —— TLM Analysis Port相关的知识,希望对你有一定的参考价值。

文章目录

我们之前看到的put/get通信通常需要相应的export提供实现。拥有analysis port的想法是,像监视器这样的组件应该能够生成一系列事务流,而不管是否实际连接了目标。

uvm_analysis_port是一种基于TLM的专用类,其接口由一个名为write()的函数组成,并可以嵌入到任何组件中,如下面的代码片段所示。该端口包含连接到它上面的analysis export列表。当组件(my_monitor)调用analysis_port.write()时,它基本上会循环遍历列表并调用每个连接export的write()方法。如果没有任何东西连接到它上面,则不执行任何操作。

class my_monitor extends uvm_component;

..UVM中的class

UVM中的类包括:基类(base)------------uvm_void/uvm_object/uvm_transaction/uvm_root/uvm_phase/uvm_port_base

报告(reporting)--------uvm_report_object/uvm_report_handler/uvm_report_server/uvm_report_catcher

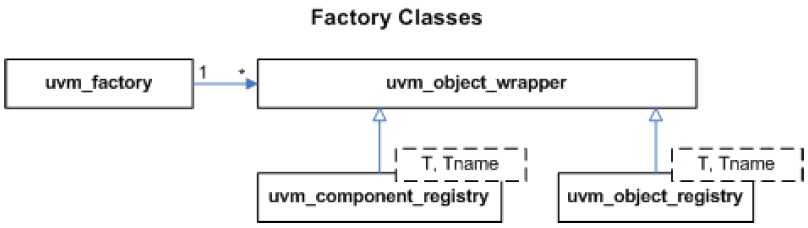

Factory---------uvm_*_register/uvm_factory

配置(config)------uvm_resource/uvm_resoure_db/uvm_config_db

sequencer--------uvm_sequencer_base/uvm_sequencer_param/uvm_squencer/uvm_push_sequencer

sequence--------uvm_sequence_item/uvm_sequence_base/uvm_sequence

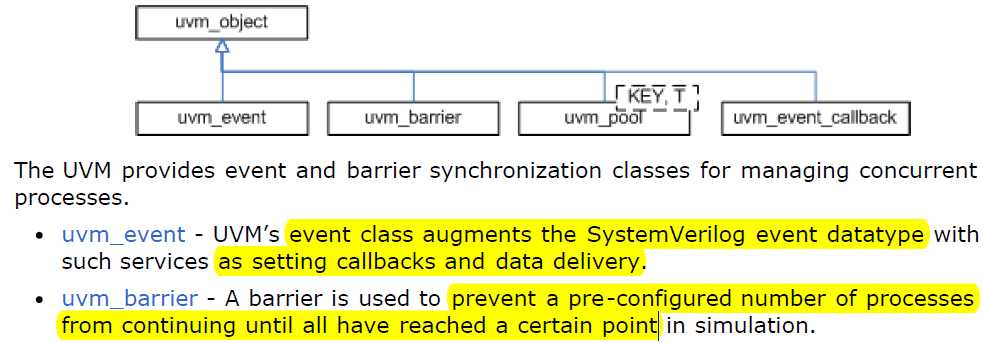

sychronization------uvm_event/uvm_event_callback/uvm_barrier/uvm_objection/uvm_heartbeat

containers----------uvm_pool/uvm_queue

TLM

component--------uvm_component/uvm_callback/uvm_test/uvm_env/uvm_agent/uvm_monitor/uvm_scoreboard/

uvm_driver/uvm_push_driver/uvm_random_stimulus/uvm_subscriber/comparators

Reg model

Macro

Commamd Line

1)uvm_void(virtual)---一个没有member和function的纯虚类。所有class的基类。

2)uvm_object(virtual)---data和component的基类,定义了一系列常用操作

virtual function:get_name/get_full_name/get_inst_id/do_copy/create

function:copy/compare/pack/pack_bytes

3)uvm_transaction(virtual)------variable:events-----event pool中为该transaction instance的event

begin_event/end_event

function:get_event_pool/set_initiator(initiator of this transaction)/get_initiator

is_active

4)uvm_root------所有uvm的潜在top-level,同时控制整个phase的执行。

virtual methods:run_test(+testname)或者cmd中加+UVM_TESTNAME=

function:print_topology/set_timeout

variable:uvm_top------const uvm_root uvm_top = uvm_root::get()

5)uvm_phase------用户可以extend自己的phase,基类(uvm_task_phase/uvm_topdown_phase/uvm_bottomup_phase)

(build phase是topbottom phase,connect是bottomtop phase)

virtual function:raise_objection/drop_objection/ exec_func/exec_task(CB)

function:jump

(new的时候,会有uvm_objection的类型传递)

uvm_factory用来创建UVM中的object和component,通过typedef和macro invocation来实现。

6)uvm_component_registry#(T,Tname)--------virtual function:get_type_name

static function:create/set_type_override/set_inst_override

7)uvm_object_registry#(T,Tname)--------virtual function:get_type_name

static function:create/set_type_override/set_inst_override

8)uvm_factory--------function:set_inst_override_by_type/set_inst_override_by_name/

set_type_override_by_type/set_type_override_by_name/

create_object_by_type/create_component_by_type/

create_object_by_name/create_component_by_name/

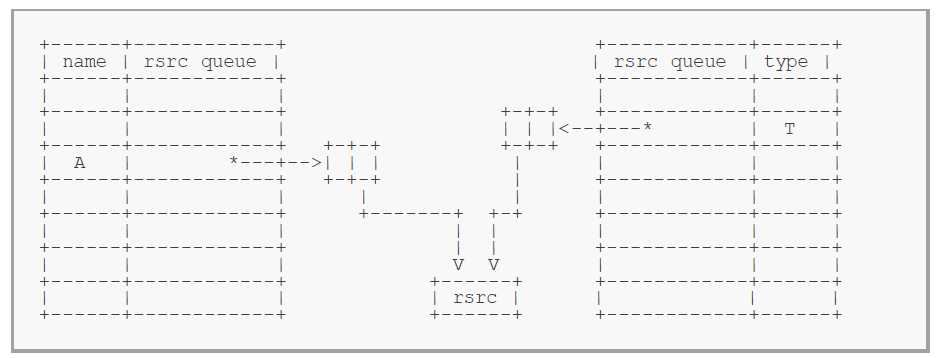

Configuration和Resource Class,提供一个database,供读写。通过queues的方式,可以保存scalar/class handle/

queues/list/virtual interface的结构,保存三部分内容name_table, type_table, set_of scope(通过expression实现)

uvm_resource_db:较低水平的resource database

uvm_config_db:较高水平的resource database,提供configuration的interface

9) virtual class uvm_resource_base--------task:wait_modified()

function:set_scope()

10)uvm_resource_pool--------static function:get()

funciton:set()/set_override()/set_name_override()/set_type_override()

lookup_name()/get_by_name()

11)uvm_resoure #(T)-----------function: read/write()/set/get_by_name/get_by_type

12)uvm_resoure_db #(T)-----------function:/set/get_by_name/get_by_type

13)uvm_config_db #(T)-----------static function:get()/set()/exist()/wait_modified()

uvm_event对SV中的event类型的一次封装:

14)uvm_event---------virtual task wait_on/wait_off/wait_trigger

virtual function reset/add_callback

15)uvm_event_callback(virtual)-------virtual function pre_trigger/post_trigger(uvm_event e, uvm_object data = null)

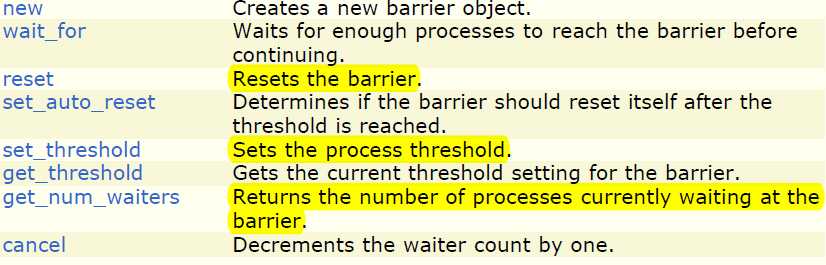

16)uvm_barrier-------virtual task wait_for()

virtual function reset()/set_threshold/get_threshold/cancel

uvm_objection的class,提供end_of_test的机制。

17)uvm_objection------virtual function raise_objection/drop_objection/raised/dropped/set_drain_time

Container class,针对SV中的queue和associative array做的封装。

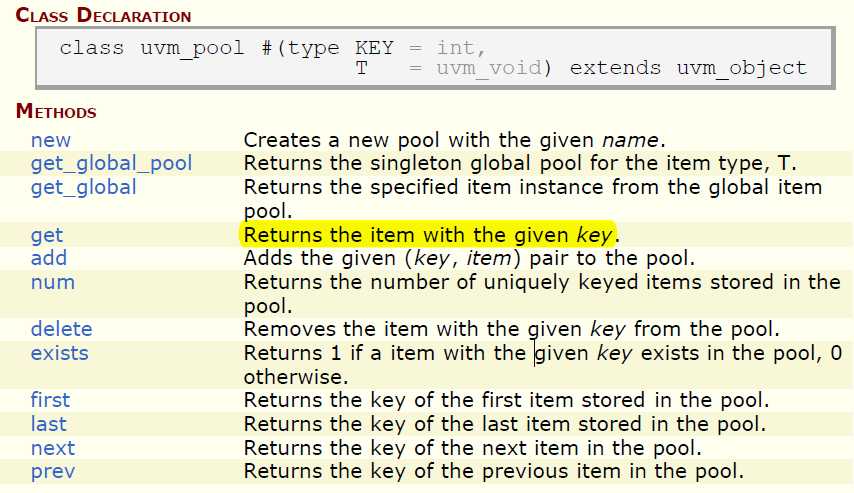

18)uvm_pool #(type KEY = int, T = uvm_void)-----------get/add/num/delete/first/last/nect/prev

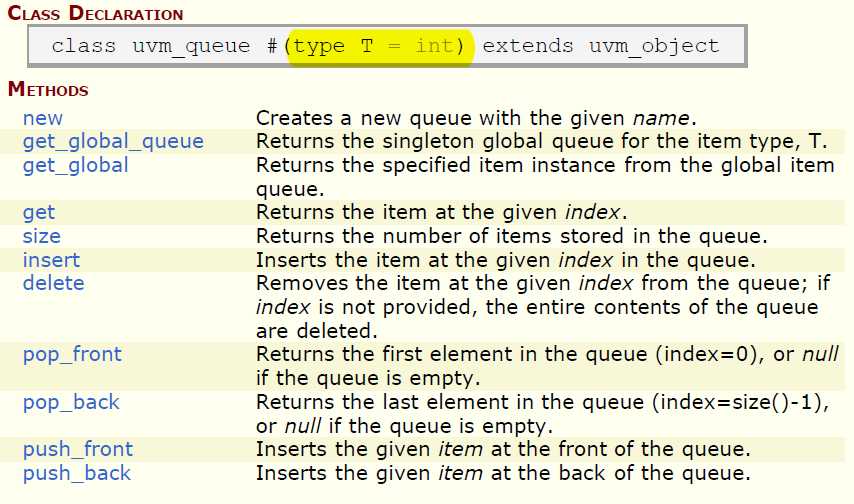

19)uvm_queue #(T)

以上是关于从零开始学习 UVM10.9UVM TLM —— TLM Analysis Port的主要内容,如果未能解决你的问题,请参考以下文章