★DDR相关

Posted KKLHUO

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了★DDR相关相关的知识,希望对你有一定的参考价值。

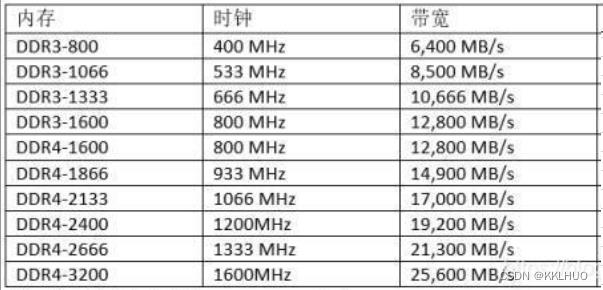

1.速率,电压

DDR3:800-2133Mbps;1.5V(VDDQ)

DDR4:1600-3200Mbps;1.2V(VDDQ)

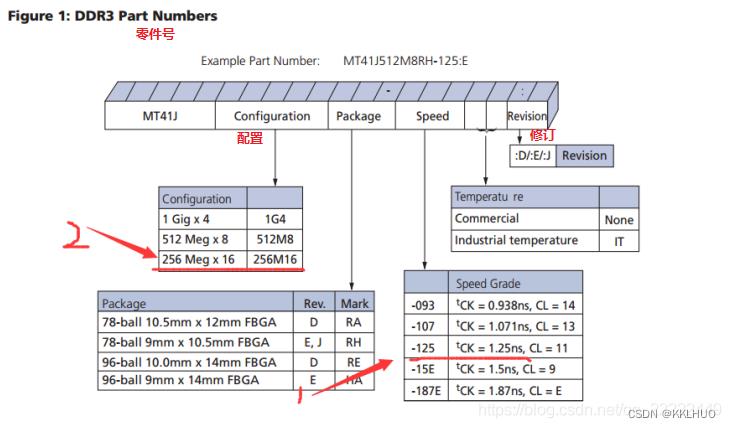

1:tCK=1.25ns,芯片支持最大IO时钟频率(DDR3频率):1/1.25ns=800Mhz

2:16代表芯片的数据位宽是16位(16根数据线);ALLIANCE的DDR3L最大存储容量是4G(245M*16,512*8)

DDR方式传输数据(上升和下降沿都传输),芯片一根数据线传输速率=2*800Mhz=1600MT/s(1600Mbit/s)

带宽是16根数据线同时传输数据速率=1600Mbit/s*16=25600Mbit/s=3200Mbyte/s=3.125GByte/s

DDR2,3,4读写速率理论极限:1333MHz*64bit(单通道,双通道128bit)/8(位到字节单位转换)=10.664GB/s,实际1333单条数据在7-9GB/s,随机读写下降1/10

256-bit LPDDR4@4266,带宽:(256*4266)/(8*1000)=136.5GB/s

256-bit LPDDR5@6400,带宽:(256*6400)/(8*1000)=204.8GB/s

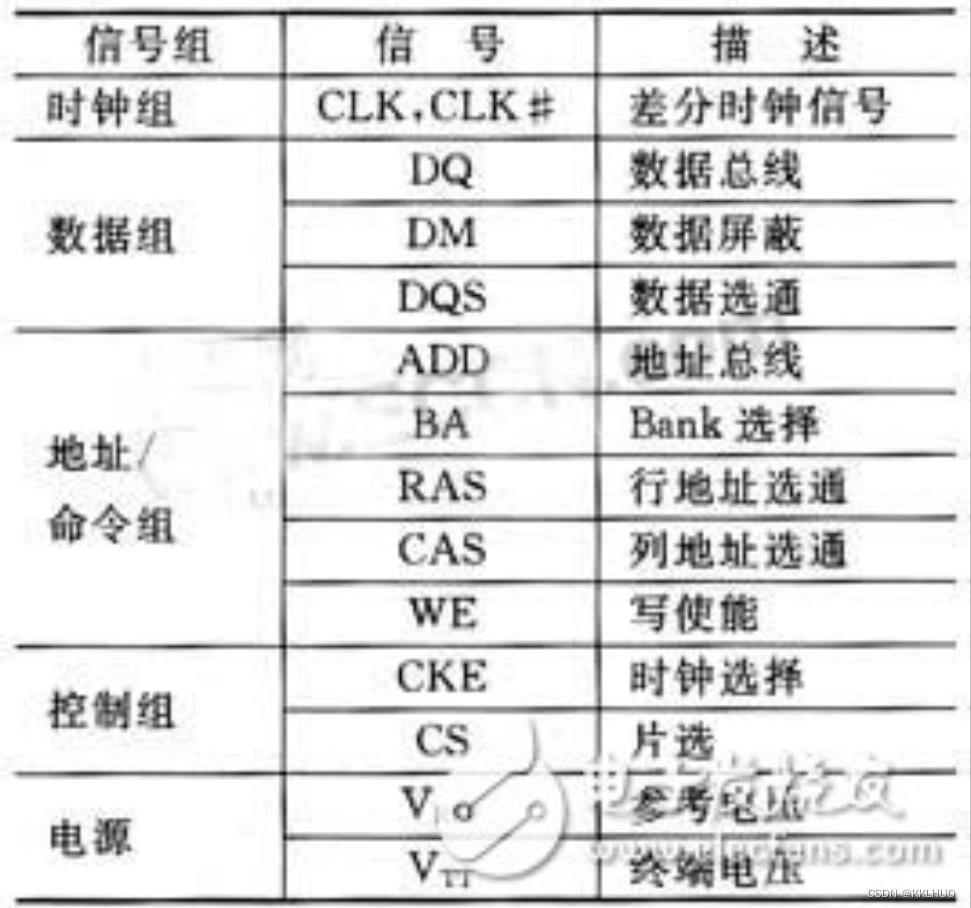

2.接口

DDR3分4类:地址总线,数据总线,控制线,电源与参考电压

数据线

DQ[13:0]:数据总线

DQS,DQS#:数据选通

DM:数据屏蔽

地址线

A[14:0]:地址总线

BA[2:0]:bank选通线

命令,控制,时钟

CKE:时钟使能引脚(输入)

CK,CK#:差分时钟信号(输入)

CS#:片选信号

RAS#,CAS#,WE#:连同CS#,定义一个命令

RESET#:复位信号

ODT:片上终端使能

ZQ#:输出驱动校准的外部参考

电源与参考引脚

VDD:电源电压,1.5V±0.075V

VEDO:DQ电源,1.5V±0.075V

VREFCA:控制,命令,地址的参考电压

VREFDQ:数据的参考电压

VSS:地

VSSQ:DQ地

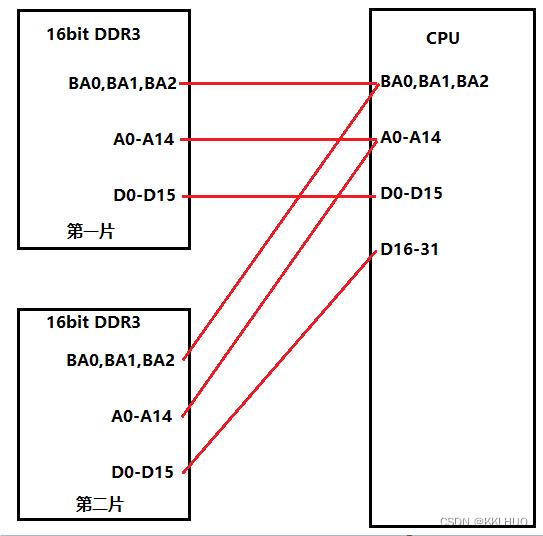

3.16bit和32bit

bank:存储库

一块内存划分多个bank,访问指定存储库编号

地址线有几位BA地址--->多少个bank(2--->4,3--->8)

DDR3地址有3个BA(三个Bank 地址,BA0,BA1,BA2),单块内存是8个bank

存储库=矩阵(很多存储点,一个行号一个列号唯一识别)

一个bank行和列数=行和列有多少位(行:A0-A14=单个bank行总量为2^15;列:A0-A9=列总量为2^10)

16bit/32bit内存概念:以多长单位进行存储(16bit:以bit为单位访问内存=给内存一个地址,内存给一个16bit数据到数据线)

内存模组宽度=内存芯片位数*单面芯片数量

(内存芯片的位宽为8bit,16bit)

二进制,每一个bit有2种取值,表示2个存储区间

n位二进制表示存储区间数位2^n种

每个存储单元是8bit=1B

n位地址总线表示存储区间位2^n Byte

例:

2个16bit DDR3拼成32bit DDR3(16bit DDR3大小为512M Bytes)

硬件连接(只看地址和数据线)

bank地址3个=单个16bit DDR3有8个bank

行有A0-A14,共15个bit=一个bank有2^15个行

列有A0-A9,共10个bit=有2^10个行

单块16bit DDR3容量=2^3*2^15*2^10=2^28=256M

访问一个地址,内存访问16bit数据,2个字节数据

25M个地址=512M数据

2个16bit组成一个32bit(数据)

CPU认为只有一块内存,访问按照BA0-BA2和A0-A14给出地址

两块16bit收到地址之后--->将给定地址上2个字节送到数据线上,或将数据线上两个字节写入制定地址

数据线连接:第一片:D0-D15--->D0-D15;第二片:D0-D15--->D16-D31

CPU认为访问是一块32bit内存,每给出一个地址,访问4个字节数据

CPU:一个32bit拆成2个16bit,DDR:2个16bit组成32bit

CPU访问内存地址有256M,能访问的内存为1G

4.布线规则

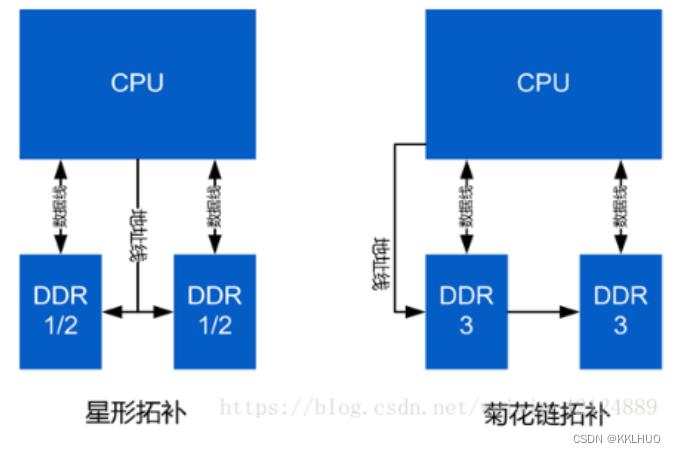

拓扑结构(仅多片有用)

星形结构(DDR1,2);菊花链结构(DDR3)

拓扑结构影响地址线走线方式,不影响数据线

DDR3原则

信号线尽量短,少打过孔,阻抗连续性,单端50Ω,差分100Ω

心得Lattice后端使用经验小结(ECP5UM,DDR3,Diamond3.10,Reveal逻辑分析)

DDR3 IP例化

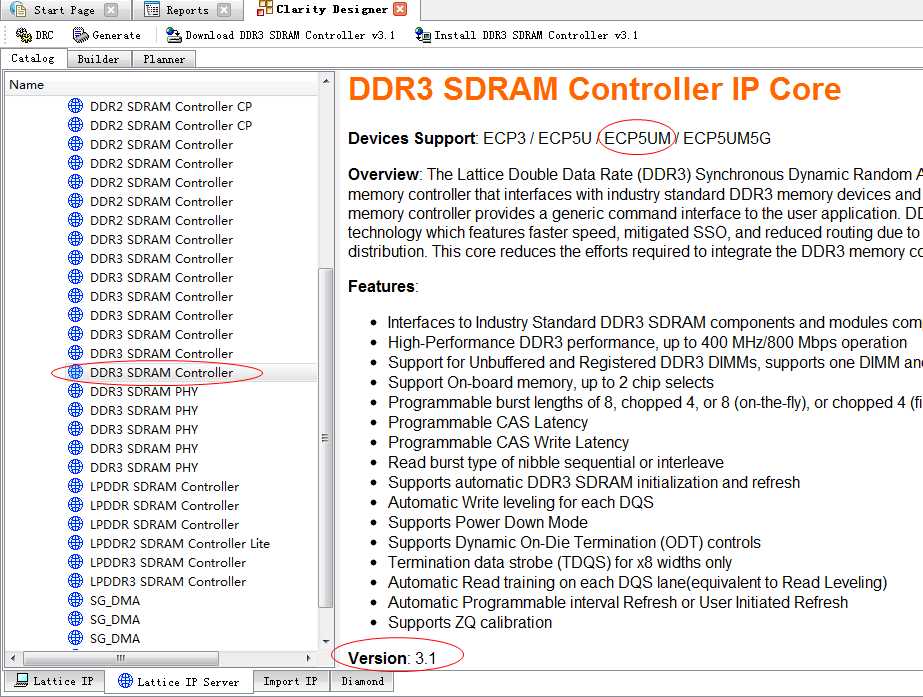

LEF5UM器件,应用DDR3控制器IP。主要分几步:IP获取,安装,例化。

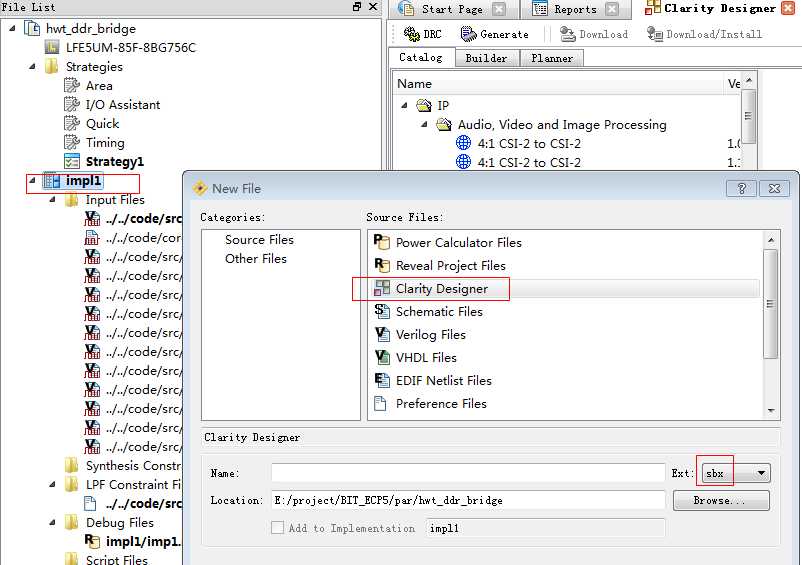

1、先在impl1目录下,右键,新建sbx文件,即Clarity Designer,通过该文件,进行IP的例化管理。

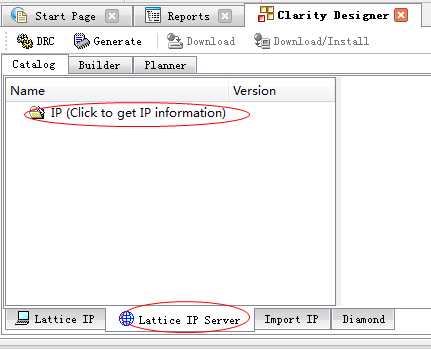

2、打开sbx,在选项卡“Lattice IP Server”里点击IP联网获取IP列表。

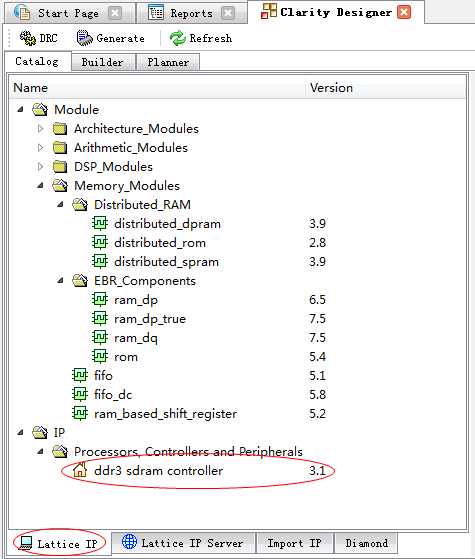

3、选择“DDR3 SDRAM Controller”,目前(18年12月)最新版本3.1,下载(格式exe)后安装到指定目录(如:C:LatticeCoreddr3_sdram_common_v3.1),这样可以在选项卡“Lattice IP”中看到“ddr3 sdram controller 3.1”。

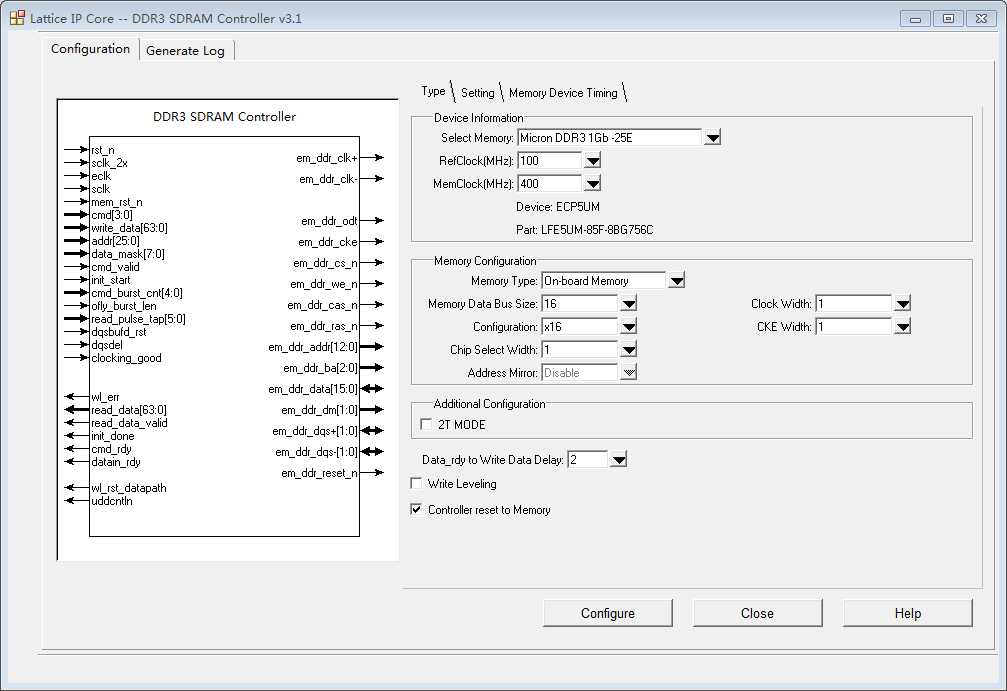

4、打开ip,GUI界面如下,在本项目中,参考时钟(RefClock)来自单板晶振产生的100M,ddr的工作频率400M,双沿也就800M。Memory Type选择On-board Memroy,总线宽度16,配置x16,时钟宽度1。注意,Data_rdy to Write Data Delay选择2,表示data_rdy有效之后必须在第2拍送数据,其实,这里2拍往往是不够的,通常送给ddr3控制器的数据来自一个fifo,这样,fifo跟ddr3控制器直接,不多几拍时钟周期的话,会导致后端时序很难收敛。我的解决办法是,对fifo进行预读操作,让fifo数据打个3~4拍才到ddr3控制器,具体预读fifo的实现就不展开了。

bit/mcs烧录

Lattice工具一个不好用的地方,就是mcs烧录得讲究顺序,否则会报错。烧录mcs的步骤:

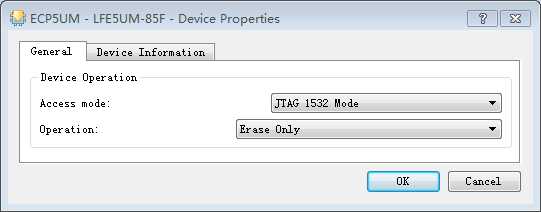

A、JTAG模式下,选择Erase Only。

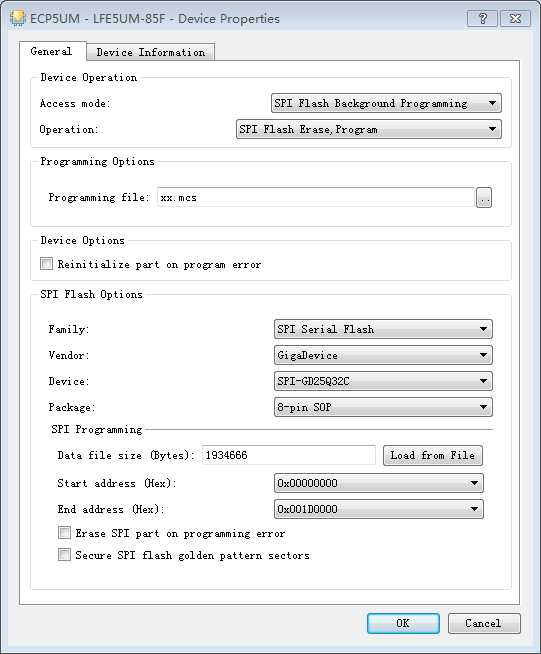

B、选择SPI Flash,操作时可以不用verify,如下。

Reveal逻辑分析仪

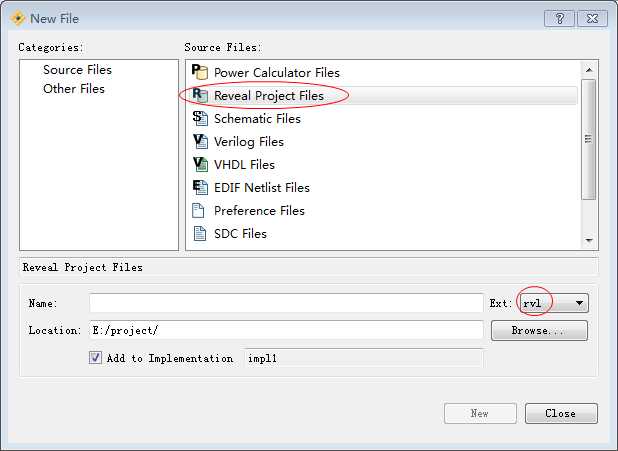

FPGA厂家都会提供内嵌逻辑分析仪,Xilinx叫chipscope,Lattice的叫reveal,可以单独安装reveal程序,也可以在diamond工程中打开。在“File List”的“Debug Files”里,右键,点击Reveal Project Files,可新建*.rvl文件,相对Xilinx,这个rvl比较好用,复制veriog代码信号名,只要没被优化,就可以很快找到。

=======================

by NicoWei

2018-12-25 17:48:09

=======================

以上是关于★DDR相关的主要内容,如果未能解决你的问题,请参考以下文章