FPGA纯vhdl实现MIPI CSI2 RX 4K视频解码输出,OV13850采集,提供工程源码和技术支持

Posted 9527华安

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA纯vhdl实现MIPI CSI2 RX 4K视频解码输出,OV13850采集,提供工程源码和技术支持相关的知识,希望对你有一定的参考价值。

目录

1、前言

FPGA图像采集领域目前协议最复杂、技术难度最高的应该就是MIPI协议了,MIPI解码难度之高,令无数英雄竞折腰,以至于Xilinx官方不得不推出专用的IP核供开发者使用,不然太高端的操作直接吓退一大批FPGA开发者,就没人玩儿了。

本文详细描述了设计方案,工程代码编译通过后上板调试验证,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

关于MIPI协议,请自行搜索,csdn就有很多大佬讲得很详细,我就不多写这块了;

2、Xilinx官方主推的MIPI解码方案

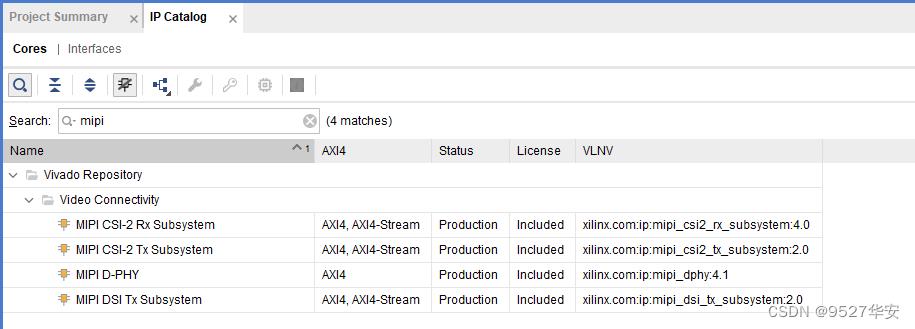

Xilinx官方主推的MIPI解码方案是专用IP核,在vivado的ip仓库里输入MIPI就会看到如下的一堆IP:

Xilinx方案使用很简单,调用IP就行,用SDK配置即可使用,MIPI解码后的数据格式为AXIS,方便与他家的VDMA之类的IP对接,你无须关心复杂的MIPI协议即可畅玩儿MIPI,但问题就来了,如果你用的FPGA不是Xilinx家的怎么办?

关于Xilinx自家的MIPI方案,请参考我之前写的文章;Xilinx的MIPI方案

3、纯Vhdl方案解码MIPI

本方案MIPI解码后的视频时序为VGA时序,即行同步,场同步,数据有效,数据信号;方便后端直接处理;

解串部分使用Xilinx源语,本工程用到的是7系列源语,更高级别的FPGA应用,需要更改源语参数,但问题不大;

一个字:牛逼,表现如下:

1:纯Vhdl代码实现,学习性和阅读性达到天花板;

2:移植性还可以,只要兼容Xilinx解串源语的FPGA均可移植;

3:算法达到天花板,标准的CSI2接收协议实现解码;

4:实用性达到天花板,采用OV13850摄像头作为输入,不同于市面上验证性和实验性的工程,本设计直接面向实用工程,贴近真实项目,MIPI输入,2路视频输出,做类似项目的兄弟可直接拿去用,一个月工资直接拿到手。。。

4、vivado工程介绍

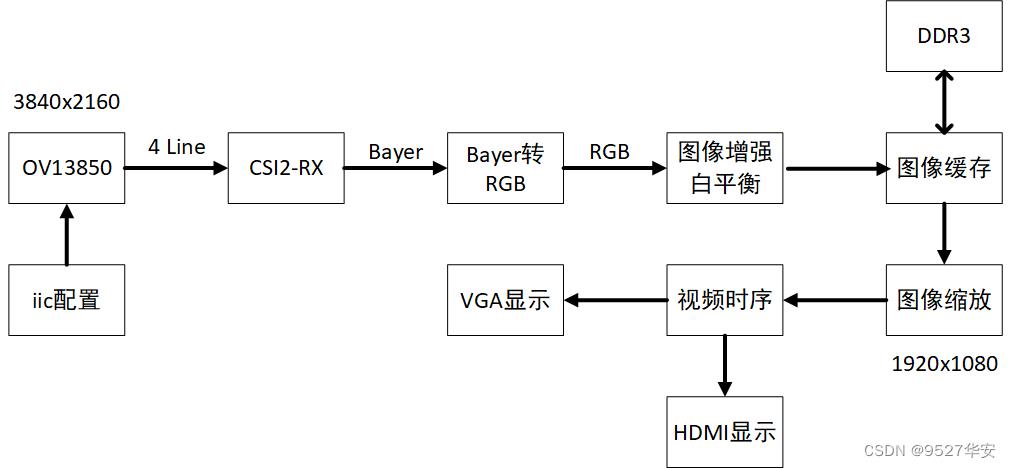

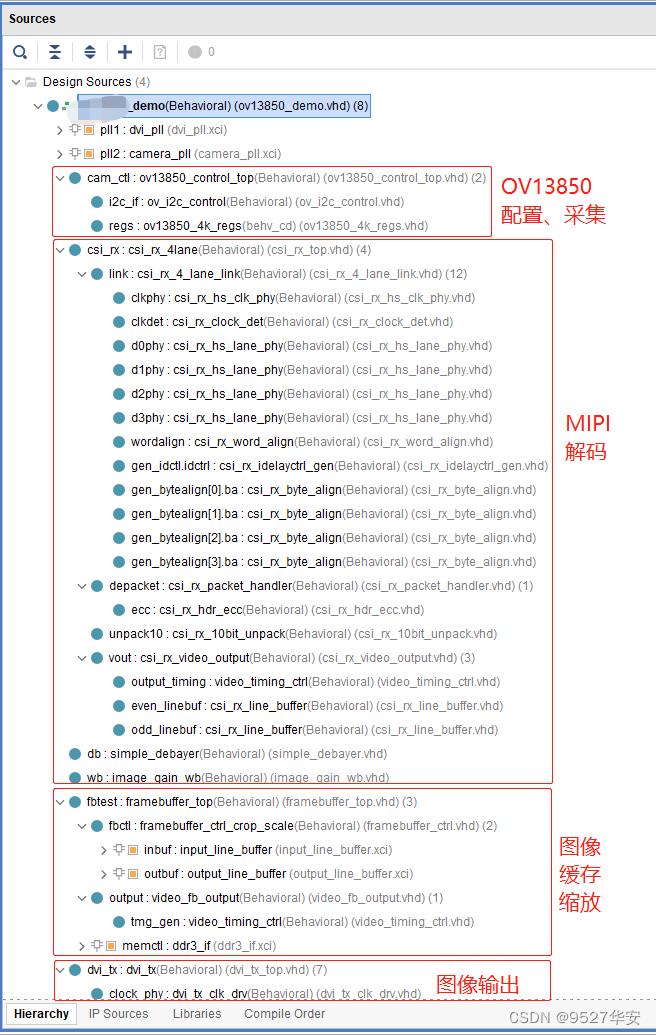

工程架构如下:

开发板:Xilinx Kintex7开发板;

开发环境:vivado2019.1;

输入:OV13850;4line;分辨率3840x2160;

输出1:VGA;分辨率1920x1080;

输出2:HDMI;分辨率1920x1080;

工程代码架构如下:

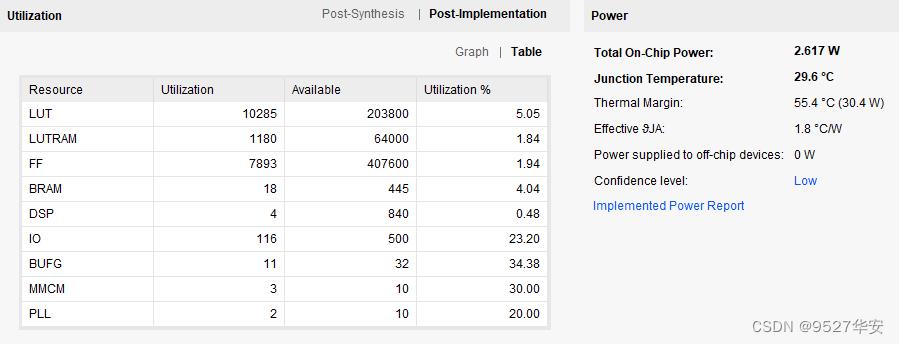

逻辑资源消耗和功耗如下:

5、上板调试验证

由于某些不可抗力和高层次复杂因素,不便展示调试结果,请见谅;

6、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

MIPI CSI2学习:说一说MIPI CSI2

1. MIPI CSI2简介

MIPI联盟是一个开放的会员制组织。2003年7月,由美国德州仪器(TI)、意法半导体(ST)、英国ARM和芬兰诺基亚(Nokia)4家公司共同成立。MIPI联盟旨在推进移动应用处理器接口的标准化 。MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风/喇叭接口SLIMbus等。

CSI(Camera Serial Interface)是由MIPI联盟下Camera工作组指定的接口标准。CSI-2是MIPI CSI第二版,主要由应用层、协议层、物理层组成,最大支持4通道数据传输、单线传输速度高达1Gb/s。

2. MIPI CSI2的分层结构

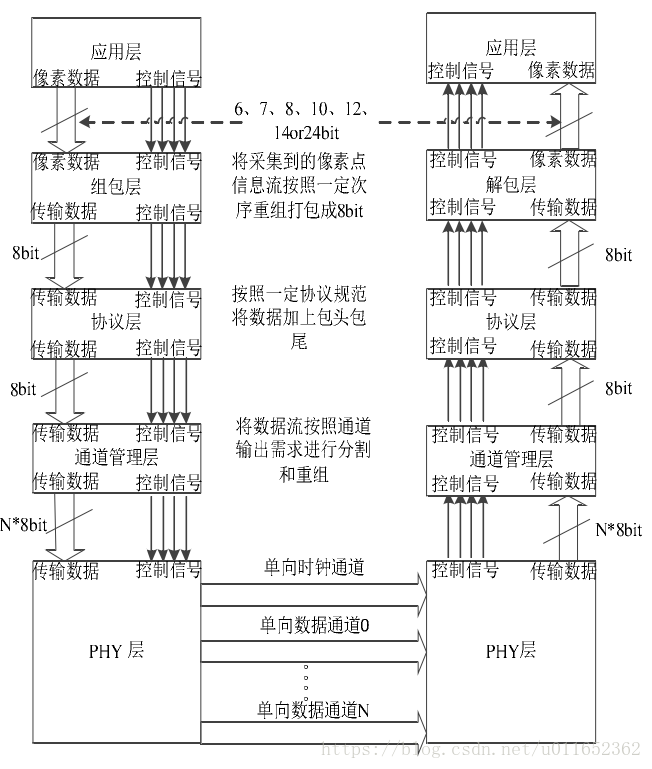

MIPI CSI2的分层方法有好几种,根据MIPI联盟的规范,CSI2可分为5层,分别为:应用层、组包/解包层、底层协议层(Low Level Protocol)、通道管理层和物理层。

为了更清晰的描述协议结构中所述的名词,列表对其做了详细的阐述具体如表 2-1 所示。

表 2-1协议结构名词解释

| 名称 | 解释 |

|---|---|

| 应用层 | 即是处理原始图像数据的各种算法模块 |

| 组包/解包层 | 负责将数据按照一定的次序,切割成 8 比特数据。 |

| 底层协议层 | 为新生成的数据加上包头包尾,形成符合协议要求的数据流。 |

| 通道管理层 | 将生成的数据流按照一定次序和要求,进行读写管理,输出数据流。 |

| 物理层 | 生成 MIPI 最后的信号波形。 |

| 像素数据 | 经过图像模块处理过的数据流,或者原始图像的数据路。 |

| 传输数据 | 经过MIPI模块切割或者加上包头包尾的数据。 |

| 控制信号 | 模块间的控制数据流 |

| 发送端 | 包括了 MIPI 数字部分,转接板等实现MIPI 信源传输的部分。 |

| 接收端 | 包括了转接板和商用接收端模块,负责解析收到的 MIPI 信源。 |

详细的来说,链路的工作顺序如下:

首先原始的图像数据会在应用层做相应的图像处理,包括白平衡、噪声去除、色彩还原等。

处理过后的数据进入组包层做数据分割和重组,再传给协议层。协议层根据数据类型产生包头,根据数据内容产生构成包尾的校验序列,之后将包头、数据本身、包尾组合起来发送给通道管理模块。

通道管理模块按照通道的选通情况,合理分配数据到每个通道,之后数据经过数模转换进入物理层传输,接收端在收到物理层的数据后,再按照之前的逆序解包出原始的图像数据。

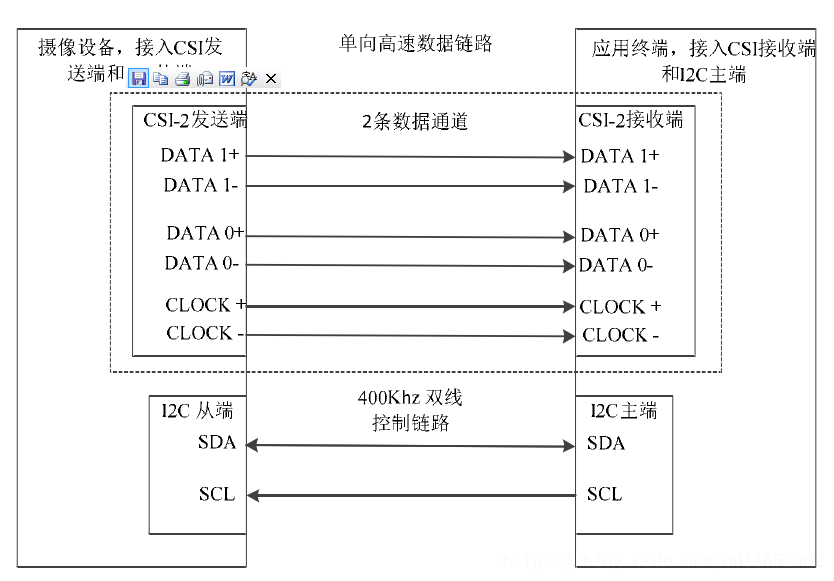

3 MIPI CSI2的物理连接

除地线外,MIPI CSI2一般会有1对I2C通信引脚,1对MIPI差分时钟引脚和1~4对MIPI差分数据信号引脚,如图3-1所示。

图中涉及到的名词如表3-1所示:

表3-1 CSI2涉及到的各个引脚解释

| 名称 | 解释 |

|---|---|

| DATA 1+ / DATA 1- MIPI | 协议组包生成的差分模拟数据信号第二组 |

| DATA 2+ / DATA 2- MIPI | 协议组包生成的差分模拟数据信号第一组 |

| CLOCK+ / CLOCK- MIPI | 协议组包生成的差分模拟时钟信号 |

| SDA I2C | 数据信号线 |

| SCL I2C | 时钟信号线 |

在典型的应用中发送端在完成对图像的各种处理后,按照协议对数据进行打包,然后通过差分信号线向接收端传输信号,差分信号线一般有一对时钟差分线和多对数据差分线,数据差分信号线的数量与需要传输的数据量的要求有关,数据量越大多对数据线能更容易满足链路的需求。一般情况下两百万到五百万像素的手机使用两对差分数据线,即两个数据通道。而当摄像头像素进一步提高到八百万甚至一千三百万时一般会使用四个数据通道,即四对差分数据线。

与外部进行控制信号交互时,采用的是 I2C 接口,在 MIPI 的发送端使用的是 I2C 从端的 IP,MIPI CSI-2 接口的控制寄存器连接 I2C 的从端,这样外部接收装置可以通过 I2C 去配置 MIPI 发送端的内部寄存器,以此改变 MIPI CSI-2 接口内部状态机的持续时间和最后输出数据时的通道数,又或者在调试过程中读出这些寄存器,去做相应的检查,以判断发送端的工作状态,再通过接收端的现象来分析发送端是否工作在正常的状态。

4. MIPI CSI2的工作模式

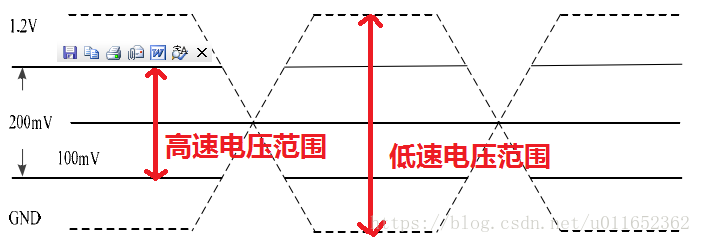

D-PHY有两种传输模式:

(1) HS 高速传输模式,用于传输突发数据,同步传输,信号为差分信号,电平范围为100mv-300mv,传输速度范围是80-1000Mbps。在该模式下传输时,当差分线正端收到 1.2V 信号,负端收到 0V信号时,这时接收端识别为 1。反之为0。

??

(2) LP 低功耗模式,用于传输控制指令,异步传输,信号线为单端,电平范围是0-1.2v,没有用时钟线,时钟是通过两个数据线异或而来的,速度只有10Mbps。在该模式下传输时,当正端接收到300m V,负端接收到100m V 时接收端识别为1.反之则识别为0.

5. MIPI CSI2的数据包格式

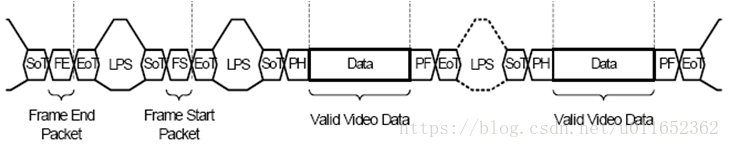

MIPI CSI2是一个面向字节的,基于包的协议;它支持任意大小的数据通过短包和长包格式传输。各个包之间由EOT-LPS-SOT序列隔开,如图5-1所示。

LLP包有两种:长包和短包。每个包的传输以SoT(start of transmission)开始,EoT(end of transmission)结束,中间间隙是LPS(Low Power State低功耗状态)。

5.1 MIPI CSI2的长包格式

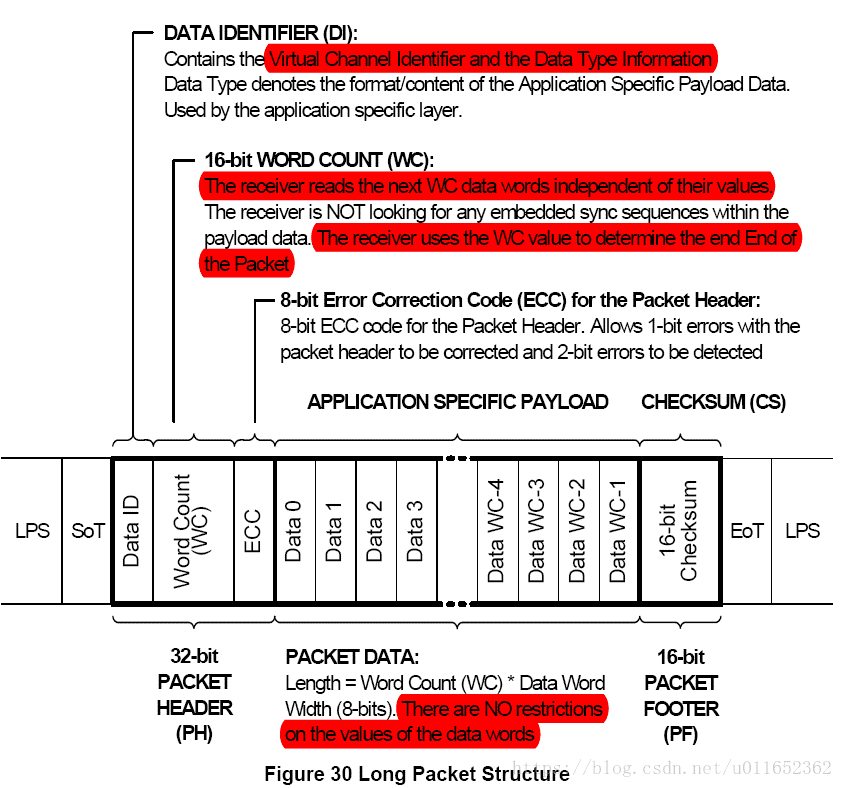

MIPI CSI2的长包主要有包头、数据包和包尾三部分构成。而包头又可细分为:数据标识(data identifier)、数据包大小(word count)和错误校验码(ECC)构成。如图5-2所示。

其中,数据标识大小为1字节,包含虚拟数据通道号[7:6]和数据类型[5:0]。

- 数据包大小为2字节,其内容为传送数据的长度,以“字”为单位。

- 错误校验码大小为1字节,负责对数据包的传输错误进行检查及纠错。

- 数据包可以传送数据的大小为0~65535字节。

- 包尾大小为2字节,是数据负荷的检查和。

5.2 MIPI CSI2的短包格式

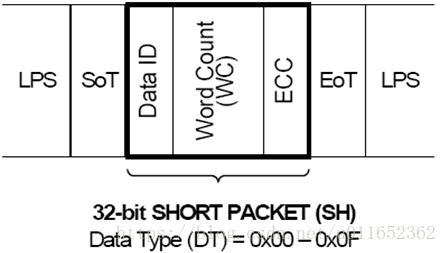

与长包相比,短包没有数据包和包尾。数据标识DI中的数据类型在0x00到0x0F之间。WC字段是短包的数据域,这个数据可由用户定义。ECC是校验码,能对1bit错误进行纠错,2bit错误进行检查,如图5-3所示。

以上是关于FPGA纯vhdl实现MIPI CSI2 RX 4K视频解码输出,OV13850采集,提供工程源码和技术支持的主要内容,如果未能解决你的问题,请参考以下文章