FPGA中,数据位数对数据选择器消耗的资源影响大吗?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA中,数据位数对数据选择器消耗的资源影响大吗?相关的知识,希望对你有一定的参考价值。

写一个数据选择器,输入四个数据,位宽为112bit。根据控制信号对六个输出赋值;也就是相当于六个四选一选择器。代码如下。用ISE综合,消耗980个slices,1706个FF,1124个LUT。有没有什么优化方法能够减少资源消耗?

module align_vpu_choice_test1(

clk,

grpnum,

A1_in,

A2_in,

A3_in,

A4_in,

in1,

in2,

in3,

in4,

in5,

in6

);

input clk;

input [3:0] grpnum; //控制

input [111:0] A1_in, A2_in, A3_in, A4_in; //输入的数据

output [111:0] in1, in2, in3, in4, in5, in6; //输出的数据

reg [111:0] in1, in2, in3, in4, in5, in6;

always @ (grpnum or A1_in or A2_in or A3_in or A4_in)

case (grpnum)

4'h0: begin

in1 = A1_in;

in2 = A2_in;

in3 = A4_in;

in4 = in4;

in5 = in5;

in6 = A3_in;

end

4'h1: begin

in1 = in1;

in2 = A3_in;

in3 = in3;

in4 = A4_in;

in5 = A1_in;

in6 = A2_in;

end

……………………………………

4'hf: begin

in1 = in1;

in2 = A3_in;

in3 = A2_in;

in4 = in4;

in5 = A4_in;

in6 = A1_in;

end

endcase

endmodule

图书馆的IEEE;

使用IEEE.STD_LOGIC_1164.ALL;

实体MUX21 IS

端口(

答:STD_LOGIC; B:在STD_LOGIC;

S:IN STD_LOGIC;

Y:OUT STD_LOGIC );

终端实体MUX21;

MUX21建筑MUX21A IS

工艺(S,A,B)BEGIN

如果s = '0'则Y <= A;

ELSE<= B;

END IF; 结束进程;

完MUX21A;

顶层文件

LIBRARY IEEE;

使用IEEE.STD_LOGIC_1164.ALL;

实体MUX31 IS

端口(A1,A2,A3,S0,S1:IN STD_LOGIC;

OUTY:OUT STD_LOGIC);

完MUX31;

MUX31建筑MUX31A IS

信号TMP:STD_LOGIC;

分量MUX21

端口(A,B,S:IN STD_LOGIC,Y:OUT STD_LOGIC);

端部部件;

U0:MUX21端口映射(A => A2,B => A,S => S 0,Y => TMP);

U1:MUX21端口映射(A => A 1,B => TMP,S => S1,Y => OUTY);

完MUX31A;

类别:埃达| |添加到收藏夹|分享我的贴吧|浏览(1719)|评论(2)上一篇:使用LCA88ET软件编译文件的书面笔记...下一篇:特殊最接近的整数嵌套读者:

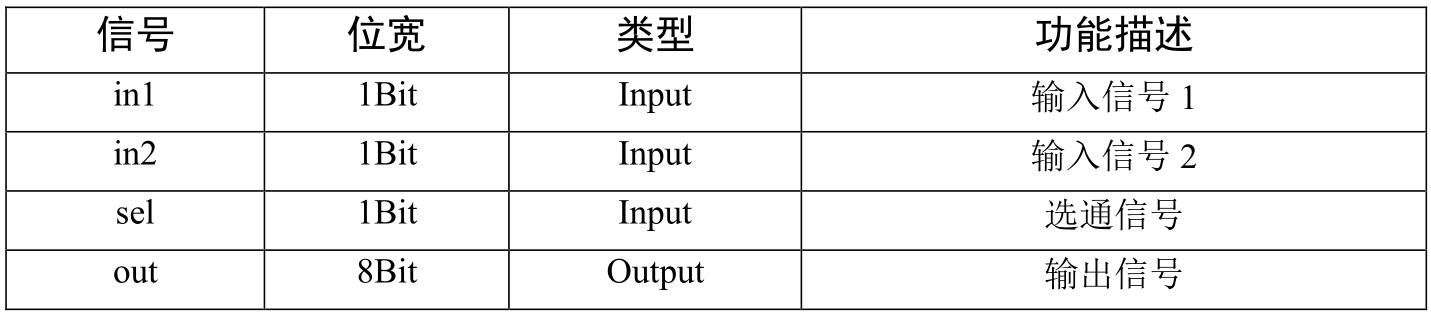

FPGA—多路选择器(简单逻辑组合电路)

摘要:多路选择器是数据选择器的别称。在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,也称多路选择器或多路开关。在选择变量控制下,从多路数据输入中某一路数据送至输出端。对于一个具有 2^n 个输入和 1 个输出的多路选择器,有 n 个选择变量。多路选择器也是 FPGA 内部的一个基本资源,主要用于内部信号的选通。简单的多路选择器还可以通过级联生成更大的多路选择器。

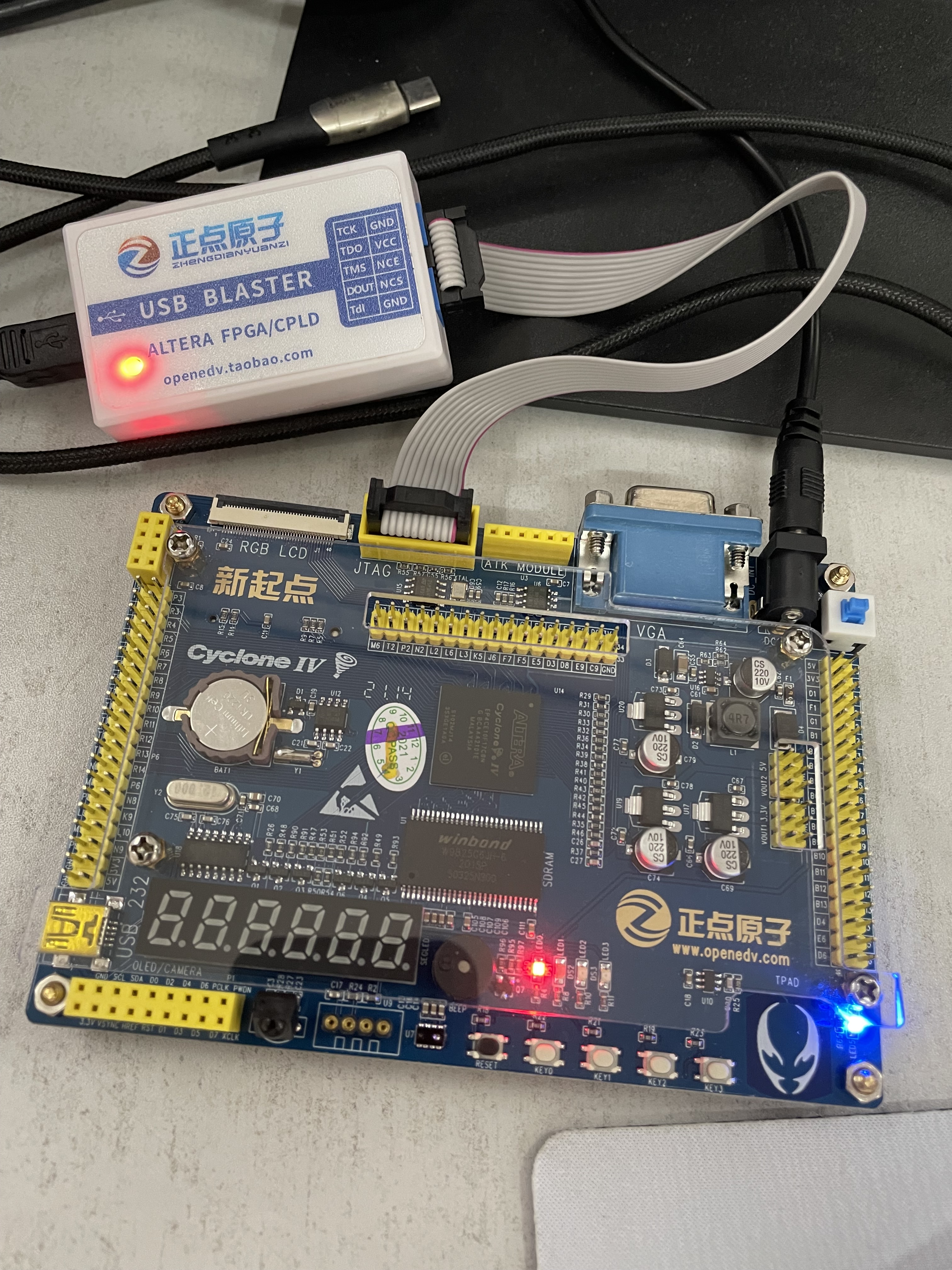

一、使用的开发板

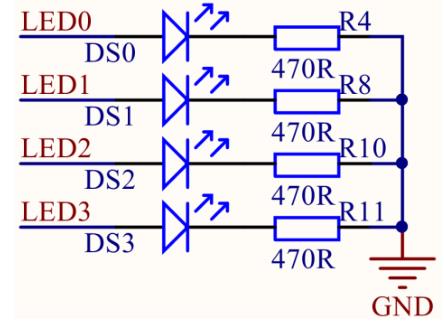

LED灯硬件原理图 LED灯硬件原理图

|

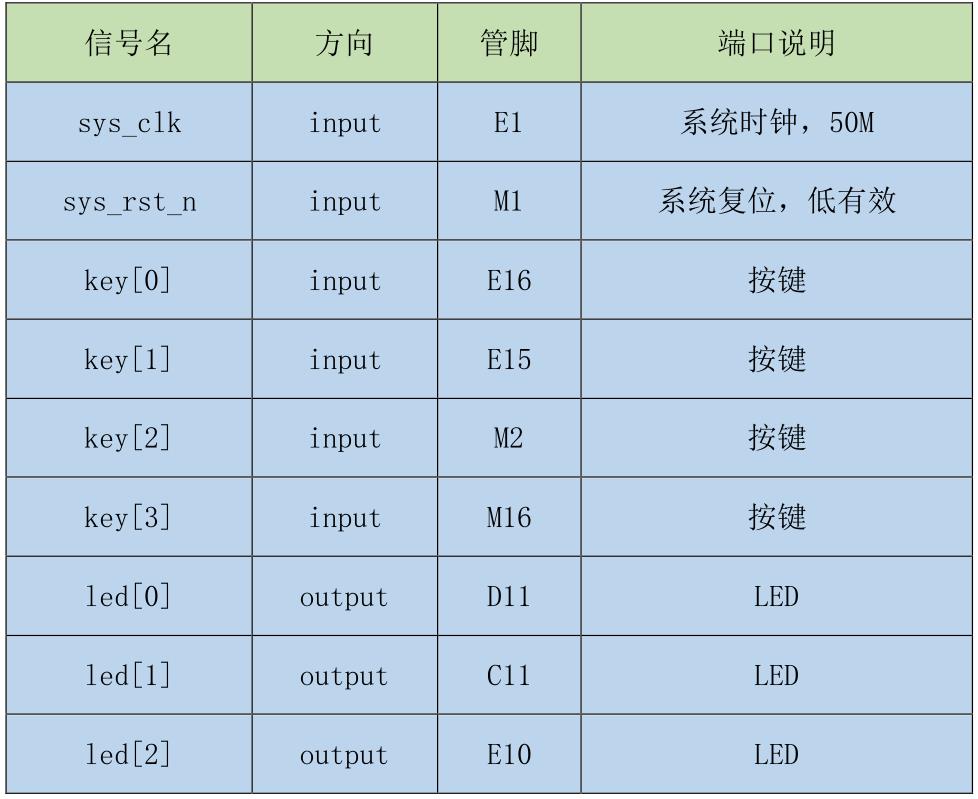

流水灯实验管脚分配 流水灯实验管脚分配

|

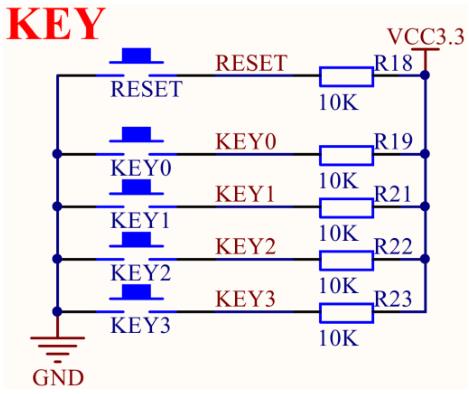

按键电路原理图 按键电路原理图

|

触摸按键控制LED管脚分配图 触摸按键控制LED管脚分配图

|

二、功能分析

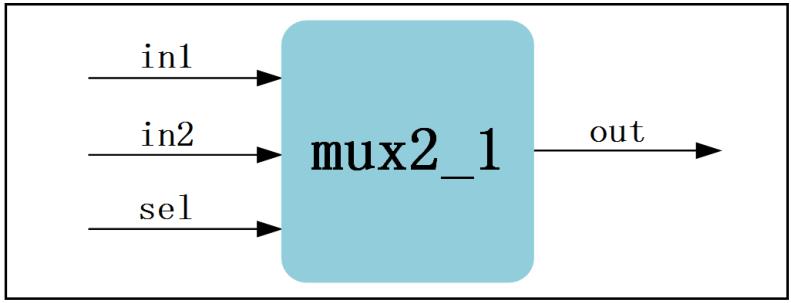

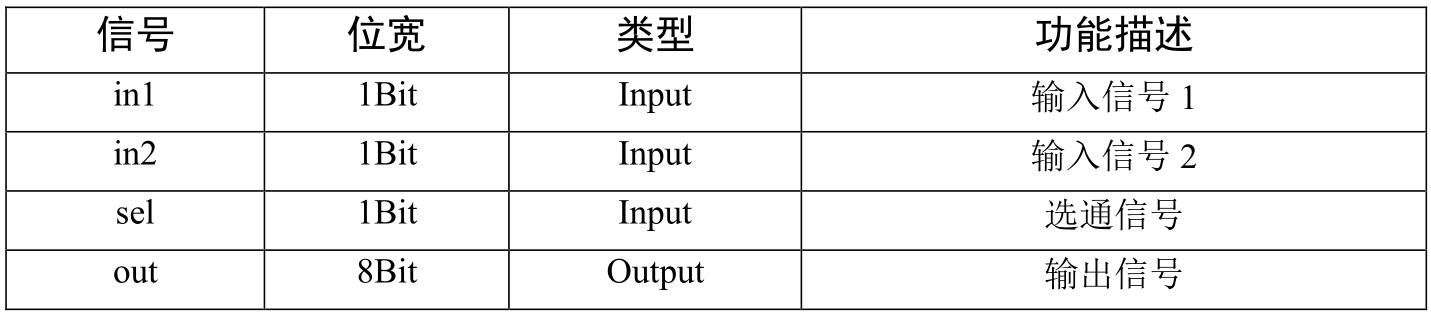

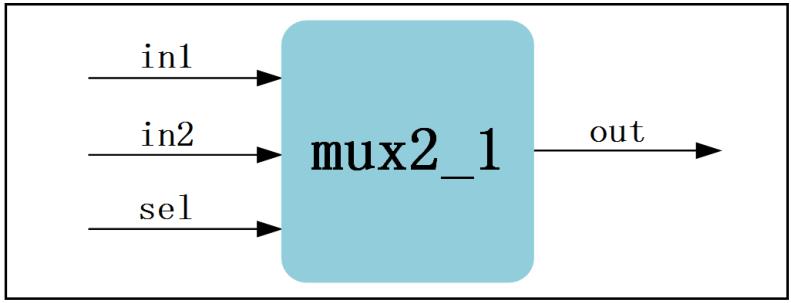

1、模块框图

模块框图 模块框图

|

输入输出信号描述 输入输出信号描述

|

2、波形图绘制

框图结构设计完毕后就可以实现该模块的具体功能了,也就是要找到输入和输出之间具体的映射关系。输入和输出满足信号与系统中输入与响应的关系。其中输入信号的名字用绿色表示,输出信号的名字用红色表示,任意模拟输入波形,画出输出信号的波形。

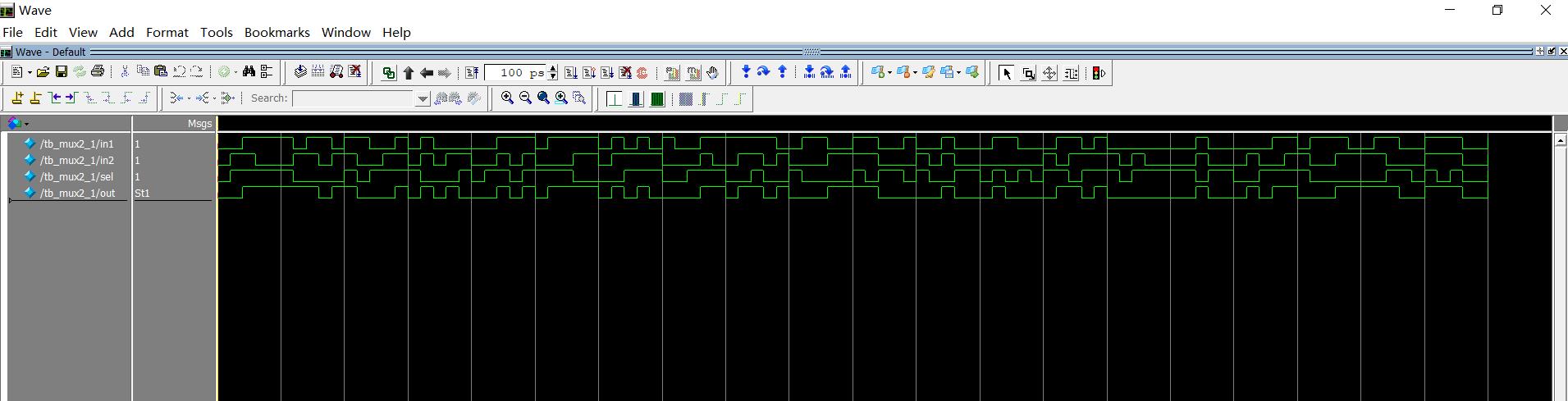

经分析得,当 sel 为低电平时,out 的输出波形和 in2 相同;当 sel 为高电平时,out 的输出波形和 in1 相同。根据分析的输入输出关系,我们列出如表格所示的真值表,然后再根据真值表的输入与输出的对应关系画出波形图。其波形图如图所示,图中蓝色的线代表有效信号。

三、程序设计

1、RTL代码的编写

开始RTL代码的编写,RTL代码编写出的模块叫RTL模块(后文中也称功能模块、可综合模块)。之所以叫RTL代码是因为用Verilog HDL在Resistances Transistors Logic(寄存器传输级逻辑)来描述硬件电路,RTL代码能够综合出真实的电路以实现我们设计的功能,区别于不可综合的仿真代码。

`timescale 1ns/1ns

module mux2_1 //模块的开头以“module”开始,然后是模块名“mux2_1”

(

input wire in1, //输入端1,信号名后就是端口列表“();”(端口列表里面列举了该模块对外输入、输出信号的方式、类型、位宽、名字),该写法采用了Verilog-2001标准,这样更直观且实例化更方便,之前的Verilog-1995标准是将模块对外输入、输出信号的方式、类型、位宽都放到外面

input wire in2, //输入端2,当数据只有一位宽时位宽表示可以省略,且输入只能是wire型变量

input wire sel, //选择端,每行信号以“,”结束,最后一个后面不加“,”

output reg out //结果输出,输出可以是wire型变量也可以是reg型变量,如果输出在always块中被赋值(即在“<=”的左边)就要用reg型变量,如果输出在assign语句中被赋值(即在“=”的左边)就要用wire型变量

); //端口列表括号后有个“;”不要忘记

//********************************************************************//

//***************************** Main Code ****************************//

//********************************************************************//

//out:组合逻辑输出sel选择的结果

always@(*) //“*”为通配符,表示只要if括号中的条件或赋值号右边的变量发生变化则立即执行下面的代码,“(*)”在此always中等价于“(sel, in1, in2)”写法

if(sel == 1'b1) //当“if...else...”中只有一个变量时不需要加“begin...end”,也显得整个代码更加简洁

out = in1; //always块中如果表达的是组合逻辑关系时使用“=”进行赋值,每句赋值以“;”结束

else

out = in2;

/*

//out:组合逻辑输出选择结果

always@(*)

case(sel)

1'b1 : out = in1;

1'b0 : out = in2;

default : out = in1; //如果sel不能列举出所有的情况一定要加default。此处sel只有两种情况,并且完全列举了,所以default可以省略

endcase

*/

/*

out:组合逻辑输出选择结果

assign out = (sel == 1'b1) ? in1 : in2; //此处使用的是条件运算符(三元运算符),当括号里面的条件成立时,执行"?”后面的结果;如果括号里面的条件不成立时,执行“:”后面的结果

*/

endmodule //模块的结尾以“endmodule”结束(每个模块只能有一组“module”和“endmodule”,所有的代码都要在它们中间编写)

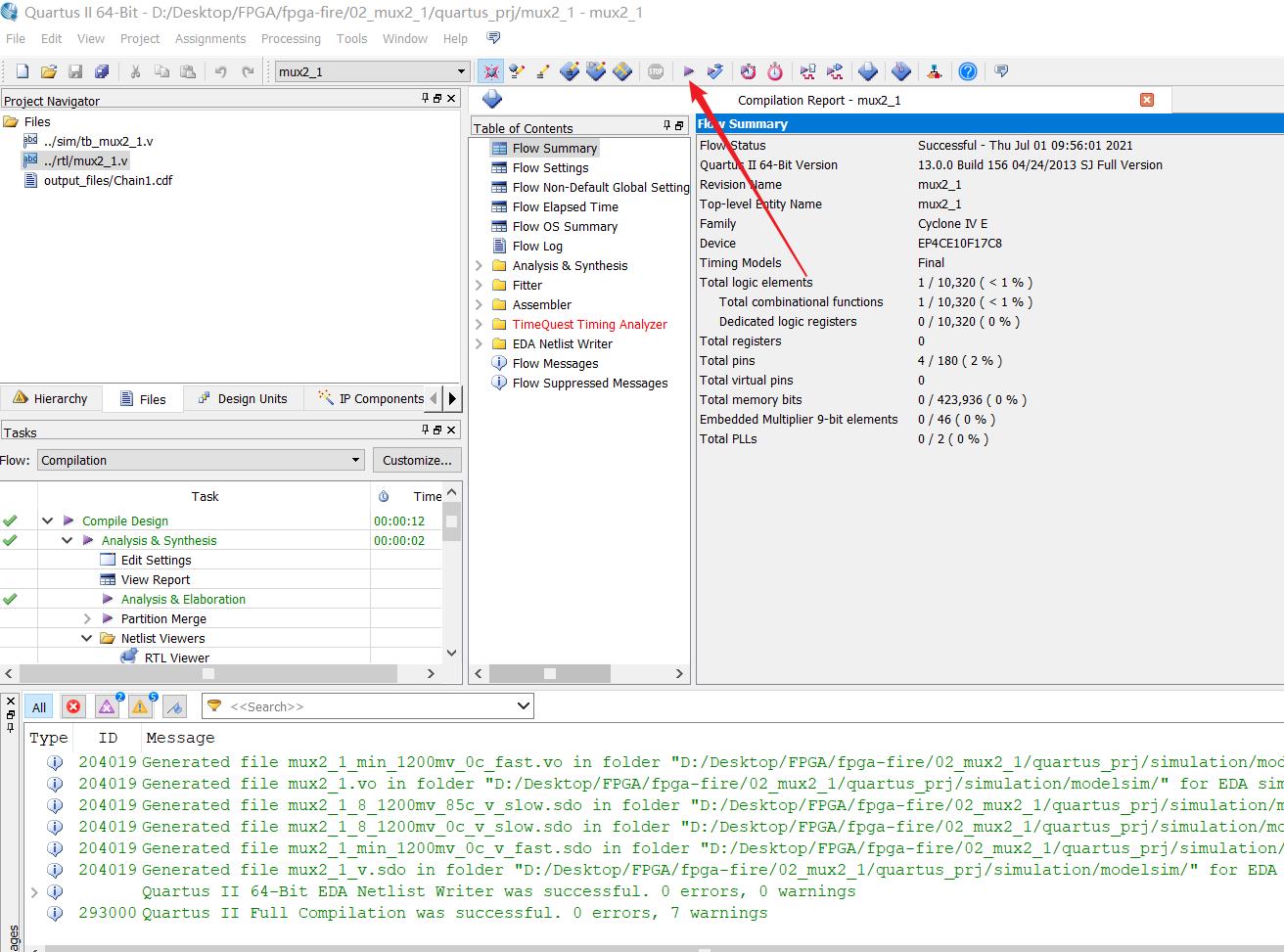

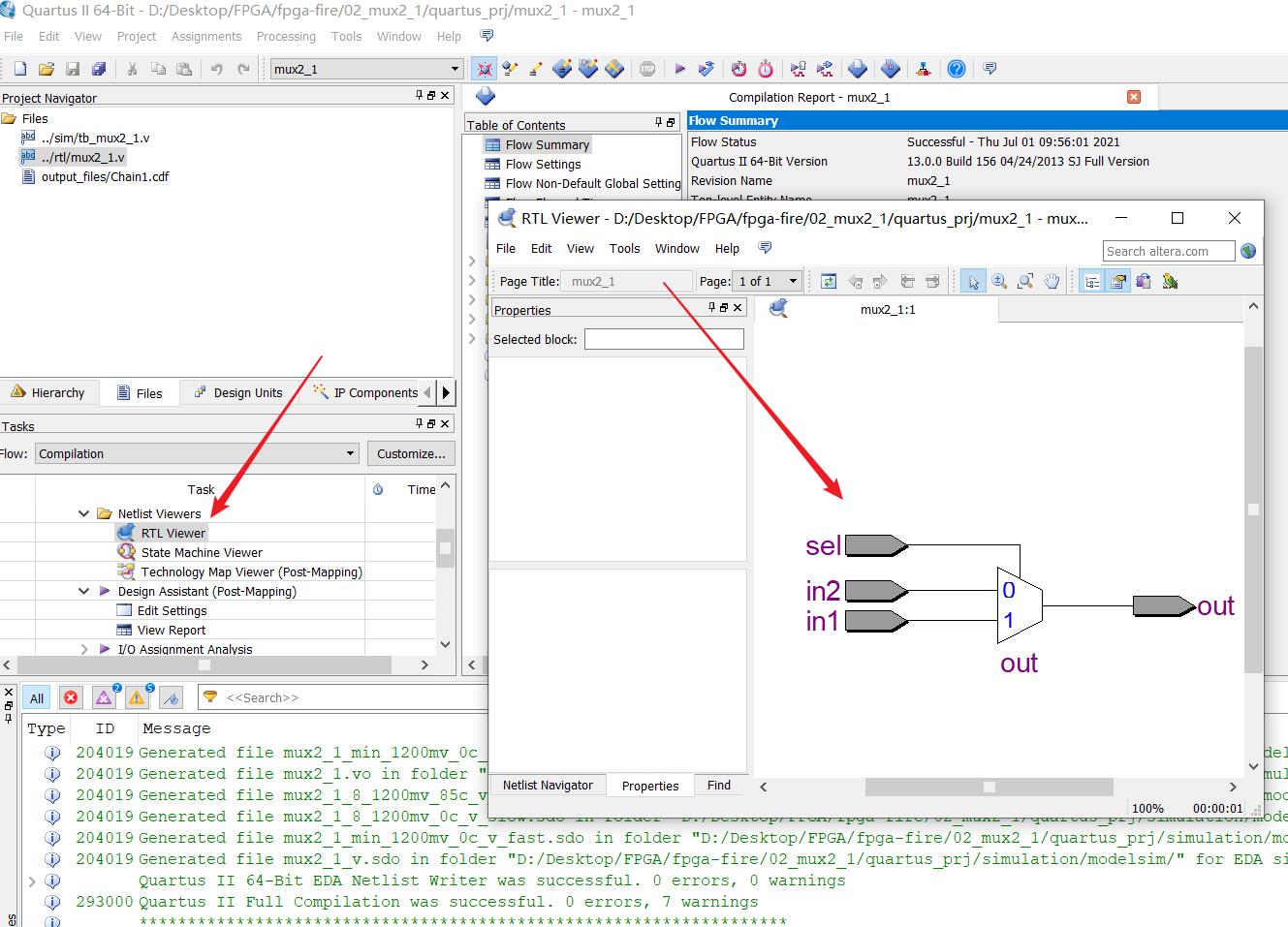

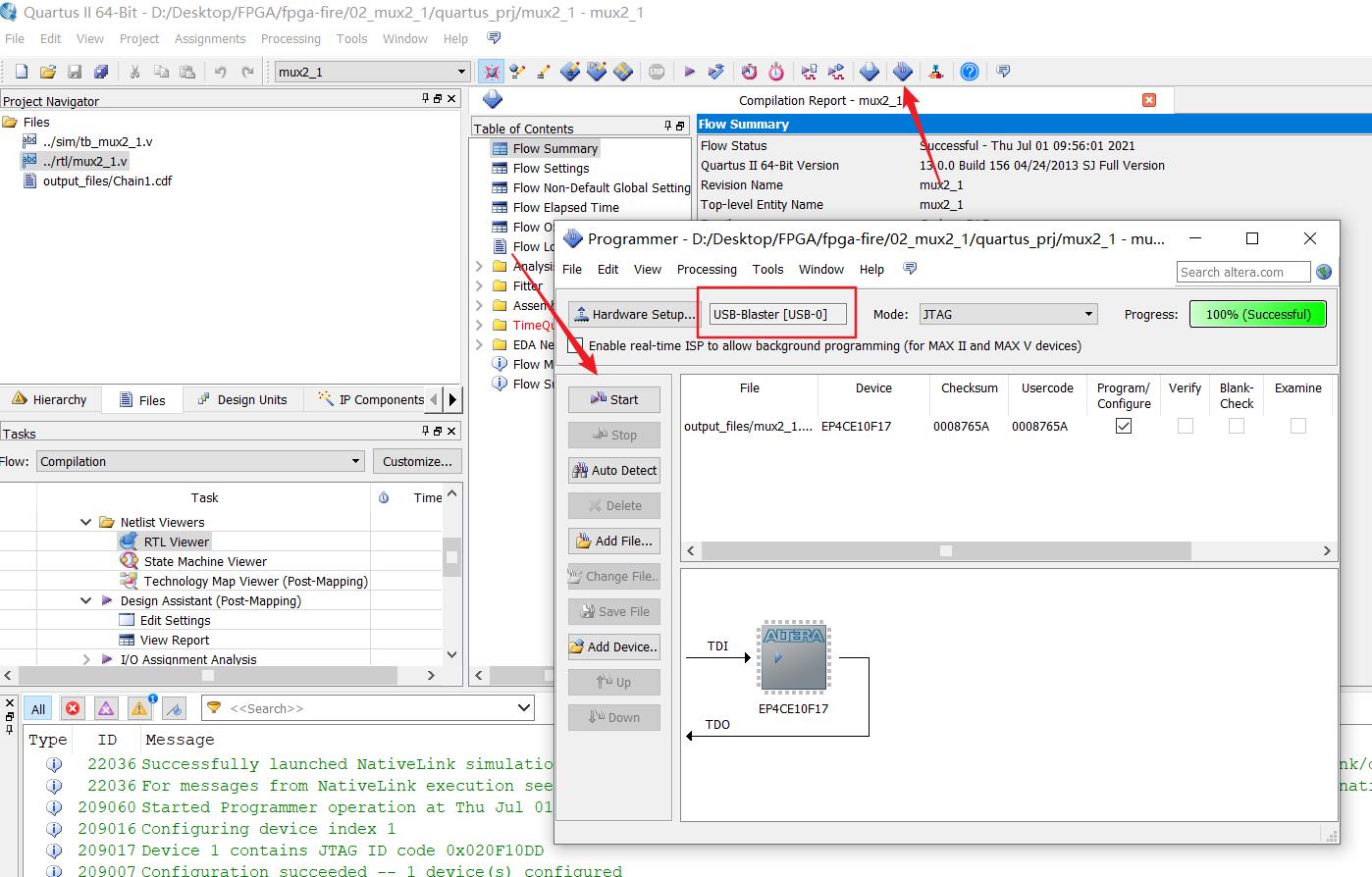

2、代码的分析和综合

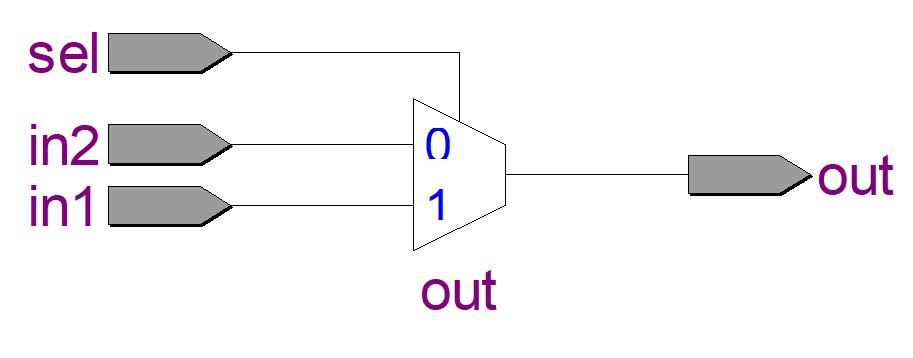

3、 查看RTL视图

4、Testbench代码的编写

//时间尺度、精度单位定义,决定“#(不可被综合,但在可综合代码中也可以写,只是会在仿真时表达效果,而综合时会自动被综合器优化掉)”

//后面的数字表示的时间尺度和精度,具体表达含义为:“时间尺度/时间精度”。

//为了以后编写方便我们将该句放在所有“.v”文件的开头,后面的代码示例将不再显示该句

`timescale 1ns/1ns

/*testbench的格式和待测试RTL模块的格式相同,也是以“module”开始以“endmodule”结束,所有的代码都要在它们中间编写。

不同的是在testbench中端口列表为空,因为testbench不对外进行信号的输入输出,

只是自己产生激励信号提供给内部实例化待测RTL模块使用,所以端口列表中没有内容,

只是列出“()”,当然也可以将“()”省略,括号后有个“;”不要忘记*/

module tb_mux2_1();

//********************************************************************//

//****************** Parameter and Internal Signal *******************//

//********************************************************************//

//reg define

//要在initial块和always块中被赋值的变量一定要是reg型

//(在testbench中待测试RTL模块的输入永远是reg型变量)

reg in1;

reg in2;

reg sel;

//wire define

//输出信号,我们直接观察,也不用在任何地方进行赋值,所以是wire型变量

//(在testbench中待测试RTL模块的输出永远是wire型变量)

wire out;

//********************************************************************//

//***************************** Main Code ****************************//

//********************************************************************//

/*initial语句是不可以被综合的,一般只在testbench中表达而不在RTL代码中表达。,

initial块中的语句上电后只执行一次,主要用于初始化仿真中要输入的信号,

初始化值在没有特殊要求的情况下给0或1都可以。如果不赋初值,仿真时信号会显示为

不定态(ModelSim中的波形显示红色)*/

initial

begin //在仿真中begin...end块中的内容都是顺序执行的,在没有延时的情况下几乎没有差别,看上去是同时执行的,如果有延时才能表达的比较明了;而在rtl代码中begin...end相当于括号的作用,在同一个always块中给多个变量赋值的时候要加上

in1 <= 1'b0;

in2 <= 1'b0;

sel <= 1'b0;

end

//in1:产生输入随机数,模拟输入端1的输入情况

always #10 in1 <= {$random} % 2; //取模求余数,产生非负随机数0、1,每隔10ns产生一次随机数

//in2:产生输入随机数,模拟输入端2的输入情况

always #10 in2 <= {$random} % 2;

//sel:产生输入随机数,模拟选择端的输入情况

always #10 sel <= {$random} % 2;

//下面的语句是为了在ModelSim仿真中直接打印出来信息便于观察信号变化的状态,也可以不使用下面的语句而直接观察仿真出的波形

//------------------------------------------------------------

initial begin

$timeformat(-9, 0, "ns", 6); //设置显示的时间格式,此处表示的是(打印时间单位为纳秒,小数点后打印的小数位为0位,时间值后打印的字符串为“ns”,打印的最小数量字符为6个)

$monitor("@time %t: in1=%b in2=%b sel=%b out=%b", $time, in1, in2, sel, out); //只要监测的变量(时间、in1, in2, sel, out)发生变化,就会打印出相应的信息

end

//------------------------------------------------------------

//********************************************************************//

//**************************** Instantiate ***************************//

//********************************************************************//

//待测试RTL模块的实例化,相当于将待测试模块放到测试模块中,并将输入输出对应连接上,测试模块中产生激励信号给待测试模块的输入,以观察待测试模块的输出信号是否正确

//------------- mux2_1_inst -------------

mux2_1 mux2_1_inst

(

//第一个是被实例化模块的名子,第二个是我们自己定义的在另一个模块中实例化后的名字。同一个模块可以在另一个模块中或不同的另外模块中被多次实例化,第一个名字相同,第二个名字不同

.in1(in1), //input in1,前面的“in1”表示被实例化模块中的信号,后面的“in1”表示实例化该模块并要和这个模块的该信号相连接的信号(可以取名不同,一般取名相同,方便连接和观察),“.”可以理解为将这两个信号连接在一起

.in2(in2), //input in2

.sel(sel), //input sel

.out(out) //output out

);

endmodule

5、ModelSim仿真波形

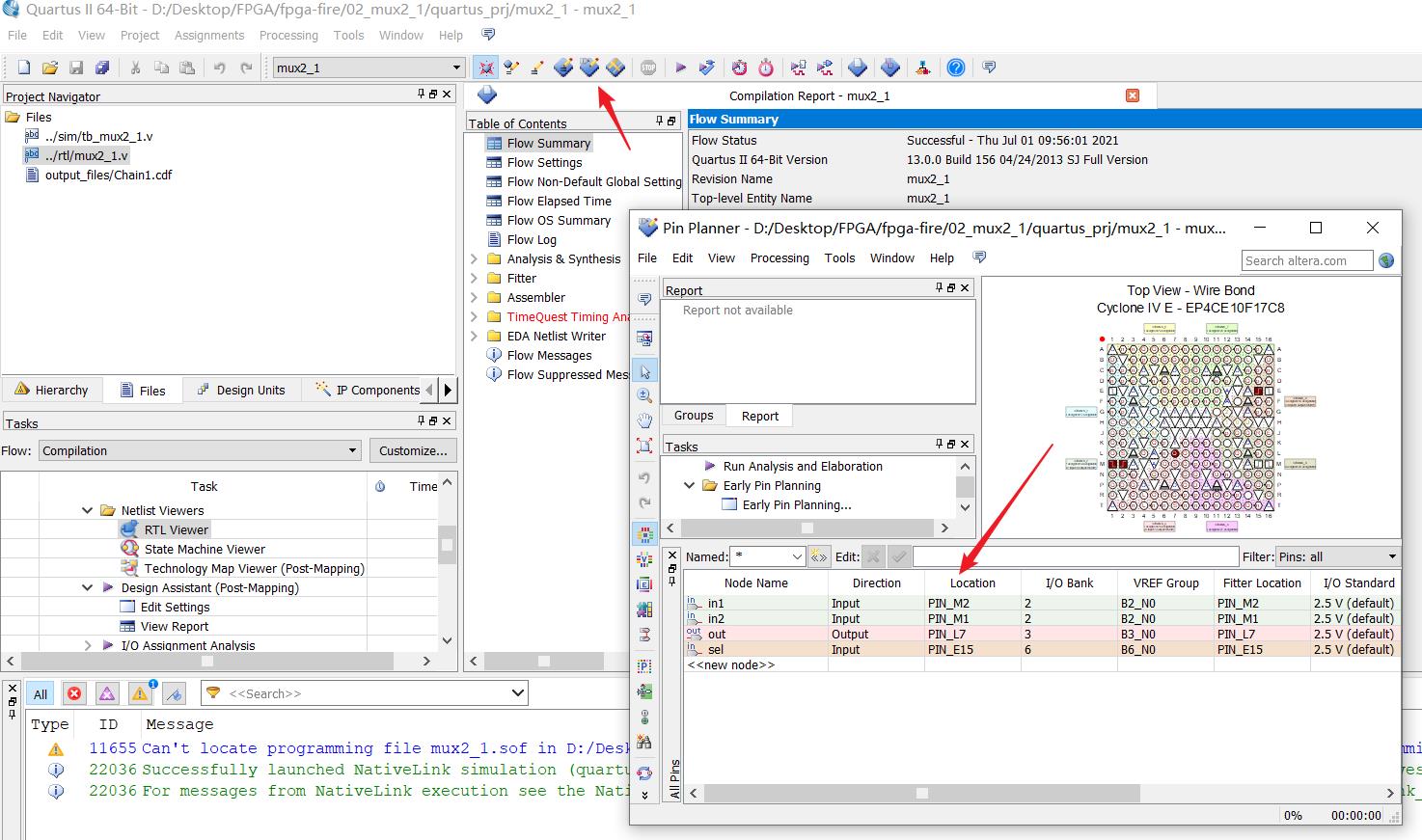

6、上板验证

以上是关于FPGA中,数据位数对数据选择器消耗的资源影响大吗?的主要内容,如果未能解决你的问题,请参考以下文章