基于ZYNQ移动机器人控制器设计控制器硬件方案选型(续)

Posted 信迈科技DSP+ARM+FPGA

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于ZYNQ移动机器人控制器设计控制器硬件方案选型(续)相关的知识,希望对你有一定的参考价值。

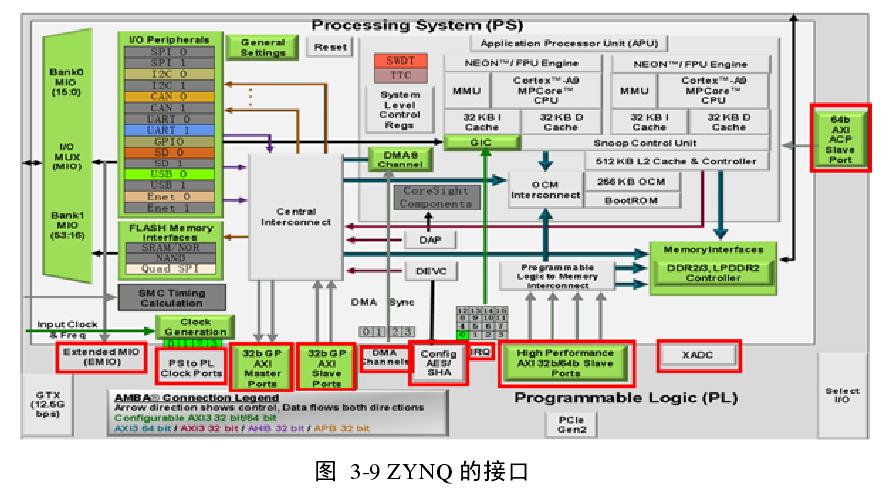

3.1.4 ZYNQ 的接口技术

本节我们来介绍 ZYNQ 的异构系统的接口技术,也即是其内部的总线体系。

在此之前,我们先来对比一下传统的 SoPC(System on a Programmale Chip)设计在

Zynq 之前,传统的方式无非两种:一是在 FPGA 上实现一个软核,如 Xilinx 的 Micro

Blaze,Altera 的 NiosII 等,另一种方式就是将 FGPA 和一个通用的嵌入式处理器相配

合(如 ARM)。两种方式均有较大的瓶颈:第一种主要在于软核的性能通常远远低于硬

核,并且耗费大量的 FPGA 资源;第二种主要在于 FPGA 和通用处理器的通信很容易成

为难以克服的瓶颈,尤其是当两者之间需要高带宽,低延时的大量数据传输时。

Zynq-7000 作为首款将高性能 ARM CrotexTM-A 系列处理器与高性能 FPGA 在单芯

片内紧密结合的产品,与现行其他方案诸如独立的 Cortex-A9 与 Xilinx 相比,其可以带

来如下优点:处理性能大大高于软核,克服了 FPGA 和 ARM 之间的通信瓶颈,直接带

来的后果就是设计成本降低;设计体积减小;设计风险降低;更灵活的设计。为了实现这

些优点,Xilinx 在设计 Zynq 的时候,面临的问题绝不仅仅要解决将不同工艺特征的处

理器和 FPGA 融合在单芯片上,并保证其良品率这么简单;更要面临的是设计高校的片

内器与 FPGA 之间的互联通路。

ZYNQ 平台的框架如图 3-9 所示,事实上只要是位于 PS 和 PL 边缘的接口(红色框

图标注),都可以纳入 PL 和 PS 间通信的范畴,只是它们在带宽、时延、灵活性等方面

略有差异。纵观所有的接口,本论文把 PS 和 PL 的通信归结为三种:基于总线级别的接

口;基于 EMIO;其他方式。下文我们将各自分述。

AXI 接口和协议

ZYNQ 内部的总线称为 AXI 总线。作为一种可以支持构建异构系统的全新平台,

其内部的总线体系必然比起常见的 Soc 有了新的变化。我们在做设计的时候,总是要结

合通信的需求,并考虑备选方案的的不同特性,选用不同的 AXI 接口类型。举个例子,

在做一些低速外设的时候,使用 AXI_GP 总线设计 AXI_Lite 接口即可完成外设的控制,

例如本论文中超声波模块 Ultrasonic IP 与 PS 的互联正是使用了 AXI_GP 中支持 lite 协议

的接口。充分的了解是运用的前提,因此在此有必要对 AXI 总线进行一定程度的分析介

绍。

首先是 AXI(Advanced e Xtensible Interface)协议。这是一种描述主从设备之间数

据传输方式是的片内总线协议。优势在于高带宽,高性能,低延迟。

其他接口

这里把剩下的放在一起做一下很简单的介绍。主要原因是前面的两种方式主要在

PS 和 PL 的通信中起数据传输作用,而且一般量会比较大。而其他的就主要就是一些信

号,功能为主,数据传输只是实现功能的一个方式,一般量也比较小,比如像时钟呀,

以上是关于基于ZYNQ移动机器人控制器设计控制器硬件方案选型(续)的主要内容,如果未能解决你的问题,请参考以下文章