计算机组成原理 — CPU — 缓存访问

Posted 范桂飓

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了计算机组成原理 — CPU — 缓存访问相关的知识,希望对你有一定的参考价值。

目录

文章目录

CPU 缓存

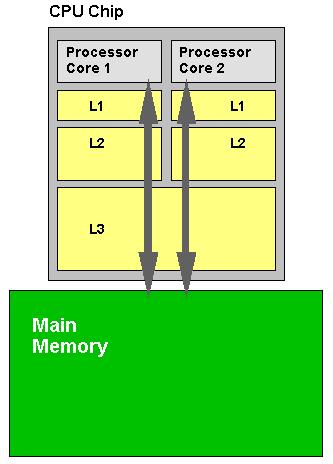

CPU Cache(CPU 缓存)就是数据交换的缓冲区,往往都是 RAM(断电即掉的非永久储存),它们的作用就是帮助硬件更快地响应。CPU 内部集成了计算机系统中速度最快的 Cache(L1、L2、L3 Cache)。

CPU Cache 定义为 CPU 与 Main Memory(主存)之间的临时数据交换器,它的出现是为了解决 CPU 运行处理速度与 Main Memory 读写速度不匹配的矛盾 —— CPU 访问 CPU Cache 的速度比 Main Memory 的速度快得多。

CPU Cache 一般直接集成在 CPU 芯片上,要求尽可能地靠近 CPU,所以它的成本异常昂贵,更大的 CPU Cache 意味着更高的缓存命中率,也意味着更快的速度。

CPU Cache 的运行原理

根据局部性访问原理,CPU 往往需要重复处理相同的数据、重复执行相同的指令,如果这部分数据、指令 CPU 能在 CPU Cache 中找到,那么 CPU 就不需要从 Main Memory 或 Hardware Disk 中再读取数据、指令,从而减少了整机的响应时间。

有了 CPU Cache 之后,CPU 可以直接在 CPU Cache 里读取到想要的数据,称之为命中(hit)。如果 CPU 在 L1 Cache 中找到所需要的资料要用的时间为 3 个周期左右,那么在 L2 Cache 找到资料的时间就要 10 个周期左右,L3 Cache 所需时间为 50 个周期左右;而如果要到内存上去找,则可能需要几百个周期的时间。

L1 的运行速度很快,但是它的数据容量很小,CPU 能在 L1 里命中的概率大概在 80% 左右(日常使用的情况下),L2、L3 也类似如此。这样一来,CPU 需要在 Main Memory 中读取的数据大概为 5%-10%,其余数据命中全部可以在 L1、L2、L3 中做到,大大减少了系统的响应时间,总的来说,所有 CPU 读取数据的顺序都是先查 CPU Cache 再查 Main Memory。

三级缓存(L1、L2、L3)

以近代 CPU 的视角来说,三级缓存都是集成在 CPU 内的缓存,它们的作用都是作为 CPU 与主内存之间的高速数据缓冲区,L1 最靠近 CPU 核心;L2 其次;L3 再次。运行速度方面:L1 最快、L2 次快、L3 最慢;容量大小方面:L1 最小、L2 较大、L3 最大。

CPU 会先在最快的 L1 中寻找需要的数据,找不到再去找次快的 L2,还找不到再去找 L3,L3 都没有那就只能去内存找了。

L1、L2、L3 可以说是各有特点,下面我们就分开来讲一下。

L1 Cache

L1 Cache 这个名词出现应该是在 Intel 公司 Pentium 处理器时代把缓存开始分类的时候,当时在 CPU 内部集成的 CPU Cache 已经不能满足整机的性能需求,而制造工艺上的限制不能在 CPU 内部大幅提高缓存的数量,所以出现了集成在主板上的缓存,当时人们把 CPU 内部集成的 CPU Cache 称为 L1 Cache。

L1 Cache 还可以细分为:

- 一级数据缓存(Data Cache,D-Cache,L1d):用于存放数据。

- 一级指令缓存(Instruction Cache,I-Cache,L1i):执行数据的指令解码。

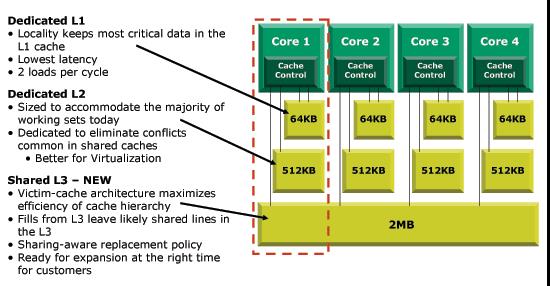

两者可同时被 CPU 访问,减少了 CPU 多核心、多线程争用缓存造成的冲突,提高了处理器的效能。一般 CPU 的 L1i 和 L1d 具备相同的容量,例如 I7-8700K 的 L1 即为 32KB+32KB。

L2 Cache

L2 Cache 的主要作用是当 CPU 在 L1 Cache 中没读取到所需要的数据时再把数据展示给 CPU 作筛选。

L2 Cache 比 L1 Cache 的容量要更大,但是 L2 Cache 的速率要更慢。因为有 2 个:

- L2 比 L1 要更远离 CPU Core,L1 是最靠近 CPU 核心的缓存,CPU 需要读取 L2 的数据从物理距离上比 L1 要更远;

- L2 的容量比 L1 更大,打个简单的比喻,在小盒子里面找东西要比在大房间里面找要方便快捷。

这里也可以看出,缓存并非越大越好,越靠近 CPU 核心的缓存运行速率越快越好,非最后一级缓存的缓存容量自然是够用即可。

L2 Cache 实际上就是 L1 Cache 跟 Main Memory 之间的缓冲器。在 2006 年的时间点上,Intel 和 AMD 当家在售的几款处理器可以看出他们对最后一级缓存不同的见解:

-

Intel Core Duo 不同于它的前辈 Pentium D、EE,采用了双核心共享的 2M L2 二级缓存,是属于当时最先二级缓存架构,即 “Smart Cache” 共享缓存技术,这种技术沿用到以后的 Intel 推出的所有多核心处理器上;

-

AMD Athlon 64X2 处理器则是每个 CPU 核心都具备独立的二级缓存,Manchester 核心的处理器为每核心 512KB、Toledo 核心为每核心 1MB,两个核心之间的缓存的数据同步是通过 CPU 内置的 SRI(系统请求接口)控制,这样的数据延迟及占用资源情况都要比 Intel 的 Pentium D、EE 核心要好,但还是比不上 Core 为代表的 Smart Cache 缓存共享。

L3 Cache

最初出现 L3 Cache 的应该是 AMD 的 K6-III 处理器,当时受限于制造工艺,L3 Cache 只能集成在主板上。然后 Intel 首次出现 L3 Cache 的是 Itanium 安腾服务器处理器,接着就是 P4EE 和至强 MP。

L3 Cache 的出现其实对 CPU 性能提升呈一个爬坡曲线 —— L3 从 0 到 2M 的情况 CPU 性能提升非常明显,L3 从 2M 到 6M 提升可能就只有 10% 不到了,这是在近代 CPU 多核共享 L3 的情况下,当 L3 集成进 CPU 正式成为 CPU 内部缓存后,CPU 处理数据时只有 5% 需要在内存中调用数据,进一步地减少了内存延迟,使系统的响应更为快速。

同理,L3 Cache 作为 L2 Cache 与 Main Memory 之间的缓冲器,主要体现在提升处理器大数据处理方面的性能,对游戏表现方面有较大的帮助。

以上是关于计算机组成原理 — CPU — 缓存访问的主要内容,如果未能解决你的问题,请参考以下文章