编码器/译码器(Verilog HDL)|计算机组成

Posted 桃陉

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了编码器/译码器(Verilog HDL)|计算机组成相关的知识,希望对你有一定的参考价值。

前言

编码与译码是一对相反的操作,其中编码是将2n个电路状态转换为n个二进制结果;译码是将n个二进制结果转换为2n个电路状态。下面主要介绍最经典的8-3编码器与3-8译码器。

1. 8-3编码器

8-3编码器即把8个1位的二进制数转换位3个1位的二进制结果输出。我们根据转换表来编写代码,转换表如下,从I0到I7(从低位到高位)表示的是编码器的输入,从Y2到Y0(从高位到低位)表示的是编码器的输出。在进行转换时我们只需要注意到出现在最高位的1即可。

代码如下:

module encoder8_3(

input [7:0]I,

output reg [2:0]Y

);

always@(I) begin

//从高位到低位判断出现1的位置,并进行转换

if(I[7]==1) Y=3'b111;

else if(I[6]==1) Y=3'b110;

else if(I[5]==1) Y=3'b101;

else if(I[4]==1) Y=3'b100;

else if(I[3]==1) Y=3'b011;

else if(I[2]==1) Y=3'b010;

else if(I[1]==1) Y=3'b001;

else if(I[0]==1) Y=3'b000;

else Y=3'b000;

end

endmodule

仿真代码如下:(只取了8之前的数字,自己可以继续进行扩充)

module encoder8_3_sim();

reg [7:0]I=8'b00000000;

wire [2:0]Y;

encoder8_3 uut(.I(I),

.Y(Y));

initial begin

#100 I=8'b00000001;

#100 I=8'b00000010;

#100 I=8'b00000011;

#100 I=8'b00000100;

#100 I=8'b00000101;

#100 I=8'b00000110;

#100 I=8'b00000111;

#100 I=8'b00001000;

end

endmodule

仿真波形结果如下:

2. 3-8译码器

译码是编码的逆过程,可以将n位的二进制代码,译为2n种电路状态。代码的变量介绍如下:

| 变量 | 长度 | 输入/输出 | 含义 |

|---|---|---|---|

| a | 3 | input | 3-8译码器三位二进制输入 |

| ena | 1 | input | 3-8译码器使能信号,为0则归0,为1则输出对应的译码信号 |

| y | 8 | output | 3-8译码器对应的8种电路状态输出 |

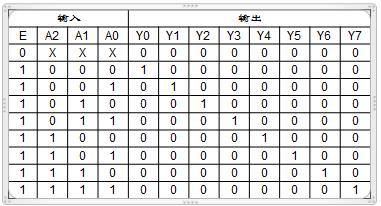

同样转换关系表如下图所示:

代码如下:

module decoder3_8(

input [2:0]a,

input ena,

output reg [7:0]y);

always@(*) begin

if(ena==0) y=8'b00000000;

else begin

case(a)

3'b000:y=8'b00000001;

3'b001:y=8'b00000010;

3'b010:y=8'b00000100;

3'b011:y=8'b00001000;

3'b100:y=8'b00010000;

3'b101:y=8'b00100000;

3'b110:y=8'b01000000;

3'b111:y=8'b10000000;

default:y=8'b00000000;

endcase

end

end

endmodule

仿真代码如下:

module decoder3_8_sim();

reg [2:0]a=3'b000;

reg ena=1;

wire [7:0]y;

decoder3_8 uut(.a(a),

.ena(ena),

.y(y));

initial begin

#100 a=3'b001;

#100 a=3'b010;

#100 a=3'b011;

#100 a=3'b100;

#100 a=3'b101;

#100 a=3'b110;

#100 a=3'b111;

#100 a=3'b010;

ena=0;

#100 a=3'b111;

end

endmodule

仿真波形结果如下:

以上是关于编码器/译码器(Verilog HDL)|计算机组成的主要内容,如果未能解决你的问题,请参考以下文章