DDR3基本概念 - 8n pre-fetch architecture的含义

Posted Linux学习之路

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了DDR3基本概念 - 8n pre-fetch architecture的含义相关的知识,希望对你有一定的参考价值。

原文链接:https://blog.csdn.net/tbzj_2000/article/details/90762749

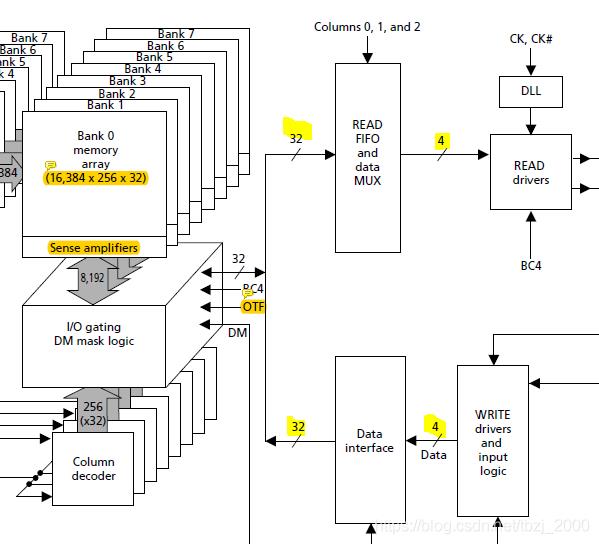

在DDR3标准中提到"The DDR3 SDRAM uses a 8n prefetch architecture to achieve high-speed operation".

-

n表示DDR内存颗粒的位宽(一般为4/8/16bits). 8表示burst的最大数据量。为了获取最佳的性能,DDR3一次读写数据位数为8 x n。如下图所示,READ 通道有一个32数据到8个4位burst数据的转换;Write通道有一个8个4位写数据到32位写数据的转换。该读写结构的好处:

-

存储器内部电路仅需以端口时钟的1/8频率工作. 一次读写32位 。通过READ FIFO and data MUX和 Data interface模块和 DDR端口上 的高频端口时钟交互。

内部读写数据位宽都是32位,提高了读写效率

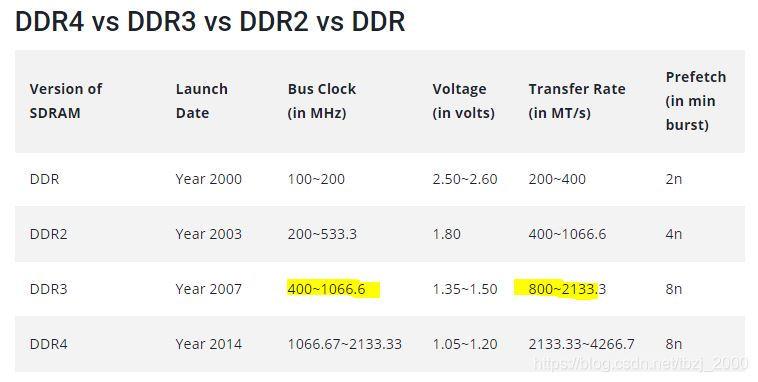

以上为DDR ~ DDR4各代DDR产品的prefetch burst长度对比。

以上是关于DDR3基本概念 - 8n pre-fetch architecture的含义的主要内容,如果未能解决你的问题,请参考以下文章