鲁棒性检查(中)

Posted KuoGavin

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了鲁棒性检查(中)相关的知识,希望对你有一定的参考价值。

文章目录

10.5 时钟门控检查(Clock Gating Checks)

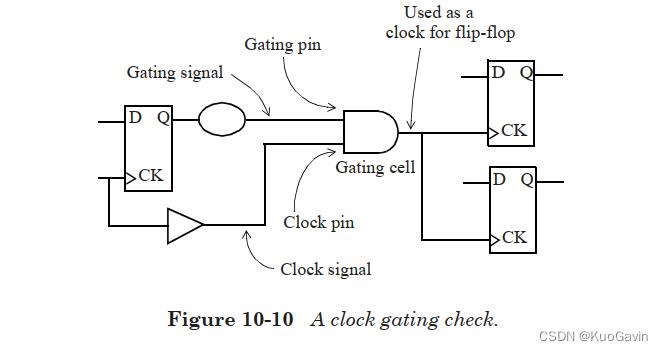

当一个门控信号(gating signal)可以控制逻辑单元中时钟信号(clock signal)的路径时,将会执行时钟门控检查(clock gating check),一个示例如图10-10所示。逻辑单元与时钟相连的引脚称为时钟引脚(clock pin),与门控信号相连的引脚称为门控引脚(gating pin),产生时钟门控的逻辑单元也称为门控单元(gating cell)。

进行时钟门控检查的条件之一是:必须将通过门控单元的时钟用作下游的时钟。下游时钟的使用可以是触发器的时钟、也可以是扇出到输出端口、也可以是作为衍生时钟的主时钟。如果时钟不用作门控单元之后的下游时钟,则不会推断出时钟门控检查。

时钟门控检查的另一个条件针对的是门控信号:门控引脚上的信号不应是时钟,或者如果是时钟,也不应将其用作下游时钟(例如本节稍后要介绍的将时钟用作门控信号的一个示例)。

在一般情况下,时钟信号和门控信号不需要连接到同一个逻辑单元(例如与门、或门),但是可以输入到任意逻辑块。在这种情况下,为了推断出时钟门控检查,检查的时钟引脚和检查的门控引脚必须扇出到公共输出引脚。

可推断出两种时钟门控检查:

- 高电平(Active-high)有效时钟门控检查:门控单元具有“与”功能或“与非”功能;

- 低电平(Active-low)有效时钟门控检查:门控单元具有“或”功能或“或非”功能;

高电平有效和低电平有效是指门控信号的逻辑状态,该逻辑状态用以使能门控单元输出端的时钟信号。如果门控单元是门控关系不明显的复杂功能,例如多路复用器(MUX, multiplexer)或异或门(XOR),则

S

T

A

STA

STA输出通常会给出警告,提示没有推断出时钟门控检查。但是,可以通过使用命令set_clock_gating_check为门控单元显式地指定时钟门控关系。在这种情况下,如果set_clock_gating_check命令与门控单元的功能不一致,则

S

T

A

STA

STA通常会给出警告。我们将在本节稍后部分介绍此类命令的示例。

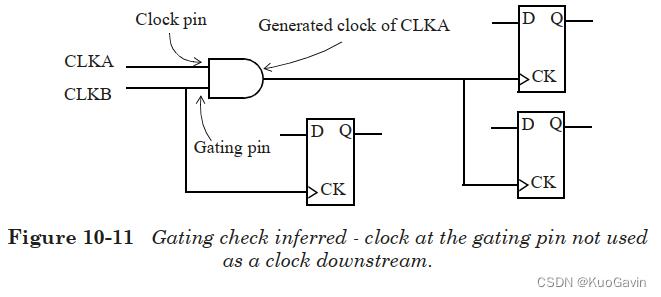

如前所述,只有当时钟不用作下游时钟时,它才可以用作门控信号,考虑图10-11中的示例。由于定义了 C L K A CLKA CLKA的衍生时钟,因此 C L K B CLKB CLKB不用作下游时钟,即 C L K B CLKB CLKB的路径被衍生时钟的定义阻塞了。因此,针对这个与门单元会推断出时钟 C L K A CLKA CLKA的时钟门控检查。

高电平时钟门控(Active-High Clock Gating)

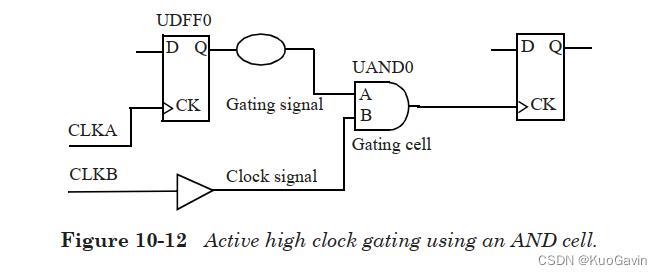

我们现在检视一个高电平时钟门控检查的时序关系。发生在"与"和"非与"单元;一个与单元例子如图10-12所示。门控单元的 B B B引脚是时钟信号, A A A引脚是门控信号。

我们假定时钟 C L K A CLKA CLKA和时钟 C L K B CLKB CLKB具有相同的波形。

create_clock -name CLKA -period 10 -waveform 0 5 \\

[get_ports CLKA]

create_clock -name CLKB -period 10 -waveform 0 5 \\

[get_ports CLKB]

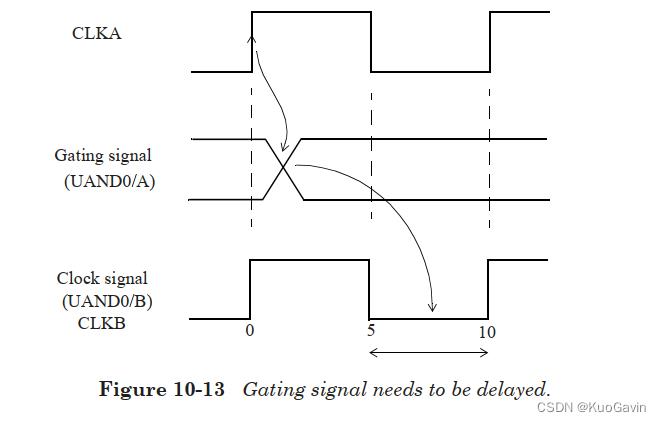

因为它是一个与门单元,所以门控信号引脚 U A N D 0 / A UAND0 / A UAND0/A上为高电平时才会打开门控单元,并允许时钟传播通过。时钟门控检查旨在验证门控引脚的电平切换不会为扇出时钟创建时钟有效沿。对于上升沿触发的逻辑,这意味着门控信号的上升沿发生在时钟的无效周期内(当其为低电平时)。类似地,对于下降沿触发的逻辑,门控信号的下降沿应仅在时钟为低电平时产生。注意,如果时钟同时驱动上升沿和下降沿触发的触发器,则门控信号的任何边沿(上升沿或下降沿)都必须仅在时钟为低电平时产生。图10-13给出了一个在有效周期期间门控信号电平切换的示例,该信号需要延迟才能通过时钟门控检查。

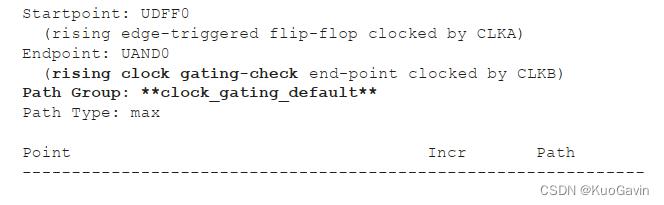

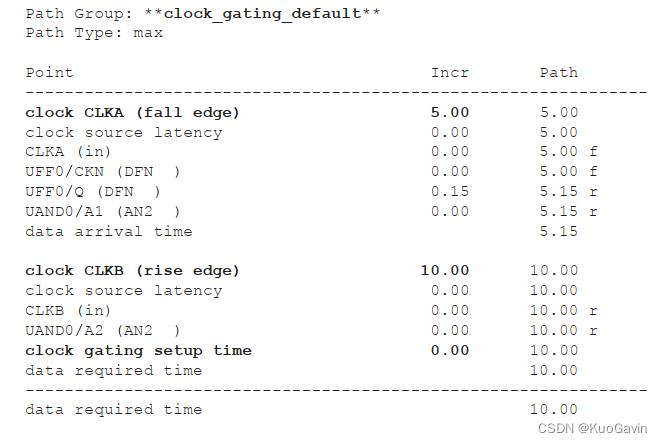

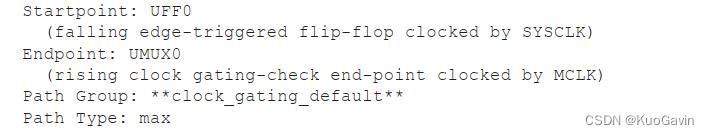

高电平有效时钟门控的建立时间检查可确保门控信号的电平改变发生在时钟变为高电平之前。以下是建立时间检查的路径报告:

请注意,终点(Endpoint)处说明这是时钟门控检查。另外,从Path Group一行中可以看出该路径属于clock_gating_default路径组中。该检查能确保门控信号在

10

n

s

10ns

10ns处的时钟

C

L

K

B

CLKB

CLKB下一个上升沿之前改变。

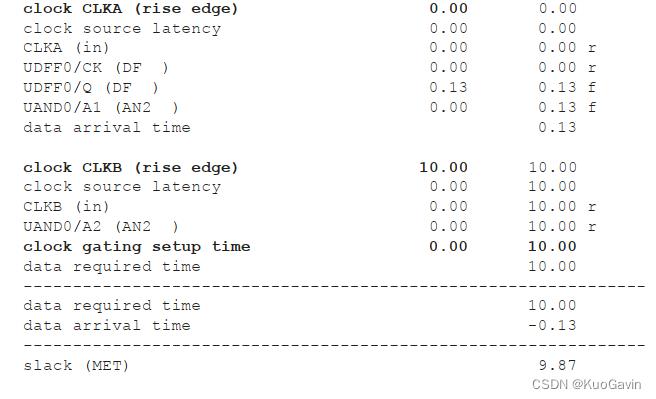

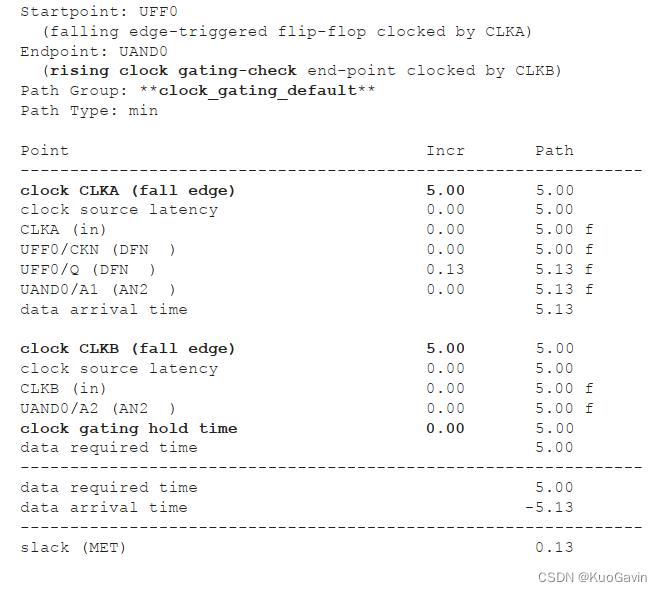

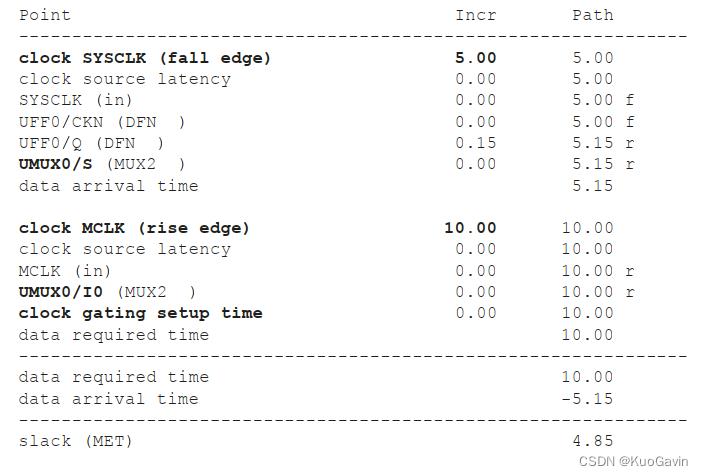

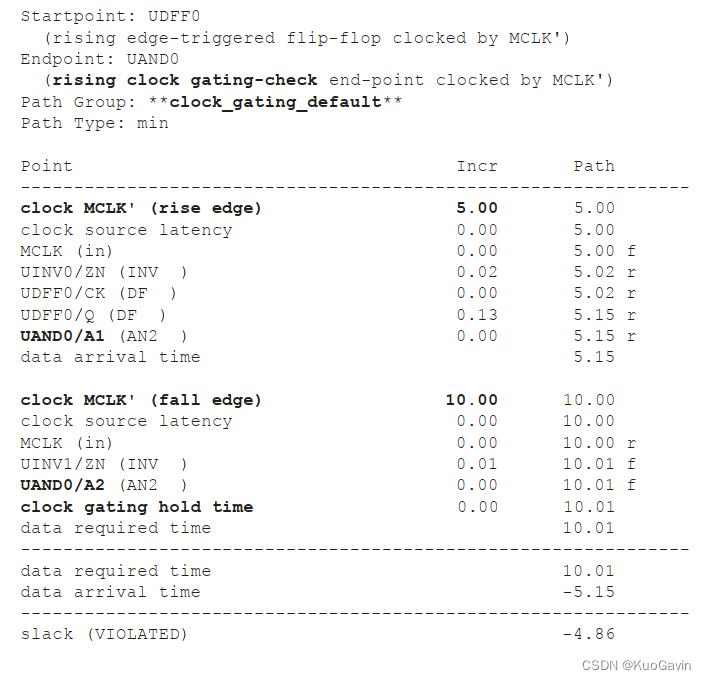

高电平有效时钟门控的保持时间检查要求门控信号仅在时钟的下降沿之后才可以发生变化。以下是保持时间检查的路径报告:

时钟门控的保持时间检查失败了,因为在 5 n s 5ns 5ns处的 C L K B CLKB CLKB下降沿之前,门控信号发生了改变。如果在 U D F F 0 UDFF0 UDFF0 / Q 和 U A N D 0 / A 1 Q和UAND0 / A1 Q和UAND0/A1引脚之间添加了 5 n s 5ns 5ns的延迟,则时钟门控的建立时间和保持时间检查都会通过,即门控信号仅在指定的时间窗口内发生变化。

从前文可以看到保持时间要求是非常大的,这是由于产生门控信号的时钟沿和门控单元时钟信号的有效沿是相同沿(上升沿或下降沿)导致的,这可以通过使用另一种类型的触发器(例如下降沿触发的触发器)产生门控信号来解决。下面将介绍这样的示例。

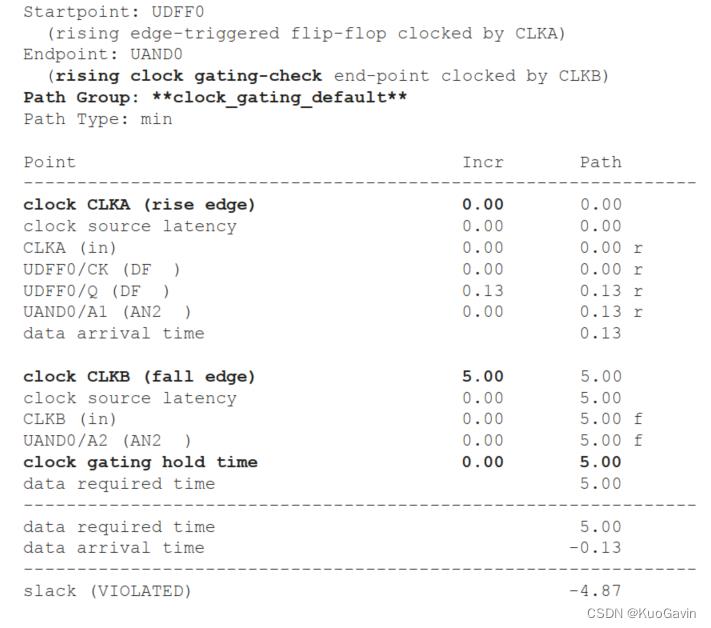

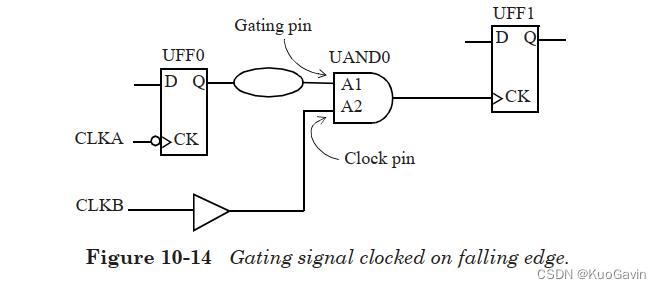

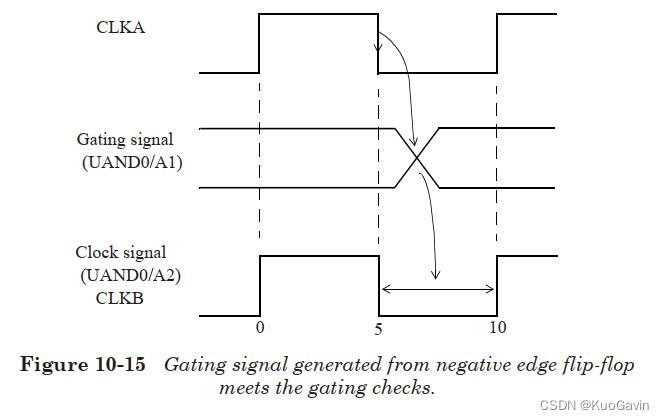

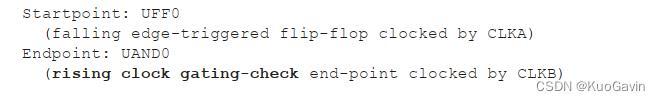

在图10-14中,触发器 U F F 0 UFF0 UFF0由时钟 C L K A CLKA CLKA的下降沿触发。安全的时钟门控意味着触发器 U F F 0 UFF0 UFF0的输出(门控信号)必须在门限时钟的无效时间改变,也就是 5 n s 5ns 5ns和 10 n s 10ns 10ns之间。

与图10-14中的示意图相对应的信号波形如图10-15所示:

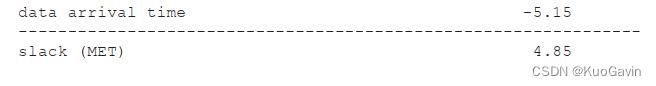

以下是时钟门控的建立时间检查报告:

以下是时钟门控的保持时间检查报告。请注意,在此新设计中,保持时间检查更容易满足要求。

由于产生门控信号的时钟沿(下降沿)与门控时钟相反(高电平有效),因此很容易满足建立时间和保持时间的要求。这也是门控时钟最常用的结构。

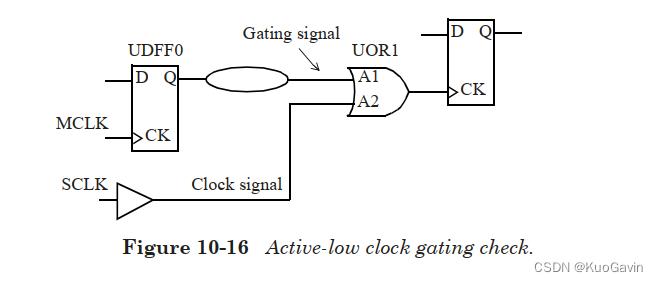

低电平时钟门控(Active-Low Clock Gating)

图10-16给出了低电平有效时钟门控检查的示例:

create_clock -name MCLK -period 8 -waveform 0 4 \\

[get_ports MCLK]

create_clock -name SCLK -period 8 -waveform 0 4 \\

[get_ports SCLK]

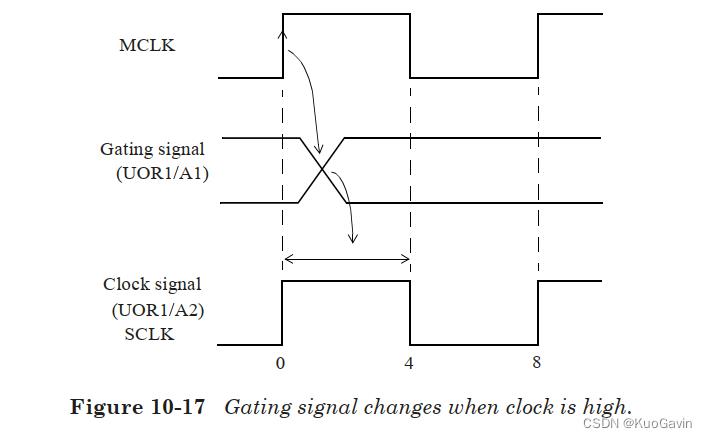

对于上升沿触发逻辑,低电平时钟门控验证到达有效时钟周期门控信号的上升沿(当为高电平)。如前所述,关键在于门控信号不应使门控时钟的输出产生有效沿。当门控信号为高电平时,时钟无法通过。因此,只有在时钟为高电平时,门控信号才允许切换,如图10-17所示。

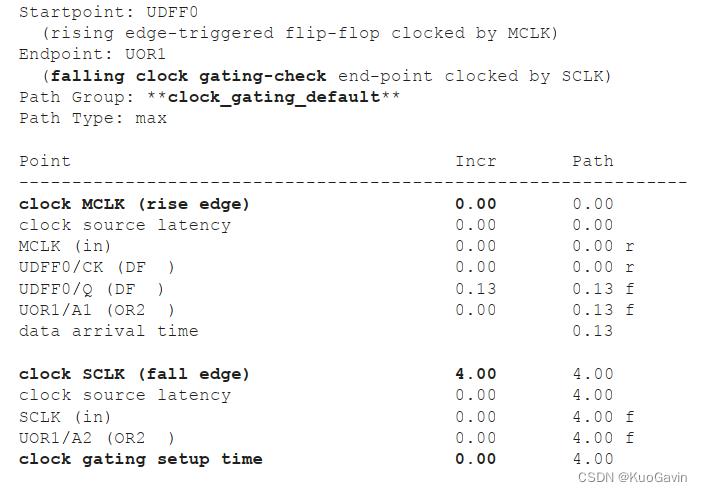

以下是低电平有效时钟门控的建立时间检查报告。该检查可确保门控信号在时钟沿变为无效状态(在这种情况下为 4 n s 4ns 4ns)之前到达。

以下是时钟门控的保持时间检查报告。此检查可确保门控信号仅在时钟信号的上升沿(在这种情况下为 0 n s 0ns 0ns)之后才发生变化。

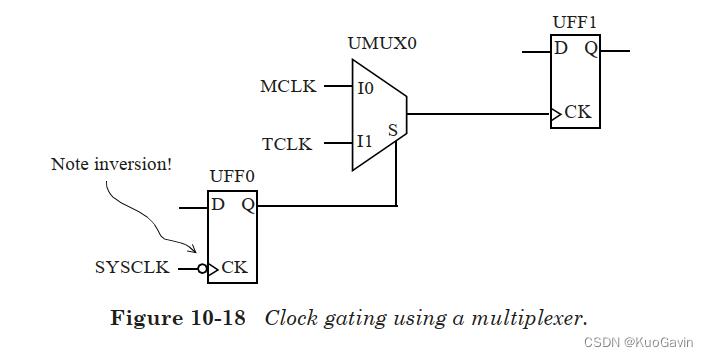

使用多路复用器的时钟门控(Clock Gating with a Multiplexer)

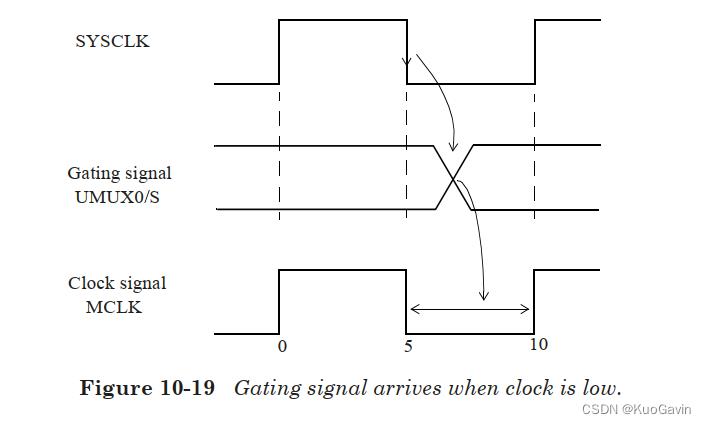

图10-18给出了使用多路复用器单元进行时钟门控的示例。多路复用器输入上的时钟门控检查可确保多路复用器选择信号在正确的时间到达,以在 M C L K MCLK MCLK和 T C L K TCLK TCLK之间进行“干净”(clean)的切换。对于这个例子,我们感兴趣的是 M C L K MCLK MCLK,假设 T C L K TCLK TCLK为低电平时选择信号进行切换。这意味着多路复用器的选择信号应仅在 M C L K MCLK MCLK为低电平时进行切换,这类似于高电平有效时钟门控检查。

时序关系如图10-19所示,多路复用器的选择信号必须在 M C L K MCLK MCLK为低电平时到达。同样,假设选择信号改变时 T C L K TCLK TCLK为低电平。

由于门控单元是多路复用器,因此不会自动推断出时钟门控检查,在 S T A STA STA期间会报告出以下信息:

Warning: No clock-gating check is inferred for clock MCLK at

pins UMUX0/S and UMUX0/I0 of cell UMUX0.

Warning: No clock-gating check is inferred for clock TCLK at

pins UMUX0/S and UMUX0/I1 of cell UMUX0.

但是,通过使用set_clock_gating_check命令可以强制执行时钟门控检查。

set_clock_gating_check -high [get_cells UMUX0]

# The -high option indicates an active-high check.

set_disable_clock_gating_check UMUX0/I1

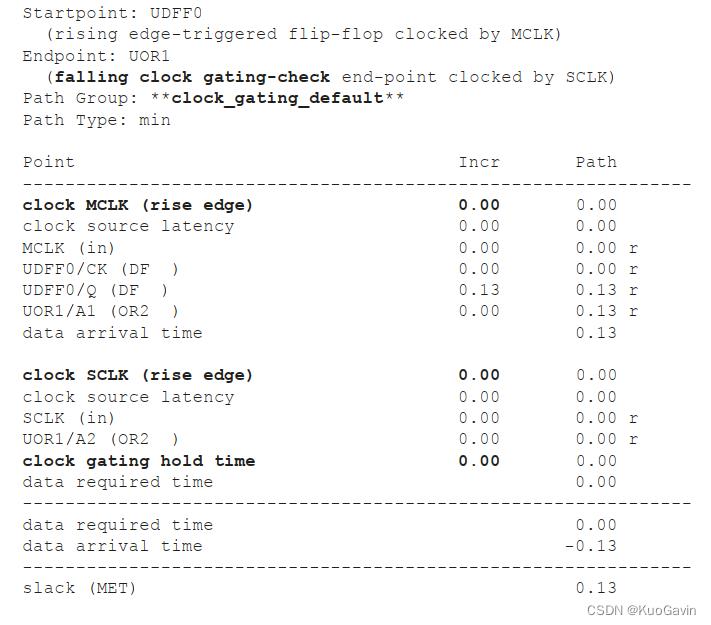

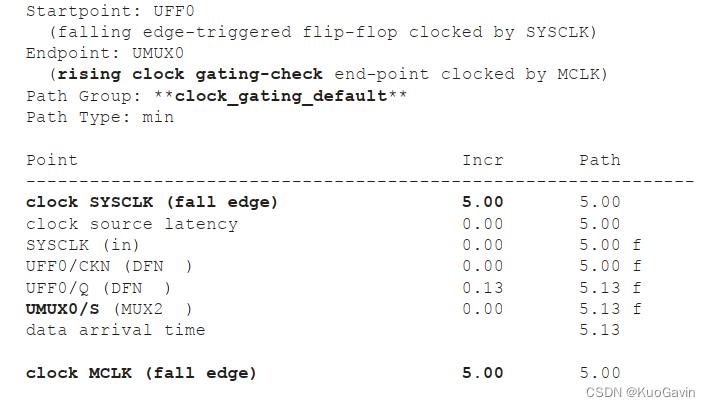

第一条命令中的-high选项表示这是高电平有效的时钟门控检查,第二条命令中的禁止检查将关闭特定引脚上的时钟门控检查,因为我们不考虑该引脚。以下是建立时间检查的路径报告:

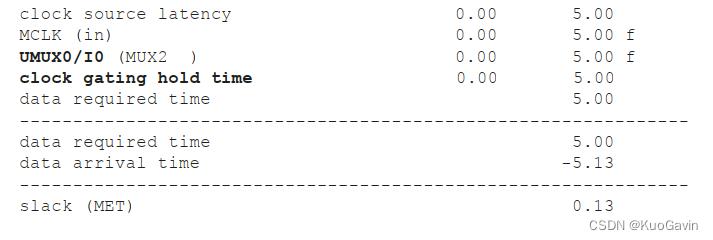

接下来是保持时间时钟门控检查的报告:

带有时钟反相的时钟门控检查(Clock Gating with Clock Inversion)

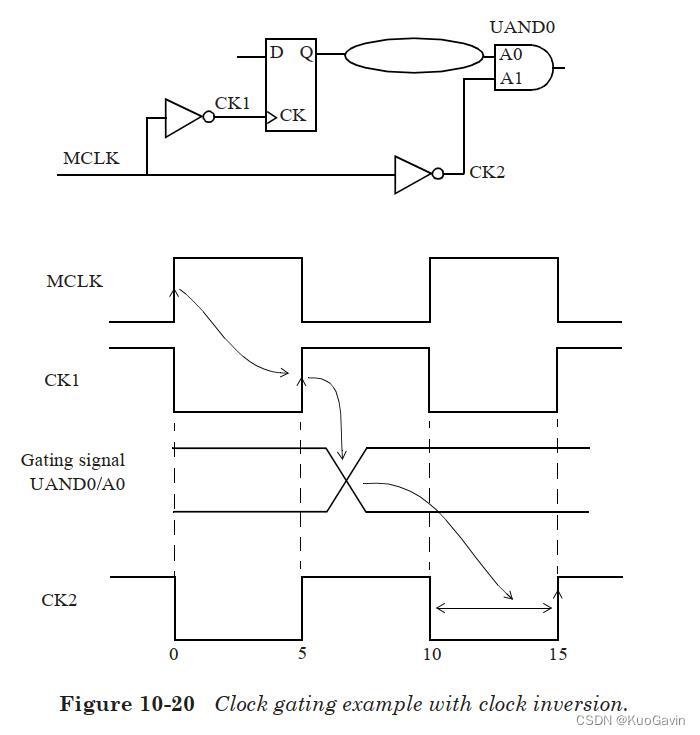

图10-20显示了另一个时钟门控示例,其中产生门控信号的触发器时钟被反相了。由于门控单元是与门单元,因此门控信号必须仅在时钟信号为低电平时才能切换,这定义了时钟门控的建立时间和保持时间检查。

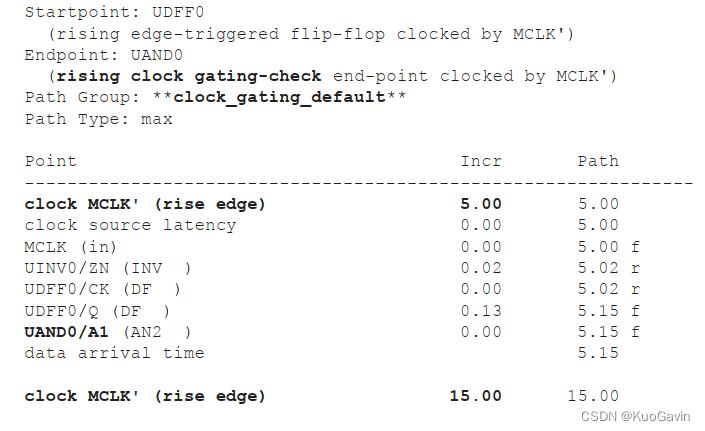

以下是时钟门控的建立时间检查报告:

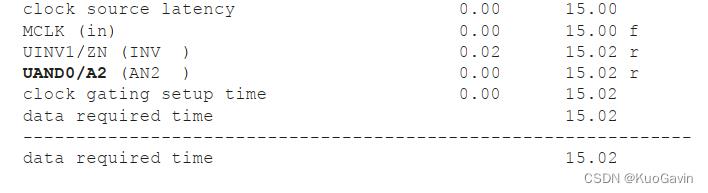

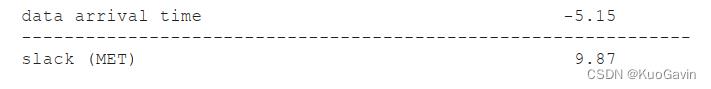

请注意,建立时间检查会验证数据是否在 15 n s 15ns 15ns处的 M C L K MCLK MCLK沿之前发生改变。以下是时钟门控的保持时间检查报告:

保持时间检查可验证门控信号是否在 10 n s 10ns 10ns处的 M C L K MCLK MCLK下降沿之前发生了改变。

如果门控单元是一个复杂的单元并且建立时间和保持时间检查不够明显,则可以使用set_clock_gating_check命令来指定对门控单元的门控信号进行建立时间和保持时间检查。建立时间检查会去确保门控信号在时钟信号的有效沿之前是稳定的,建立时间检查的失败可能会导致门控单元输出端出现毛刺。保持时间检查可验证门控信号在时钟信号的无效沿处是否稳定。以下是set_clock_gating_check命令的一些示例:

set_clock_gating_check -setup 2.4 -hold 0.8 \\

[get_cells U0/UXOR1]

# Specifies the setup and hold time for the clock

# gating check at the specified cell.

set_clock_gating_check -high [get_cells UMUX5]

# Check is performed on high level of clock. Alternately, the

# -low option can be used for an active-low clock gating check.

10.6 功耗管理(Power Management)

功耗管理是任何设计及其实现方式的一个重要方面。在设计实现(implementation)过程中,设计人员通常需要评估在速度、功耗和面积之间权衡(trade-off)的不同方法。

如3.8 功耗建模(power dissipation modeling)所述,一个设计的逻辑部分中消耗的功率包括漏电功率(leakage power)和有功功率(active power)。 此外,模拟部分和 I O IO IO缓冲器(尤其是具有主动匹配(active termination)功能的)会耗散与功能无关且非漏电的功率。在本节中,我们重点讨论设计中逻辑部分所耗散功率的权衡。

通常,管理由标准单元和存储器组成的数字逻辑的功率影响有两个注意事项:

-

使设计的总有功功率最小化:设计人员将确保总功耗保持在特定的功耗极限之内。设计的不同工作模式可能会有不同的极限值,此外,设计中使用的不同供电电源也会有不同的极限值。

-

使待机模式下设计的功耗最小化:对于电池供电的设备(例如手机),这是一个重要的考虑因素,其目的是使待机模式下的功耗最小。待机模式下的功耗等于漏电功耗加上待机模式下有效逻辑的任何功耗。如上所述,可能存在其它模式,例如睡眠模式,其对功耗的约束有所不同。

本节将介绍各种功耗管理方法,这些方法中的每一种都有其优缺点。

10.6.1 时钟门控(Clock Gating)

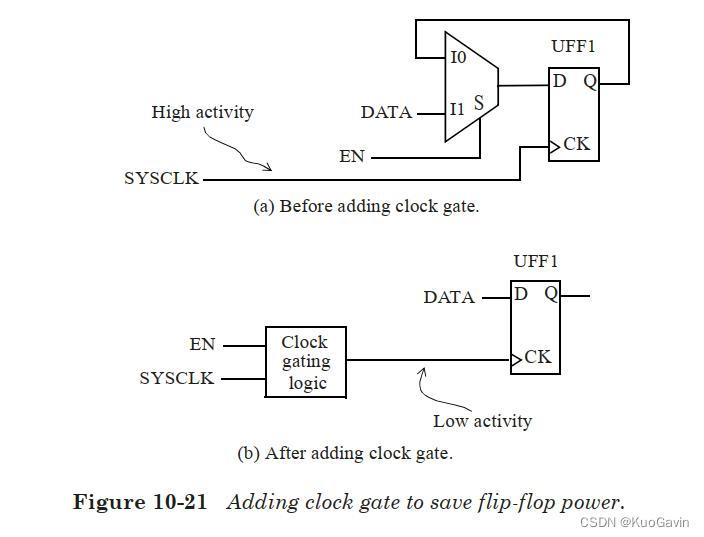

如3.8 功耗建模(power dissipation modeling)所述,触发器的时钟翻转是总功耗的重要组成部分。即使触发器的输出未切换,触发器也会由于时钟切换而消耗功率。考虑图10-21(a)中的示例,其中触发器仅在使能信号 E N EN EN处于有效状态时才接收新数据,否则将保持先前的状态。在 E N EN EN信号处于无效状态期间,时钟在触发器处的翻转不会引起任何输出变化,但是仍然导致了触发器内部的功率消耗。时钟门控的目的是:通过在触发器输入无效的时钟周期内消除触发器的时钟翻转来最大程度地减少这种影响。通过时钟门控进行的逻辑重组会在触发器时钟引脚上引入时钟门控,图10-21给出了此时钟门控的示例:

因此,时钟门控可确保仅在其数据输入端有新数据可用时,触发器的时钟引脚才会翻转。

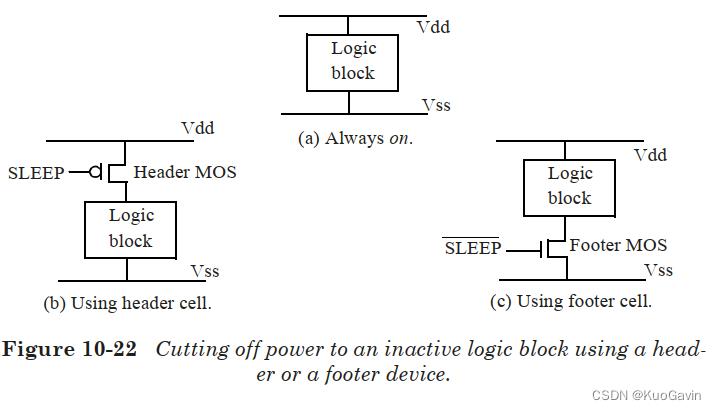

10.6.2 电源门控(Power Gating)

电源门控包括关闭电源,以便可以关闭无效模块的供电。图10-22中说明了此过程,其中在电源中串联添加了 f o o t e r footer footer(或 h e a d e r header header) M O S MOS MOS器件。适当配置控制信号 S L E E P SLEEP SLEEP后,可以使 f o o t e r footer footer(或 h e a d e r header header) M O S MOS MOS器件在模块的正常工作期间处于打开状态。由于在正常工作期间电源门控MOS器件(Header或Footer)处于打开状态,因此该模块已被上电,并在正常功能模式下运行。在模块的无效(或睡眠)模式期间,门控 M O S MOS MOS器件( f o o t e r footer footer或 h e a d e r header header)被关闭,这可以消除逻辑模块中的任何有功功耗。 f o o t e r footer footer是在实际的地与模块的地网络之间的大型 N M O S NMOS NMOS器件,可通过电源门控对其进行控制。 h e a d e r header header是实际的电源和模块的电源网络之间的大型 P M O S PMOS PMOS设备,也可通过电源门控进行控制。在睡眠模式下,模块中唯一消耗的功率是通过 f o o t e r footer footer(或 h e a d e r header header)器件的漏电功率。

通常使用多个电源门控单元来实现 h e a d e r s headers headers或 f o o t e r s footers footers,这些电源门控单元对应于多个并联的 M O S MOS MOS器件。 f o o t e r footer footer和 h e a d e r header header器件为电源引入了一系列导通电阻。如果导通电阻的值不小,则通过门控 M O S MOS MOS器件的 I R IR IR压降会影响逻辑模块中单元的时序。关于门控器件尺寸的考虑主要是为了确保导通电阻值足够小,若再同时考虑电源门控 M O S MOS MOS器件在无效模式或睡眠模式下的漏电功耗,则需要进行权衡。

总之,应该有足够数量的并联电源门控单元,以确保在正常工作模式下电阻串联时的 I R IR IR压降最小。但是,在无效模式或睡眠模式下门控单元的漏电功耗也是选择并联电源门控单元数量的标准。

10.6.3 多阈值单元(Multi Vt Cells)

如3.8 功耗建模(power dissipation modeling)中所述,多阈值( V t Vt Vt)单元可用于权衡速度与漏电。高 V t Vt Vt单元的漏电较少,但是却比标准Vt单元的速度更慢,相反,标准 V t Vt Vt单元虽然速度更快,但是漏电也更多。同样,低 V t Vt Vt单元的速度比标准 V t Vt Vt单元更快,但漏电量也相应地比较高。

在大多数设计中,目标是在达到所需工作速度的同时将总功率降至最低。即使漏电可能是总功率的重要组成部分,但仅采用高 V t Vt Vt单元来减少漏电的设计也可能会增加总功率,尽管漏电确实减少了。这是因为最终的设计实现可能需要更多(或更高强度)的高 V t Vt Vt单元才能实现所需的性能。由于使用高 V t Vt Vt单元,等效门数的增加导致的有功功率增加将会远大于漏电功率的减少。但是在某些情况下,漏电才是总功率的主要组成部分,在这种情况下,使用高 V t Vt Vt单元的设计可以使总功率降低。由于需要取决于具体的设计以及切换活动曲线(switching activity profile),因此需要适当地利用上述具有不同 V t Vt Vt的单元之间在速度和漏电方面的折中。下面将介绍一个高性能模块的两种不同情况,根据模块是处于非常活跃状态还是低切换状态,实现方法可能有所不同。

具有高切换活动的高性能模块:这种情况是具有高切换活动的高性能模块,其功率主要由有功功率决定。对于此类模块,即使可以将漏电影响最小化,但仅专注于降低漏电功率还是会导致总功率的增加。在这种情况下,初始设计实现应使用标准 V t Vt