quartus II 全编译出现严重警告

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了quartus II 全编译出现严重警告相关的知识,希望对你有一定的参考价值。

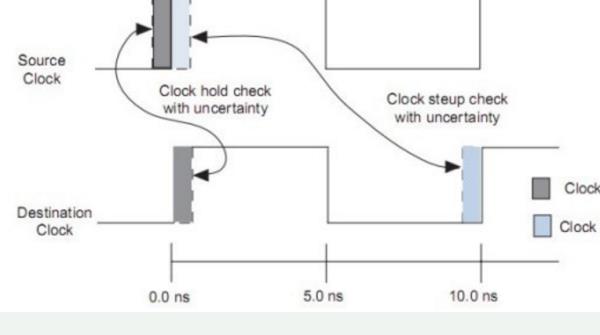

Critical Warning: The following clock transfers have no clock uncertainty assignment. For more accurate results, apply clock uncertainty assignments or use the derive_clock_uncertainty command.

Critical Warning: From Clock (Rise) to Clock (Rise) (setup and hold

quartus II 全编译出现严重警告按以下方式解决:

首先看命令 derive_clock_uncertainty 的帮助,再根据自己的问题在*.sdc文件中加入

set_clock_uncertainty -setup -rise_from Clock -rise_to Clock 0.150

set_clock_uncertainty -hold -rise_from Clock -rise_to Clock 0.150

保存,重新编译。严重警告就消失了。

编译的时候没有注意,整个工程都可以在板子上跑起来。但是做Powerplay的时候,出现了这个Critical Warning:、

Critical

Warning: The following clock transfers have no clock uncertainty

assignment. For more accurate results, apply clock uncertainty

assignments or use the derive_clock_uncertainty command.

Critical Warning: From altera_reserved_tck (Rise) to altera_reserved_tck (Rise) (setup and hold)

Critical Warning: From altera_reserved_tck (Rise) to altera_reserved_tck (Fall) (setup and hold)

Critical Warning: From altera_reserved_tck (Fall) to altera_reserved_tck (Fall) (setup and hold)

参考了很多文献。Altera上说是时序问题,并提供了如下解决方法:

Solution

The

altera_reserved_tck pin is automatically generated for a design that

uses a JTAG accessible module such as the SignalTap? II logic analyzer,

the In-System Memory Content Editor or the Nios? II debugger.

To constrain this JTAG clock, apply a 10-MHz clock constraint to this pin.

For the TimeQuest Timing Analyzer, use the following command:

create_clock -period "100.000 ns" -name altera_reserved_tck altera_reserved_tck

For the Quartus? II Classic Timing Analyzer, use the following command:

set_global_assignment -name FMAX_REQUIREMENT "10 MHz" -section_id altera_reserved_tck

set_instance_assignment -name CLOCK_SETTINGS altera_reserved_tck -to altera_reserved_tck

Any

datapaths crossing into the altera_reserved_tck clock domain from

another domain can be set as false paths. Similarly any datapaths

crossing from the altera_reserved_tck domain to another domain can also

be set as false paths.

好像有些人用了这个方法之后有效果。但是我的没有效果。有另外搜索了好多。实验了很多次,尽管使用的命令各不相同,但是大家一致认为这个事是时序约束没做好的问题,跟使用JTAG有关系。最后找到一片博文:http://blog.sina.com.cn/s/blog_436c7ed30100lu1q.html

我很欣赏博主的“依样画葫芦”的精神,跟我太像了。说实话这个精神救了很多人,害了整个国家。但是这并不影响我再一次“依样画葫芦”:

set_clock_uncertainty -setup -rise_from altera_reserved_tck -rise_to altera_reserved_tck 0.150

set_clock_uncertainty -hold -rise_from altera_reserved_tck -rise_to altera_reserved_tck 0.150

set_clock_uncertainty -setup -rise_from altera_reserved_tck -fall_to altera_reserved_tck 0.150

set_clock_uncertainty -hold -rise_from altera_reserved_tck -fall_to altera_reserved_tck 0.150

set_clock_uncertainty -setup -fall_from altera_reserved_tck -fall_to altera_reserved_tck 0.150

set_clock_uncertainty -hold -fall_from altera_reserved_tck -fall_to altera_reserved_tck 0.150

这几句话添加上去,就没有Warning了。希望看到这篇文章的牛人,留言批评一下,告诉我应该在哪里弄清楚这些东西呢?

【转别人的,你参考下】本回答被提问者采纳

Quartus II 中 Verilog 常见警告/错误汇总

Verilog 常见错误汇总

1.Found clock-sensitive change during active clock edge at time <time> on register "<name>"

原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化.而时钟敏感信号是不能在时钟边沿变化的.其后果为导致结果不正确.

措施:编辑vector source file

2.Verilog HDL assignment warning at <location>: truncated with size <number> to match size of target (<number>

原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位, 将位数裁定到合适的大小

措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数

3.All reachable assignments to data_out(10) assign ‘0‘, register removed by optimization

原因:经过综合器优化后,输出端口已经不起作用了

4.Following 9 pins have nothing, GND, or VCC driving datain port -- changes to this connectivity may change fitting results

原因:有9个脚为空或接地或接上了电源

措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源. 如果你的设计中这些端口就是这样用的,那便可以不理会这些warning

5.Found pins functioning as undefined clocks and/or memory enables

原因:是你作为时钟的PIN没有约束信息.可以对相应的PIN做一下设定就行了. 主要是指你的某些管脚在电路当中起到了时钟管脚的作用,比如flip-flop的clk 管脚,而此管脚没有时钟约束,因此QuartusII把“clk”作为未定义的时钟.

措施:如果clk不是时钟,可以加“not clock”的约束;如果是,可以在clock setting当中加入;在某些对时钟要求不很高的情况下,可以忽略此警告或在这里修改:Assignments>Timing analysis settings...>Individual

clocks...>...

6.Timing characteristics of device EPM570T144C5 are preliminary

原因:因为MAXII 是比較新的元件在 QuartusII 中的時序并不是正式版的,要等 Service Pack

措施:只影响 Quartus 的 Waveform

7.Warning: Clock latency analysis for PLL offsets is supported for the current device family, but is not enabled

措施:将setting中的timing Requirements&Option-->More Timing Setting-->setting-->Enable Clock Latency中的on改成OFF

8.Found clock high time violation at 14.8 ns on register "|counter|lpm_counter:count1_rtl_0|dffs[11]"

原因:违反了steup/hold时间,应该是后仿真,看看波形设置是否和时钟沿符合steup/hold时间

措施:在中间加个寄存器可能可以解决问题

9.warning: circuit may not operate.detected 46 non-operational paths clocked by clock clk44 with clock skew larger than data delay

原因:时钟抖动大于数据延时,当时钟很快,而if等类的层次过多就会出现这种问 题,但这个问题多是在器件的最高频率中才会出现

措施:setting-->timing Requirements&Options-->Default required fmax 改小一些,如改到50MHZ

10.Design contains <number> input pin(s) that do not drive logic

原因:输入引脚没有驱动逻辑(驱动其他引脚),所有的输入引脚需要有输入逻辑

措施:如果这种情况是故意的,无须理会,如果非故意,输入逻辑驱动.

11.Warning:Found clock high time violation at 8.9ns on node ‘TEST3.CLK‘

原因:FF中输入的PLS的保持时间过短

措施:在FF中设置较高的时钟频率

12.Warning: Found 10 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skew

原因:如果你用的 CPLD 只有一组全局时钟时,用全局时钟分频产生的另一个时 钟在布线中当作信号处理,不能保证低的时钟歪斜(SKEW).会造成在这个时钟 上工作的时序电路不可靠,甚至每次布线产生的问题都不一样.

措施:如果用有两组以上全局时钟的 FPGA 芯片,可以把第二个全局时钟作为另 一个时钟用,可以解决这个问题.

13.Critical Warning: Timing requirements were not met. See Report window for details.

原因:时序要求未满足,

措施:双击Compilation Report-->Time Analyzer-->红色部分(如clock setup:‘clk‘等)-->左键单击list path,查看fmax的SLACK REPORT再根据 提示解决,有可能是程序的算法问题

14.Can‘t achieve minimum setup and hold requirement <text> along <number> path(s). See Report window for details.

原因:时序分析发现一定数量的路径违背了最小的建立和保持时间,与时钟歪斜 有关,一般是由于多时钟引起的

措施:利用Compilation Report-->Time Analyzer-->红色部分(如clock hold:‘clk‘等),在slack中观察是hold time为负值还是setup time 为负值, 然后在:Assignment-->Assignment Editor-->To中增加时钟名(from

node finder),Assignment Name中增加 和多时钟有关的Multicycle 和Multicycle Hold选项,如hold time为负,可 使Multicycle hold的值>multicycle,如设为2和1.

15: Can‘t analyze file -- file E://quartusii/*/*.v is missing

原因:试图编译一个不存在的文件,该文件可能被改名或者删除了

措施:不管他,没什么影响

16.Warning: Can‘t find signal in vector source file for input pin |whole|clk10m

原因:因为你的波形仿真文件( vector source file )中并没有把所有的输入 信号(input pin)加进去,对于每一个输入都需要有激励源的

17.Error: Can‘t name logic scfifo0 of instance "inst" -- has same name as current design file

原因:模块的名字和project的名字重名了

措施:把两个名字之一改一下,一般改模块的名字

18.Warning: Using design file lpm_fifo0.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project Info: Found entity 1: lpm_fifo0

原因:模块不是在本项目生成的,而是直接copy了别的项目的原理图和源程序 而生成的,而不是用QUARTUS将文件添加进本项目

措施:无须理会,不影响使用

19.Timing characteristics of device <name> are preliminary

原因:目前版本的QuartusII只对该器件提供初步的时序特征分析

措施:如果坚持用目前的器件,无须理会该警告.关于进一步的时序特征分析会在后续版本的Quartus得到完善.

20.Timing Analysis does not support the analysis of latches as synchronous elements for the currently selected device family

原因:用analyze_latches_as_synchronous_elements setting可以让 Quaruts II来分析同步锁存,但目前的器件不支持这个特性

措施:无须理会.时序分析可能将锁存器分析成回路.但并不一定分析正确.其 后果可能会导致显示提醒用户:改变设计来消除锁 存器

21.Warning:Found xx output pins without output pin load capacitance assignment

原因:没有给输出管教指定负载电容

措施:该功能用于估算TCO和功耗,可以不理会,也可以在Assignment Editor 中为相应的输出管脚指定负载电容,以消除警告

22.Warning: Found 6 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skew

原因:使用了行波时钟或门控时钟,把触发器的输出当时钟用就会报行波时钟, 将组合逻辑的输出当时钟用就会报门控时钟

措施:不要把触发器的输出当时钟,不要将组合逻辑的输出当时钟,如果本身如 此设计,则无须理会该警告

23.Warning (10268): Verilog HDL information at lcd7106.v(63): Always Construct contains both blocking and non-blocking assignments

原因: 一个always模块中同时有阻塞和非阻塞的赋值

24.Warning: Can‘t find signal in vector source file for input pin |whole|clk10m

原因:这个时因为你的波形仿真文件( vector source file )中并没有把所有的输入信号(input pin)加进去, 对于每一个输入都需要有激励源的

25 Warning:Output pins are stuck at VCC or GND

如果正是希望某些输出被固定置高电平或低电平或者无所谓,就不用管它,否则请检查代码。这样的输出其实没有什么意义.

26.Warning (10208): honored full_case synthesis attribute - differences between design synthesis and simulation may occur。

/* synopsys full_case */;

意思就是:,告诉合成软件你的case几乎是full case,你(designer)可以保证没有列出的case分支是永远也不会发生的。 {

目的:告诉合成软体不用去考虑没有列出的case分支,便于化简。

限制:当然只有synopsys 的合成软体可以看懂了!所以不建议用,最好还是用default。

缺点:前后仿真不一致,综合的结果和期望的不一致。

27:Warning: No exact pin location assignment(s) for 16 pins of 16 total pins

定义的管脚没有和外部的管脚连接.

28:Warning: Ignored locations or region assignments to the following nodes

Warning: Node "78ledcom[4]" is assigned to location or region, but does not exist in design

设计中没提到"78ledcom[4]" ,而分配了管脚给它。

说明:有时候运行了TCL脚本文件后需要修改,修改后有一些先前分配的管脚不需要了,如果没有delete,则会出现此提示。

解决办法:assignments->pins,把不用的管脚删除即可(TCL脚本文件里的多余管脚分配语句最好也一起delete)。

1 Warning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not in sensitivity list

----没把singal放到process()中

2 Warning: Found pins ing as undefined clocks and/or memory enables

Info: Assuming node CLK is an undefined clock

-=-----可能是说设计中产生的触发器没有使能端

3 Error: VHDL Interface Declaration error in clk_gen.vhd(29): interface object "clk_scan" of mode out cannot be read. Change object mode to buffer or inout.

------信号类型设置不对,out当作buffer来定义

4 Error: Node instance "clk_gen1" instantiates undefined entity "clk_gen"

-------引用的例化元件未定义实体--entity "clk_gen"

5 Warning: Found 2 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skew

Info: Detected ripple clock "clk_gen:clk_gen1|clk_incr" as buffer

Info: Detected ripple clock "clk_gen:clk_gen1|clk_scan" as buffer

6 Warning: VHDL Process Statement warning at ledmux.vhd(15): signal or variable "dataout" may not be assigned a new in every possible path through the Process Statement. Signal or variable "dataout" holds its previous in every path with no new assignment, which may create a combinational loop in the current design.

7 Warning: VHDL Process Statement warning at divider_10.vhd(17): signal "cnt" is read inside the Process Statement but isn‘t in the Process Statement‘s sensivitity list

-----缺少敏感信号

8 Warning: No clock transition on "counter_bcd7:counter_counter_clk|q_sig[3]" register

9 Warning: Reduced register "counter_bcd7:counter_counter_clk|q_sig[3]" with stuck clock port to stuck GND

10 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "class[1]" with clock skew larger than data delay. See Compilation Report for details.

11 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "sign" with clock skew larger than data delay. See Compilation Report for details.

12 Error: VHDL error at counter_clk.vhd(90): actual port "class" of mode "in" cannot be associated with formal port "class" of mode "out"

------两者不能连接起来

13 Warning: Ignored node in vector source file. Can‘t find corresponding node name "class_sig[2]" in design.

------没有编写testbench文件,或者没有编辑输入变量的值 testbench里是元件申明和映射

14 Error: VHDL Binding Indication error at freqdetect_top.vhd(19): port "class" in design entity does not have std_logic_vector type that is specified for the same generic in the associated component

---在相关的元件里没有当前文件所定义的类型

15 Error: VHDL error at tongbu.vhd(16): can‘t infer register for signal "gate" because signal does not hold its outside clock edge

16 Warning: Found clock high time violation at 1000.0 ns on register "|fcounter|lpm_counter:temp_rtl_0|dffs[4]"

17 Warning: Compiler packed, optimized or synthesized away node "temp[19]". Ignored vector source file node.

---"temp[19]"被优化掉了

18 Warning: Reduced register "gate~reg0" with stuck data_in port to stuck GND

19 Warning: Design contains 2 input pin(s) that do not drive logic

Warning: No output dependent on input pin "clk"

Warning: No output dependent on input pin "sign"

------输出信号与输入信号无关,

20 Warning: Found clock high time violation at 16625.0 ns on register "|impulcomp|gate1"

21 Error: VHDL error at impulcomp.vhd(19): can‘t implement clock enable condition specified using binary operator "or"

22 Error: VHDL Association List error at period_counter.vhd(38): actual parameter assigned to formal parameter "alarm", but formal parameter is not declared

-------连接表错误,形参"alarm"赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

23 Error: Ignored construct behavier at period_counter.vhd(15) because of previous errors

--------因为前一个错误而导致的错误

24 Error: VHDL error at period_counter.vhd(38): type of identifier "alarm" does not agree with its usage as std_logic type

--------"alarm"的定义类型与使用的类型不一致

25 Error: VHDL error at shift_reg.vhd(24): can‘t synthesize logic for statement with conditions that test for the edges of multiple clocks

-------同一进程中含有两个或多个if(edge)条件,(一个进程中之能有一个时钟沿)

26 Error: Can‘t resolve multiple constant drivers for net "datain_reg[22]" at shift_reg.vhd(19)

27 can‘t infer register for signal "num[0]" because signal does not hold its outside clock edge

28 Error: Can‘t elaborate top-level user hierarchy

29 Error: Can‘t resolve multiple constant drivers for net "cs_in" at led_key.vhd(32) ----------有两个以上赋值语句,不能确定“cs_in”的值

30 Warning: Ignored node in vector source file. Can‘t find corresponding node name "over" in design.

---------------在源文件中找不到对应的节点“over”。

31 Error: Can‘t access JTAG chain

无法找到下载链

1.Found clock-sensitive change during active clock edge at time <time> on register "<name>"

原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。而时钟敏感信号是 不能在时钟边沿变化的。其后果为导致结果不正确。

措施:编辑vector source file

2.Verilog HDL assignment warning at <location>: truncated value with size <number> to match size of target (<number>

原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位,将位数裁定到合适的大小 措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数

3.All reachable assignments to data_out(10) assign ‘0‘, register removed by optimization 原因:经过综合器优化后,输出端口已经不起作用了

4.Following 9 pins have nothing, GND, or VCC driving datain port -- changes to this connectivity may change fitting results

原因:第9脚,空或接地或接上了电源 措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。如果你的设计中这些端口就是这样用的,那便可以不理会这些warning

5.Found pins functioning as undefined clocks and/or memory enables

原因:是你作为时钟的PIN没有约束信息。可以对相应的PIN做一下设定就行了。主要是指你的某些管脚在电路当中起到了时钟管脚的 作用,比如flip-flop的clk管脚,而此管脚没有时钟约束,因此QuartusII把“clk”作为未定义的时钟。

措施:如果clk不是时钟,可以加“not clock”的约束;如果是,可以在clock setting当中加入;在某些对时钟要求不很高的情况下,可以忽略此警告或在这里修改:Assignments>Timing analysis settings...>Individual clocks...>... 注意在Applies to node中只用选择时钟引脚一项即可,required fmax一般比所要求频率高5%即可,无须太紧或太松。

6.Timing characteristics of device EPM570T144C5 are preliminary

原因:因为MAXII 是比較新的元件在 QuartusII 中的時序並不是正式版的,要等 Service Pack 措施:只影响 Quartus 的 Waveform

7.Warning: Clock latency analysis for PLL offsets is supported for the current device family, but is not enabled

措施:将setting中的timing Requirements&Option-->More Timing Setting-->setting-->Enable Clock Latency中的on改成OFF

8.Found clock high time violation at 14.8 ns on register "|counter|lpm_counter:count1_rtl_0|dffs[11]"

原因:违反了steup/hold时间,应该是后仿真,看看波形设置是否和时钟沿符合steup/hold时间

措施:在中间加个寄存器可能可以解决问题

9.warning: circuit may not operate.detected 46 non-operational paths clocked by clock clk44 with clock skew larger than data delay

原因:时钟抖动大于数据延时,当时钟很快,而if等类的层次过多就会出现这种问题,但这个问题多是在器件的最高频率中才会出现

措施:setting-->timing Requirements&Options-->Default required fmax 改小一些,如改到50MHZ

10.Design contains <number> input pin(s) that do not drive logic

原因:输入引脚没有驱动逻辑(驱动其他引脚),所有的输入引脚需要有输入逻辑

措施:如果这种情况是故意的,无须理会,如果非故意,输入逻辑驱动.

11.Warning:Found clock high time violation at 8.9ns on node ‘TEST3.CLK‘

原因:FF中输入的PLS的保持时间过短

措施:在FF中设置较高的时钟频率

12.Warning: Found 10 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skew

原因:如果你用的 CPLD 只有一组全局时钟时,用全局时钟分频产生的另一个时钟在布线中当作信号处理,不能保证低的时钟歪斜(SKEW)。会造成在这个时钟上工作的时序电路不可靠,甚至每次布线产生的问题都不一样。

措施:如果用有两组以上全局时钟的 FPGA 芯片,可以把第二个全局时钟作为另一个时钟用,可以解决这个问题。

13.Critical Warning: Timing requirements were not met. See Report window for details.

原因:时序要求未满足,

措施:双击Compilation Report-->Time Analyzer-->红色部分(如clock setup:‘clk‘等)-->左键单击list path,查看fmax的SLACK REPORT再根据提示解决,有可能是程序的算法问题或fmax设置问题

14.Warning: Can‘t find signal in vector source file for input pin |whole|clk10m

原因:这个时因为你的波形仿真文件( vector source file )中并没有把所有的输入信号(input pin)加进去,对于每一个输入都需要有激励源的

15.Can‘t achieve minimum setup and hold requirement <text> along <number> path(s). See Report window for details.

原因:时序分析发现一定数量的路径违背了最小的建立和保持时间,与时钟歪斜有关,一般是由于多时钟引起的

措施:利用Compilation Report-->Time Analyzer-->红色部分(如clock hold:‘clk‘等),在slack中观察是hold time为负值还是setup time 为负值,然后在:Assignment-->Assignment Editor-->To中增加时钟名(from node finder),Assignment Name中增加和多时钟有关的Multicycle 和Multicycle Hold选项,如hold time为负,可使Multicycle hold的值>multicycle,如设为2和1。

16: Can‘t analyze file -- file E://quartusii/*/*.v is missing

原因:试图编译一个不存在的文件,该文件可能被改名或者删除了

措施:不管他,没什么影响

17.Warning: Can‘t find signal in vector source file for input pin |whole|clk10m

原因:因为你的波形仿真文件( vector source file )中并没有把所有的输入信号(input pin)加进去,对于每一个输入都需要有激励源的

18.Error: Can‘t name logic function scfifo0 of instance "inst" -- function has same name as current design file

原因:模块的名字和project的名字重名了

措施:把两个名字之一改一下,一般改模块的名字

19.Warning: Using design file lpm_fifo0.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project Info: Found entity 1: lpm_fifo0

原因:模块不是在本项目生成的,而是直接copy了别的项目的原理图和源程序而生成的,而不是用QUARTUS将文件添加进本项目

措施:无须理会,不影响使用

20.Timing characteristics of device <name> are preliminary

原因:目前版本的QuartusII只对该器件提供初步的时序特征分析

措施:如果坚持用目前的器件,无须理会该警告。关于进一步的时序特征分析会在后续版本的Quartus得到完善。

21.Timing Analysis does not support the analysis of latches as synchronous elements for the currently selected device family

原因:用analyze_latches_as_synchronous_elements setting可以让Quaruts II来分析同步锁存,但目前的器件不支持这个特性

措施:无须理会。时序分析可能将锁存器分析成回路。但并不一定分析正确。其后果可能会导致显示提醒用户:改变设计来消除锁存器,但实际其实无关紧要

22.Warning:Found xx output pins without output pin load capacitance assignment

原因:没有给输出管教指定负载电容

解决方法:该功能用于估算TCO和功耗,可以不理会,也可以在Assignment Editor中为相应的输出管脚指定负载电容,以消除警告

Quartus常见错误分析 Error

1 Warning: VHDL Process Statement warning at random.vhd(18): signal reset is in statement, but is not in sensitivity list

----没把singal放到process()中

2 Warning: Found pins ing as undefined clocks and/or memory enables

Info: Assuming node CLK is an undefined clock

-=-----可能是说设计中产生的触发器没有使能端

3 Error: VHDL Interface Declaration error in clk_gen.vhd(29): interface object "clk_scan" of mode out cannot be read. Change object mode to buffer or inout.

------信号类型设置不对,out当作buffer来定义

4 Error: Node instance "clk_gen1" instantiates undefined entity "clk_gen"

-------引用的例化元件未定义实体--entity "clk_gen"

5 Warning: Found 2 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skew

Info: Detected ripple clock "clk_gen:clk_gen1|clk_incr" as buffer

Info: Detected ripple clock "clk_gen:clk_gen1|clk_scan" as buffer

6 Warning: VHDL Process Statement warning at ledmux.vhd(15): signal or variable "dataout" may not be assigned a new in every possible path through the Process Statement. Signal or variable "dataout" holds its previous in every path with no new assignment, which may create a combinational loop in the current design.

7 Warning: VHDL Process Statement warning at divider_10.vhd(17): signal "cnt" is read inside the Process Statement but isn‘t in the Process Statement‘s sensivitity list

-----缺少敏感信号

8 Warning: No clock transition on "counter_bcd7:counter_counter_clk|q_sig[3]" register

9 Warning: Reduced register "counter_bcd7:counter_counter_clk|q_sig[3]" with stuck clock port to stuck GND

10 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "class[1]" with clock skew larger than data delay. See Compilation Report for details.

11 Warning: Circuit may not operate. Detected 1 non-operational path(s) clocked by clock "sign" with clock skew larger than data delay. See Compilation Report for details.

12 Error: VHDL error at counter_clk.vhd(90): actual port "class" of mode "in" cannot be associated with formal port "class" of mode "out"

------两者不能连接起来

13 Warning: Ignored node in vector source file. Can‘t find corresponding node name "class_sig[2]" in design.

------没有编写testbench文件,或者没有编辑输入变量的值 testbench里是元件申明和映射

14 Error: VHDL Binding Indication error at freqdetect_top.vhd(19): port "class" in design entity does not have std_logic_vector type that is specified for the same generic in the associated component

---在相关的元件里没有当前文件所定义的类型

15 Error: VHDL error at tongbu.vhd(16): can‘t infer register for signal "gate" because signal does not hold its outside clock edge

16 Warning: Found clock high time violation at 1000.0 ns on register

"|fcounter|lpm_counter:temp_rtl_0|dffs[4]"

17 Warning: Compiler packed, optimized or synthesized away node "temp[19]". Ignored vector source file node.

---"temp[19]"被优化掉了

18 Warning: Reduced register "gate~reg0" with stuck data_in port to stuck GND

19 Warning: Design contains 2 input pin(s) that do not drive logic

Warning: No output dependent on input pin "clk"

Warning: No output dependent on input pin "sign"

------输出信号与输入信号无关,

20 Warning: Found clock high time violation at 16625.0 ns on register "|impulcomp|gate1"

21 Error: VHDL error at impulcomp.vhd(19): can‘t implement clock enable condition specified using binary operator "or"

22 Error: VHDL Association List error at period_counter.vhd(38): actual parameter assigned to formal parameter "alarm", but formal parameter is not declared

-------连接表错误,形参"alarm"赋值给实参,形参没定义,可能是形参与实参的位置颠倒了,规定形参在实参之前。

23 Error: Ignored construct behavier at period_counter.vhd(15) because of previous errors

--------因为前一个错误而导致的错误

24 Error: VHDL error at period_counter.vhd(38): type of identifier "alarm" does not agree with its usage as std_logic type

--------"alarm"的定义类型与使用的类型不一致

25 Error: VHDL error at shift_reg.vhd(24): can‘t synthesize logic for statement with conditions that test for the edges of multiple clocks

-------同一进程中含有两个或多个if(edge)条件,(一个进程中之能有一个时钟沿)

26 Error: Can‘t resolve multiple constant drivers for net "datain_reg[22]" at shift_reg.vhd(19)

27 can‘t infer register for signal "num[0]" because signal does not hold its outside clock edge

28Error: Can‘t elaborate top-level user hierarchy

29 Error: Can‘t resolve multiple constant drivers for net "cs_in" at led_key.vhd(32) ----------有两

个以上赋值语句,不能确定“cs_in”的值,

30 Warning: Ignored node in vector source file. Can‘t find corresponding node name "over" in design.

---------------在源文件中找不到对应的节点“over”。

31 Error: Can‘t access JTAG chain

无法找到下载链

32 Info: Assuming node "clk" is an undefined clock

Quartus警告分析 Warning

1.Found clock-sensitive change during active clock edge at time <time> on register "<name>"

原因:vector source file中时钟敏感信号(如:数据,允许端,清零,同步加载等)在时钟的边缘同时变化。而时钟敏感信号是不能在时钟边沿变化的。其后果为导致结果不正确。

措施:编辑vector source file

2.Verilog HDL assignment warning at <location>: truncated with size <number> to match size of target (<number>

原因:在HDL设计中对目标的位数进行了设定,如:reg[4:0] a;而默认为32位, 将位数裁定到合适的大小

措施:如果结果正确,无须加以修正,如果不想看到这个警告,可以改变设定的位数

3.All reachable assignments to data_out(10) assign ‘0‘, register removed by optimization

原因:经过综合器优化后,输出端口已经不起作用了

4.Following 9 pins have nothing, GND, or VCC driving datain port -- changes to this connectivity may change fitting results

原因:第9脚,空或接地或接上了电源

措施:有时候定义了输出端口,但输出端直接赋‘0’,便会被接地,赋‘1’接电源。

如果你的设计中这些端口就是这样用的,那便可以不理会这些warning

5.Found pins ing as undefined clocks and/or memory enables

原因:是你作为时钟的PIN没有约束信息。可以对相应的PIN做一下设定就行了。

主要是指你的某些管脚在电路当中起到了时钟管脚的作用,比如flip-flop的clk管脚,而此管脚没有时钟约束,因此QuartusII把“clk”作为未定义的时钟。

措施:如果clk不是时钟,可以加“not clock”的约束;如果是,可以在clock setting当中加入;在某些对时钟要求不很高的情况下,可以忽略此警告或在这里修改:Assignments>Timing analysis settings...>Individual clocks...>...

6.Timing characteristics of device EPM570T144C5 are preliminary

原因:因为MAXII 是比較新的元件在 QuartusII 中的時序并不是正式版的,要等 Service Pack

措施:只影响 Quartus 的 Waveform

7.Warning: Clock latency analysis for PLL offsets is supported for the current device family, but is not enabled

措施:将setting中的timing Requirements&Option-->More Timing Setting-->setting-->Enable Clock Latency中的on改成OFF

8.Found clock high time violation at 14.8 ns on register "|counter|lpm_counter:count1_rtl_0|dffs[11]"

原因:违反了steup/hold时间,应该是后仿真,看看波形设置是否和时钟沿符合steup/hold时间

措施:在中间加个寄存器可能可以解决问题

9.warning: circuit may not operate.detected 46 non-operational paths clocked by clock clk44 with clock skew larger than data delay

原因:时钟抖动大于数据延时,当时钟很快,而if等类的层次过多就会出现这种问题,但这个问题多是在器件的最高频率中才会出现

措施:setting-->timing Requirements&Options-->Default required fmax 改小一些,如改到50MHZ

10.Design contains <number> input pin(s) that do not drive logic

原因:输入引脚没有驱动逻辑(驱动其他引脚),所有的输入引脚需要有输入逻辑

措施:如果这种情况是故意的,无须理会,如果非故意,输入逻辑驱动

11.Warning:Found clock high time violation at 8.9ns on node ‘TEST3.CLK‘

原因:FF中输入的PLS的保持时间过短

措施:在FF中设置较高的时钟频率

12.Warning: Found 10 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skew

原因:如果你用的 CPLD 只有一组全局时钟时,用全局时钟分频产生的另一个时钟在布线中当作信号处理,不能保证低的时钟歪斜(SKEW)。会造成在这个时钟上工作的时序电路不可靠,甚至每次布线产生的问题都不一样。

措施:如果用有两组以上全局时钟的 FPGA 芯片,可以把第二个全局时钟作为另一个时钟用,可以解决这个问题。

13.Critical Warning: Timing requirements were not met. See Report window for details.

原因:时序要求未满足

措施:双击Compilation Report-->Time Analyzer-->红色部分(如clock setup:‘clk‘等)-->左键单击list path,查看fmax的SLACK REPORT再根据提示解决,有可能是程序的算法问题

14.Can‘t achieve minimum setup and hold requirement <text> along <number> path(s). See Report window for details.

原因:时序分析发现一定数量的路径违背了最小的建立和保持时间,与时钟歪斜有关,一般是由于多时钟引起的

措施:利用Compilation Report-->Time Analyzer-->红色部分(如clockhold:‘clk‘等),在slack中观察是hold time为负值还是setup time 为负值,然后在:Assignment-->Assignment Editor-->To中增加时钟名(from node finder),Assignment Name中增加和多时钟有关的Multicycle 和Multicycle Hold选项,如hold time为负,可使Multicycle hold的值>multicycle,如设为2和1。

15: Can‘t analyze file -- file E://quartusii/*/*.v is missing

原因:试图编译一个不存在的文件,该文件可能被改名或者删除了

措施:不管他,没什么影响

16.Warning: Can‘t find signal in vector source file for input pin |whole|clk10m

原因:因为你的波形仿真文件( vector source file )中并没有把所有的输入信号(input pin)加进去,对于每一个输入都需要有激励源的

17.Error: Can‘t name logic scfifo0 of instance "inst" -- has same name as current design file

原因:模块的名字和project的名字重名了

措施:把两个名字之一改一下,一般改模块的名字

18.Warning: Using design file lpm_fifo0.v, which is not specified as a design file for the current project, but contains definitions for 1 design units and 1 entities in project Info: Found entity 1: lpm_fifo0

原因:模块不是在本项目生成的,而是直接copy了别的项目的原理图和源程序而生成的,而不是用QUARTUS将文件添加进本项目

措施:无须理会,不影响使用

19.Timing characteristics of device <name> are preliminary

原因:目前版本的QuartusII只对该器件提供初步的时序特征分析

措施:如果坚持用目前的器件,无须理会该警告。关于进一步的时序特征分析会在后续版本的Quartus得到完善。

20.Timing Analysis does not support the analysis of latches as synchronous elements for the currently selected device family

原因:用analyze_latches_as_synchronous_elements setting可以让Quaruts II来分析同步锁存,但目前的器件不支持这个特性

措施:无须理会。时序分析可能将锁存器分析成回路。但并不一定分析正确。其后果可能会导致显示提醒用户:改变设计来消除锁 存器

21.Warning:Found xx output pins without output pin load capacitanceassignment(网友:gucheng82提供)

原因:没有给输出管教指定负载电容

措施:该功能用于估算TCO和功耗,可以不理会,也可以在Assignment Editor中为相应的输出管脚指定负载电容,以消除警告

22.Warning: Found 6 node(s) in clock paths which may be acting asripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting inclock skew

原因:使用了行波时钟或门控时钟,把触发器的输出当时钟用就会报行波时钟,将组合逻辑的输出当时钟用就会报门控时钟

措施:不要把触发器的输出当时钟,不要将组合逻辑的输出当时钟,如果本身如此设计,则无须理会该警告

23.Warning (10268): Verilog HDL information at lcd7106.v(63):Always Construct contains both blocking and non-blocking assignments

原因: 一个always模块中同时有阻塞和非阻塞的赋值

以上是关于quartus II 全编译出现严重警告的主要内容,如果未能解决你的问题,请参考以下文章

quartus II编译报错:Error: Current license file does not support the XXX device 环境win10,Quartus2出现破解问题

quartus II编译报错:Error: Current license file does not support the XXX device 环境win10,Quartus2出现破解问题

Quartus prime 16.0 signaltap II 使用

Quartus系列:Quartus II 调用ModelSim仿真调试