xilinx /FPGA/ verilog HDL不同位数的数相加,如何进行?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了xilinx /FPGA/ verilog HDL不同位数的数相加,如何进行?相关的知识,希望对你有一定的参考价值。

比如reg signed [11:0] a,b; reg signed [14:0] c;求 c= a+3*b?这个咋弄?试过直接加结果是错的;之后,我进行了符号扩展,结果不对啊。把a的最高位扩展了3次变成15位的数据,3b的符号位也得扩吧?之后,再进行c=a+3*b;结构还是不对....

一个有符号数[11:0]m,存到一个[14:0]n,寄存器,这个是一定要进行位扩展吧?

如果我把m直接定义成[14:0]位宽的,这个可以不?

个人觉得加法还是在赋值的时候使用$signed去做强制有符号数加法。所以你的程序可以这样:

wire [11:0] a,b;

wire [14:0] c;

wire [12:0] temp;

assign temp = b,1'b0;

assign c = $signed(a) + $signed(b) + $signed(temp);

试一下吧,顺便告诉我结果哈 参考技术A 你的写法太混乱了,乘法器最少也得1个时钟周期才能得到结果。补码运算的话要注意位扩展,是扩展符号位的意思,不是在高位补零。追问

扩展符号位就是把最高位放在前面,比如扩展 [11:0] a,为[14:0],可以这么写a[11],a[11],a[11],a[11],a[11:0]

参考技术B 你把两个logic类型转换成为integer类型 用强制转换就可以转换成integer,算出来你还可以转换回去,具体的用法查语法书! 参考技术C 用simulink仿真一下,要什么原件自己往里拖,自己去试试就清楚啦Xilinx FPGA开发环境vivado使用流程

Xilinx FPGA开发环境vivado使用流程

1.启动vivado 2016.1

2.选择Create New Project

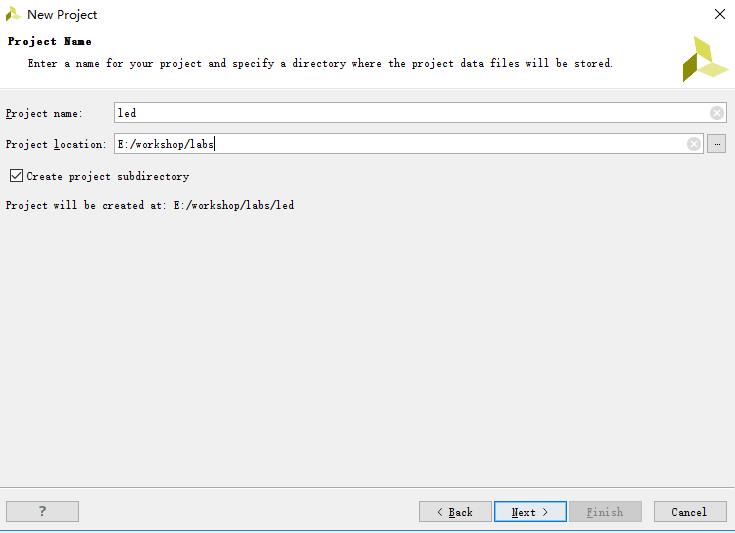

3.指定工程名字和工程存放目录

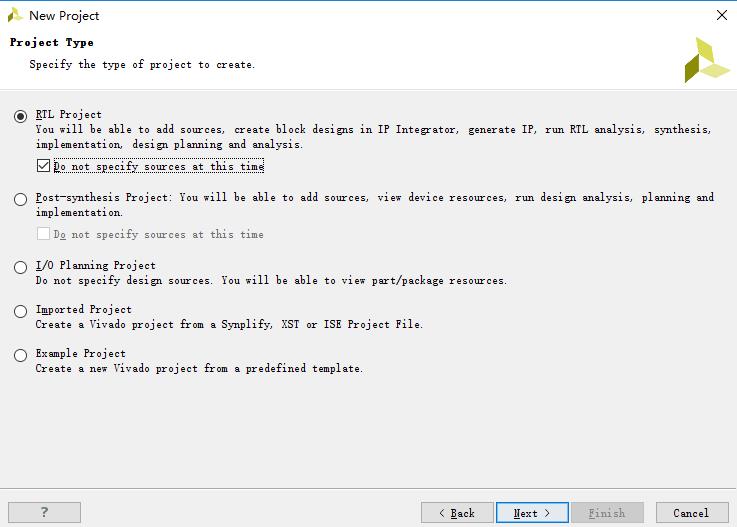

4.选择RTL Project

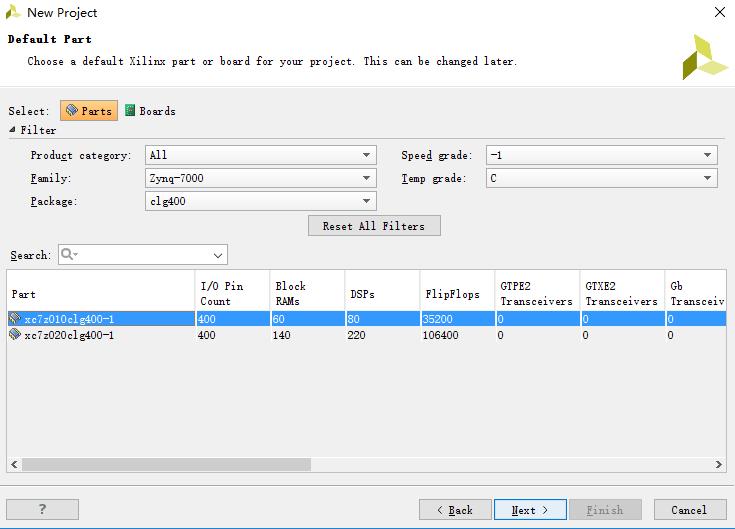

5.选择FPGA设备

6.工程创建完成后

7.开始编写verilog代码

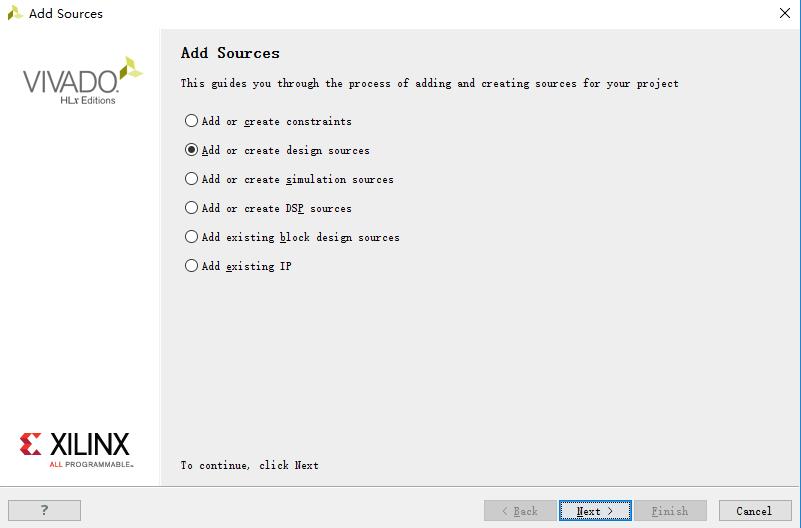

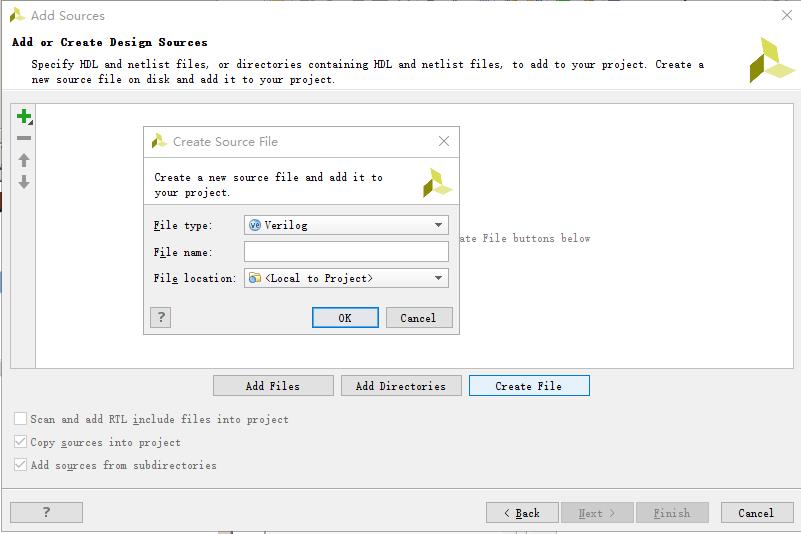

第一步:点击Add Sources按钮

第二步:选择add or create design sources按钮,即添加设计文件

第三步:选择create file

文件新建完成后:

此时可以定义I/O端口,我们选择自己在程序中编写。

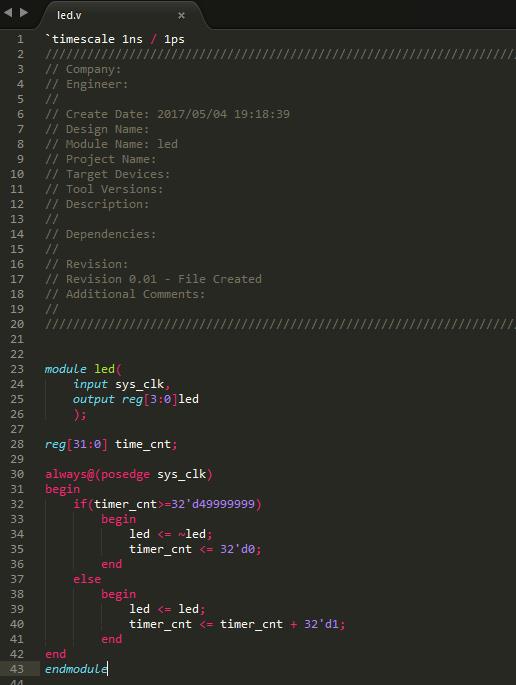

第三步:在编辑器中编写verilog程序

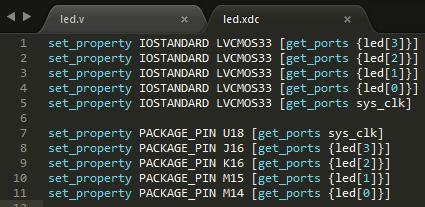

8.添加XDC管脚约束文件

XDC文件里主要是完成管脚的约束,时钟的约束,以及组的约束

第一步:新建约束文件

第二步:创造约束文件

第三步:编辑管脚约束文件

其中,set_property PACKAGE_PIN “引脚编号” [get_ports “端口名称”]

Set_property IOSTANDARD “电压” [get_ports “端口名称”]

9.编译

第一步:运行Run Synthesis 综合

第二步:运行Run Implementation 布局布线

第三步:运行Generate Bitstream 生成bit文件

10.下载和调试

运行Hardware Manager。

以上是关于xilinx /FPGA/ verilog HDL不同位数的数相加,如何进行?的主要内容,如果未能解决你的问题,请参考以下文章