关于FPGA如何快速生成模块的例化模板(实用)

Posted 吾尹先森

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了关于FPGA如何快速生成模块的例化模板(实用)相关的知识,希望对你有一定的参考价值。

关于FPGA如何快速生成模块的例化模板(实用)

语言 :Verilg HDL 、VHDL

EDA工具:ISE、Vivado、Quartus II

一、引言

在FPGA开发中,最常用的设计方式是自顶层向下的模块化设计,将设计要求分成一个个的子模块,负责实现不通的功能,顶层负责调用这些子模块,并负责子模块之间的连接以及与外部接口的连接。

因此,顶层常常要对好多个子模块进行例化,所谓的例化,对标到软件上来说,就是调用,模块也自然对应的就是一个个函数了。此时,如果子模块的输入输出接口比较多的时候,手动去巧例化的模板就是一件非常枯燥乏味浪费时间的事情,本文,在结合平时做项目中的经验,对快速生成模块的例化模板作了一个总结,望能对各位实操应用中有所帮助。

二、快速生成例化模块的几种方法

1. IP核的例化模块

工程中,IP核的使用是比较频繁的,而ip核的例化模板在生成IP的时候,就附带生成了,只需要找到位置复制即可。

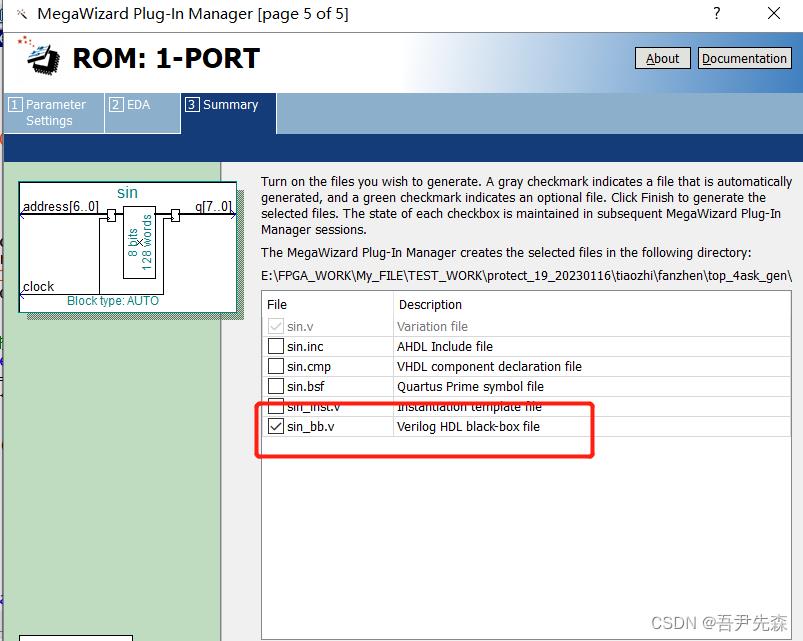

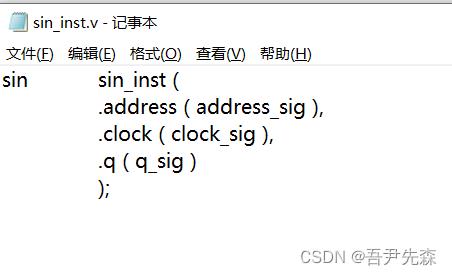

(1)quartus 软件的ip核的例化模板

quarus软件需要在生成IP时,选中xxx_inst.v,生成的模板即在所在工程目录下的xxx_inst.v文件中

如下

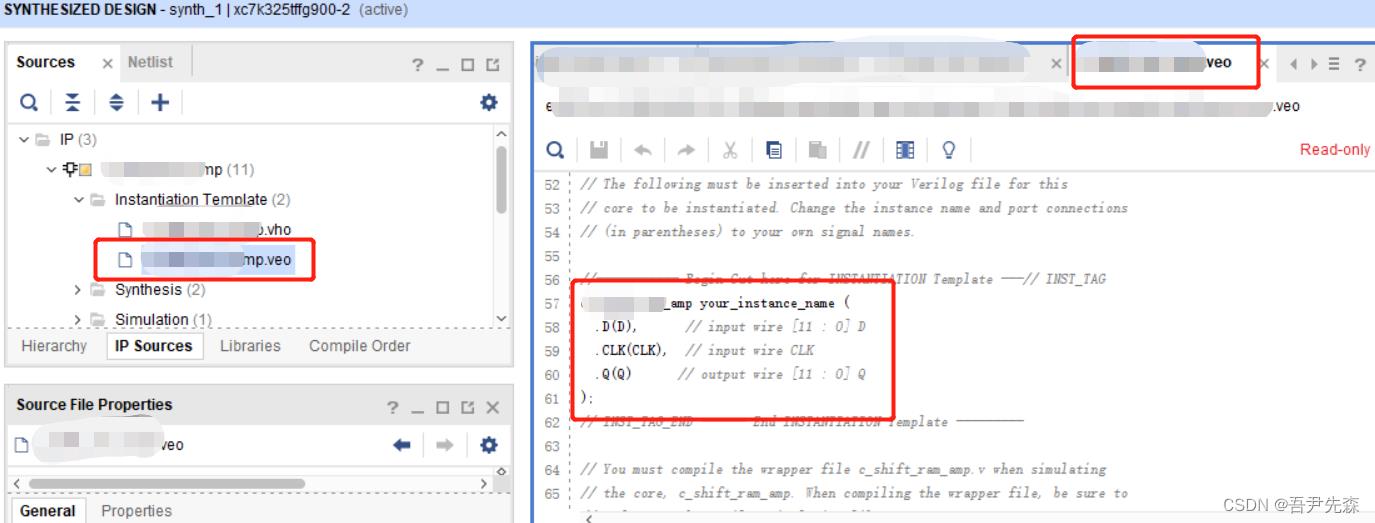

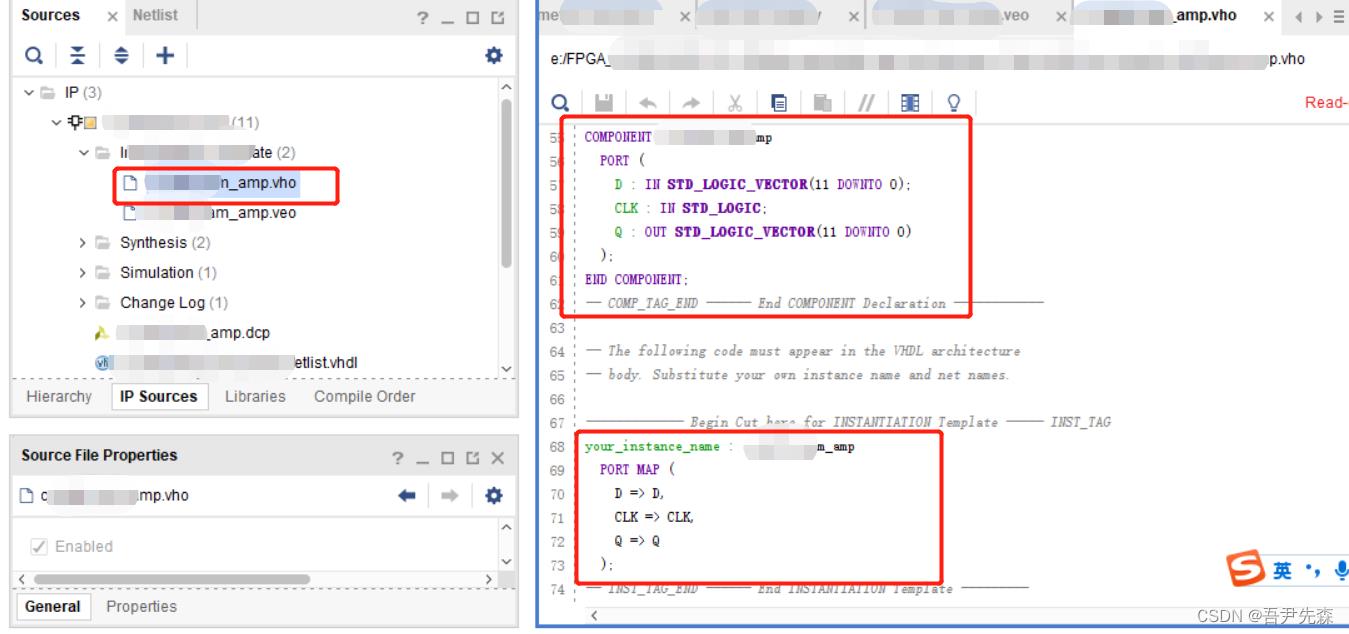

(2)Vivado软件的ip核的例化模板

vivado的例化模板在生成IP中自动生成,如下,在工程source中找到所要例化的IP,红色框中的.veo文件中即是该IP的verilog 例化模板,而红色框上面的.vho文件中即是该IP的vhdl例化模板

2. 自行设计的模块

如果模块是自行设计的模块,那么例化模块不会自动生成,但是也有一些快速的方式。

(1)利用ISE软件

这个方法是我经常会用到的,如果模块接口很多的时候,是一种快速的模板生成方式。

只需要将自己设计的模块添加到某一个ISE工程之中,再点击ISE软件具有的一键生成,即可得到自己设计模块的模板。

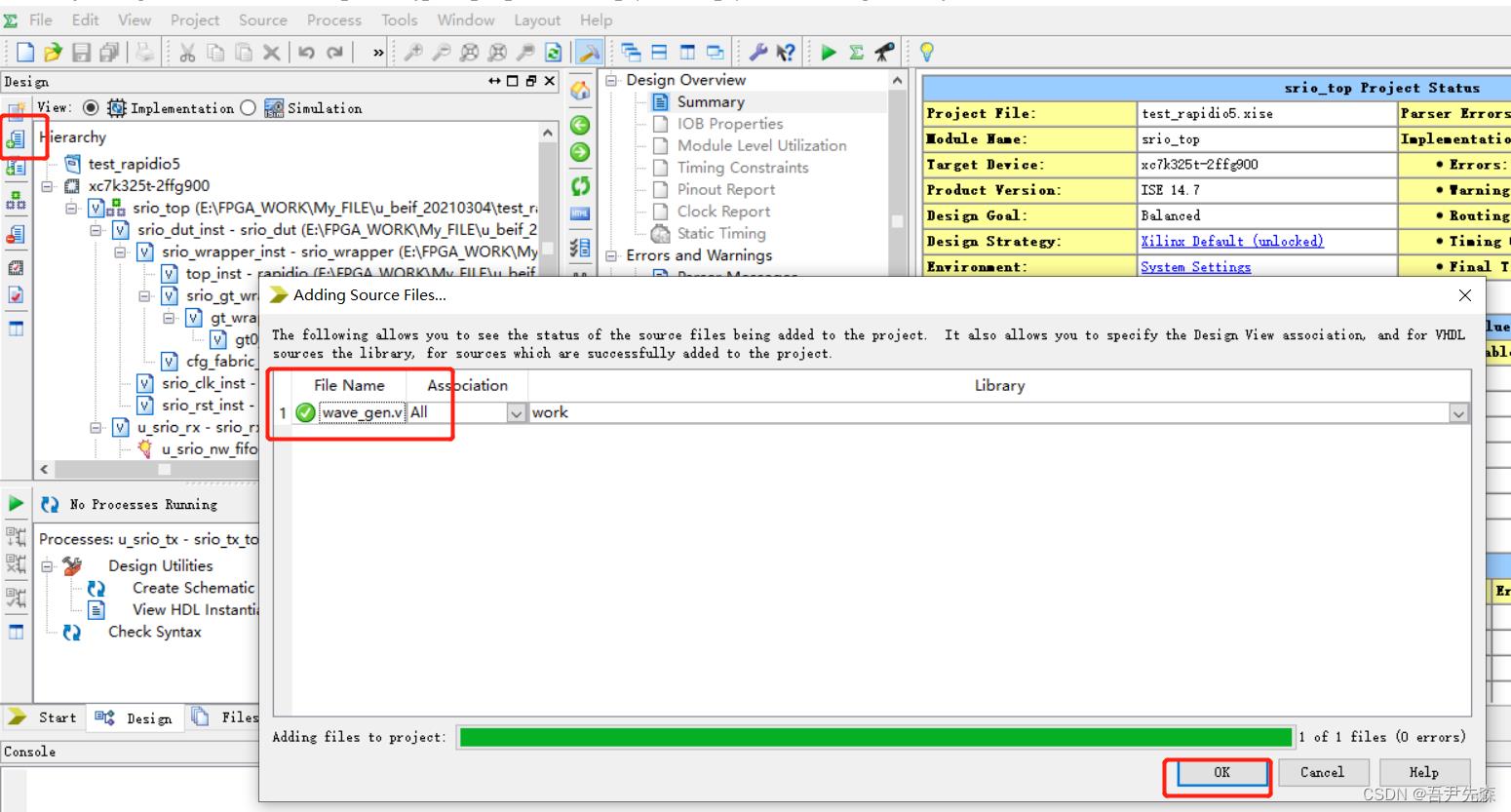

a) 选择如下第一个红框中的+,选择自己设计模块的路径,然后再选择ok,即可将模块添加到当前的工程中。

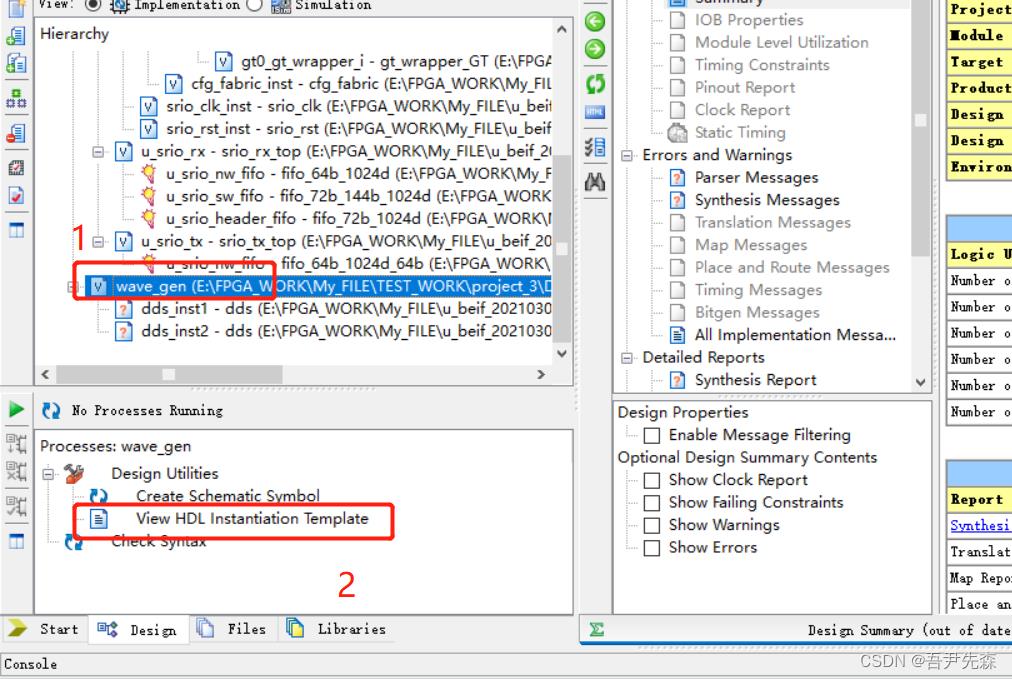

b)再选中我们添加的模块,再点击下方的生成例化模板即可得到想要的模块模板。

(2)利用vivado软件的插件

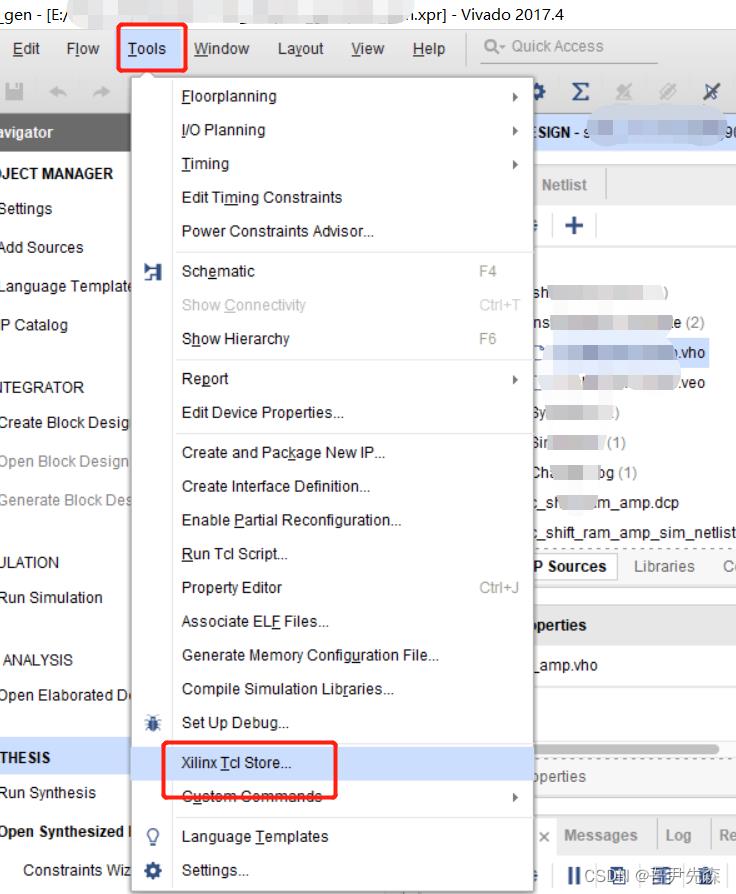

首先要在vivado中安装Design Utilities插件, 点击Tools --Xilinx Tck Store选项,如下

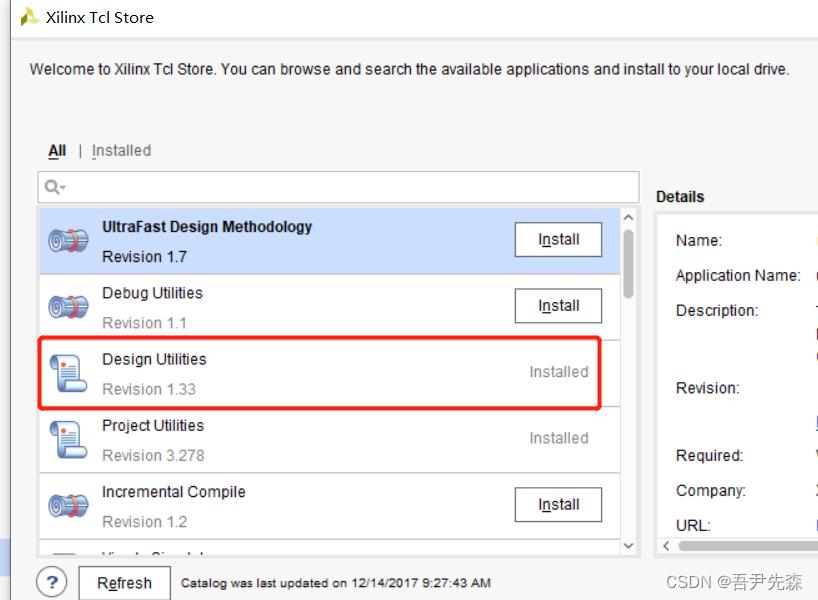

然后,点击Install, 安装Design Utilities

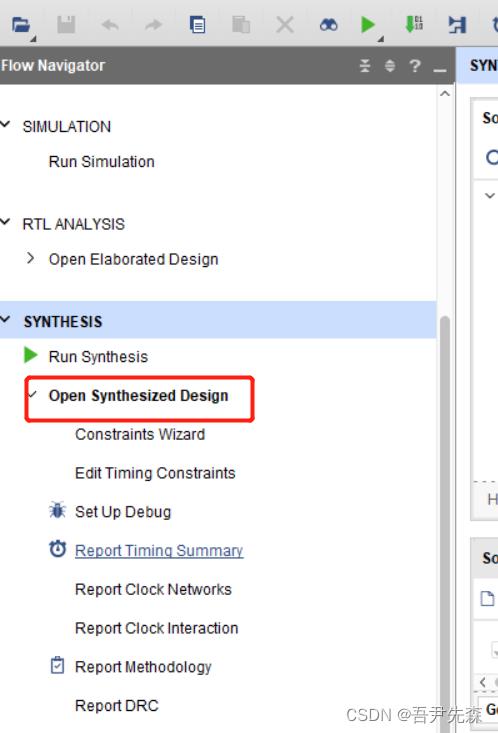

再把要生成例化模板的HDL文件设置为top文件,并点击Open Elaborated Design

在Tcl Console中执行指令

xilinx::designutils::write_template -template -verilog

即可生成verilog的例化文件。

在Tcl Console中执行指令

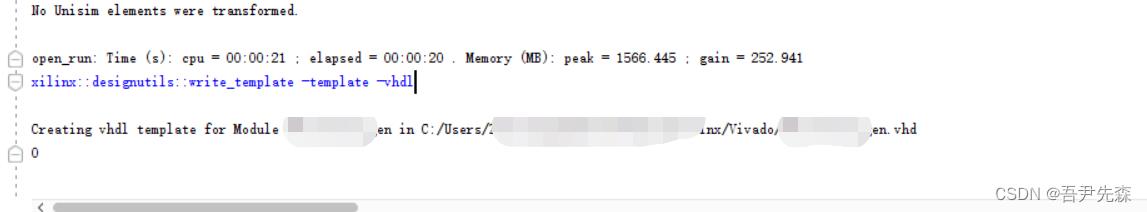

xilinx::designutils::write_template -template -vhdl

即可生成vhdl的例化文件。

最后根据提示内容,去对应位置找到生成的例化模板文件即可,如下。

三、结尾

本文阐述了快速生成verilog\\vhdl例化模块模板的几种方法,有补充的可在下方留言评论,笔耕不辍,厚积薄发。

以上是关于关于FPGA如何快速生成模块的例化模板(实用)的主要内容,如果未能解决你的问题,请参考以下文章