CAPI 初探及使用小结

Posted e_shannon

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了CAPI 初探及使用小结相关的知识,希望对你有一定的参考价值。

作者注:

限于能力和时间,文中定有不少错误,欢迎指出,邮箱yixiangrong@hotmail.com, 期待讨论。由于绝*部分是原创,即使拷贝也指明了出处(如有遗漏请指出),所以转载请表明出处http://www.cnblogs.com/e-shannon/

http://www.cnblogs.com/e-shannon/p/7495618.html

2 CAPI overview

2.1 背景

2.1.1 行业背景

2013年8月由IBM、Google 、NVIDIA等公司联合成立成立了OpenPower 基金会, 其目的是通过建立开源Power生态系统,在warehouse data center(仓储式数据中心)、HPC(高性能计算)等服务器领域与intel展开竞争[dream1] 。4年里,先后有150多家企业加入,涉及从芯片到I/O、固件、系统、软件等各个产业链。OpenPower成立后IBM于2014年推出的第一款CPU是Power8,而CAPI1.0(一致性加速处理器接口)是Power8 系统所支持的重要特性之一,用于减轻CPU负担,实现CPU加速的功能。

2017年IBM推出Power9,Power9 基于14nm FineFET工艺,8billion个晶体管(注:Power9将是检验IBM的openPower策略的重要筹码,希望能抢回HPC和超*规模数据中心市场份额的10%-20%)。同时作为Power9所支持的重要特性CAPI2.0已经公布,相比于1.0,支持PCIE Gen4(到底是4GB/s还是2GB/s的速率?Power9似乎指的是4GB/s),以及在AFU接口添加了DMA通道,支持PCIE的native 操作,便于AFU直接通过PCIE访问。值的一提的是其提供了NVlink接口可以直接对接nVIDIA的GPU,也可以复用为OpenCAPI的phy(bluelink)。(yxr注:OpenCAPI在后续会介绍)

2.1.2 技术背景以及开放式总线接口

由于在*数据/云计算/HPC(超算)/人工智能(深度学*)等*计算*存储领域,单靠CPU性能提升无法胜任越来越复杂的高运算量的需求。最近的趋势显示[dream2] ,CPU创造的价值越来越小,而加速器以及更多的依附于CPU的疯狂创新则创造了更*的价值,所以高速、低延迟、协同操作(coherent)的(CPU)高性能总线(或称为互联加速接口)成为了业界急迫的需求。CAPI则是在这种背景下出现(yxr注:对应于intel,则是QPI通道),但其依附于OpenPower的CPU体系。业界为了满足业务需求,更希望能出现一套开放式总线,独立于不同的ISA和CPU体系,并且不仅仅为了对接accelerator,而且也面向未来高速的memory,网络存储以及高速network,实现计算机集群的互联和高速运算。所以2016年共出现了3个开放标准,分别是CCIX,Gen-Z,OpenCAPI[dream3] 。

三个标准的目的相似,侧重点有些差异,成员也互相交叉,甚至有成员在三个组里(比如AMD、IBM、Xilinx、Micron等,而Google和nVIDIA仅仅在OpenCAPI,当然intel不在这三个组里)。

CCIX物理介质基于PCIE,实现处理器和加速器全cache一致性。而Gen-Z则侧重于机框之间的互联一致性加速。OpenCAPI则获得了IBM的Power9支持。(yxr猜测:相信最后这三个标准将会统一,因为其共同的敌人应该是intel吧,也许intel加入后又不同了)

2.2 Cache

CAPI里的coherent是指cache coherency。而理解cache coherency,需要从cache的认识入手,对于cache熟悉的读者可以略过本节,以下均是自己不专业地从网上搜罗整理。

2.2.1 浅析Cache

由于CPU运算速度要比内存读写速度快很多,这样会使CPU花费更多时间等待数据到来或把数据写入内存。内存一般由高密度的动态内存DRAM组成,所以其访问速度相对慢于CPU速度(需要行地址和列地址,以及刷新操作,等待周期等,并且功耗*)。

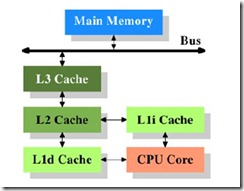

现代计算机中一般在CPU和内存之间插入了一个SRAM,作为cache,用于解决CPU速度运行速度快和内存访问速度相对慢的矛盾。CPU不再能直接访问内存[dream4] ,而是访问cache,见下面示意图

SRAM的访问速度远快于DRAM,克服了CPU访问内存的瓶颈,其缺点是无法做成*容量。引入 Cache(SRAM)的理论基础是程序局部性原理,包括时间局部性和空间局部性。即最近被CPU访问的数据,短期内 CPU还要访问(时间);被 CPU 访问的数据附近的数据,CPU 短期内还要访问(空间)。因此如果将刚刚访问过的数据缓存在 Cache中,那下次访问时,可以直接从Cache中取,其速度可以得到数量级的提高[dream5] 。

在高级的CPU中,存在二级缓存,服务器等CPU则达到三级缓存[dream6] 。Power9含有12个SMT8 core,每个core有三级缓存[dream7] ,10 MB Capacity L3+ 512k L2(SRAM),而一级缓存则由32kB instruction cache(I-cache)和32kB data cache(D-cache)组成。三级缓存工12x10MB=120 MB 其实是Shared Capacity NUCA Cache由eDRAM组成,目的是为了[dream8] *容量并行计算以及异种互动。

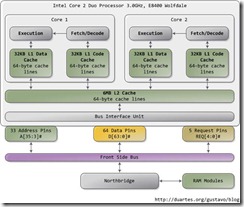

如下是以intel core2 双核处理器为例,其为双核,使用二级缓存。1级缓存是每个core对应有32KB L1 数据和32KB L1 指令。而二级缓存为6MB[dream9] 为双核共享,其cache line均为64byte。(Yxr注:Power9与其相比,似乎是插入了一级SRAM作为2级缓存。)

http://www.cnblogs.com/xkfz007/archive/2012/10/08/2715163.html

2.2.2 Cache访问方式

如上图所示,CPU无法直接访问内存,只能沿着Register —> L1 Cache —> L2 Cache —> L3 Cache —> Memory —> Mass storage的层次结构进行访问。CPU访问内存则存在4种方式,

读写各两种,读有 look through 和 look aside方式,写有 write through 和write back

Look through:指的是CPU读请求只能发给cache,如果命中则cache回内容给CPU,结束本次访问。如果没有命中(hit),则cache将读请求发给内存。

Look aside: 则是CPU的读请求同时给cache和内存[dream10] ,如果cache命中,则cache回数据并且中断内存读。如果没有命中,则不中断内存读操作,继续内存访问,好处是减少了延迟,缺点是每次都将发起内存总线读操作,占用了内存访问总线[dream11] 。

Write through:透过本级缓存,直接把数据写到下一级缓存(或直接到内存)中,如果对应的段被缓存了,我们同时更新缓存中的内容(甚至直接丢弃)。优点是操作简单,保证缓存和内存一致,缺点是降低了系统写速度,占用了内存的访问总线。

Write back:(yxr注:有两种说法,回写时机不一样,不清楚哪种正确!!!)

1种说法.缓存不会立即把写操作传递到下一级,而是仅修改本级缓存中的数据,并且把对应的缓存段标记为“脏”段。脏段会触发回写,也就是把里面的内容写到对应的内存或下一级缓存中。回写后,脏段又变“干净”了。当一个脏段被丢弃的时候,总是先要进行一次回写[dream12] 。

2种说法. 数据一般只写到Cache,这样有可能出现Cache中的数据得到更新而主存(Main Storage)中的数据不变(数据陈旧)的情况。但此时可在Cache 中设一标志地址及数据陈旧的信息,只有当Cache中的数据被再次更改时,才将原更新的数据写入主存相应的单元中,然后再接受再次更新的数据。这样保证了 Cache和主存中的数据不致产生冲突。

有些(*多数是比较老的)CPU只使用直写模式,有些只使用回写模式,还有一些,一级缓存使用直写而二级缓存使用回写。这样做虽然在一级和二级缓存之间产生了不必要的数据流量,但二级缓存和更低级缓存或内存之间依然保留了回写的优势。

2.2.3 缓存映射方式和cache line

Cache的内部结构含有内存地址和cache内部地址映射关系,以及存储内存数据的单元。

Cache line是cache加载内存的基本操作单位,每次加载一个cache line而不是一个字节。*小是32(较早的ARM、90年代/2000年代早期的x86和PowerPC)、64(较新的ARM和x86)或128(较新的Power ISA机器)字节,(yxr注:cache line*小可能和DRAM内存的内部结构有关,一个基本内存访问的基本操作可能是8个时钟的数据,而数据线宽度为32,64,128bit (注意不要跨DRAM的bank[dream13] ))

每个cache line,都有如下类似的结构,tag是数据块在内存中的地址,data block则是数据内容,flag bits则是valid和脏等标志,甚至一些算法信息

而相对于内存的物理地址,则可理解为如下结构,其原因是缓存与内存的映射关系造成。

这里的 page 不是分页机制的page概念,而是cache 内部的page,line则是cache line所在的位置,offset则是具体数据所在字节(?理解正确吗),具体理解需要从cache的映射关系来看。

Cache与主存有三种映射关系,可参考如下资料(高速缓存与主存的三种映射方式[dream14]

http://blog.csdn.net/hs794502825/article/details/37937949 (ok)讲的比较好,这里直接搬过来), https://en.wikipedia.org/wiki/CPU_cache,http://blog.sina.com.cn/s/blog_5ccec1e30100yte3.html)

1、全相联映射方式 (full-associative)

2、直接相联映射方式 (direct map,相当于1-way associative) http://www.cs.umd.edu/class/sum2003/cmsc311/Notes/Memory/direct.html

3、组相联映射方式 (2-way,8-way N-Way Set-Associative) 这个是现在CPU中用的较多的方式,