鲁棒性检查(中)

Posted KuoGavin

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了鲁棒性检查(中)相关的知识,希望对你有一定的参考价值。

文章目录

10.5 时钟门控检查(Clock Gating Checks)

当一个门控信号(gating signal)可以控制逻辑单元中时钟信号(clock signal)的路径时,将会执行时钟门控检查(clock gating check),一个示例如图10-10所示。逻辑单元与时钟相连的引脚称为时钟引脚(clock pin),与门控信号相连的引脚称为门控引脚(gating pin),产生时钟门控的逻辑单元也称为门控单元(gating cell)。

进行时钟门控检查的条件之一是:必须将通过门控单元的时钟用作下游的时钟。下游时钟的使用可以是触发器的时钟、也可以是扇出到输出端口、也可以是作为衍生时钟的主时钟。如果时钟不用作门控单元之后的下游时钟,则不会推断出时钟门控检查。

时钟门控检查的另一个条件针对的是门控信号:门控引脚上的信号不应是时钟,或者如果是时钟,也不应将其用作下游时钟(例如本节稍后要介绍的将时钟用作门控信号的一个示例)。

在一般情况下,时钟信号和门控信号不需要连接到同一个逻辑单元(例如与门、或门),但是可以输入到任意逻辑块。在这种情况下,为了推断出时钟门控检查,检查的时钟引脚和检查的门控引脚必须扇出到公共输出引脚。

可推断出两种时钟门控检查:

- 高电平(Active-high)有效时钟门控检查:门控单元具有“与”功能或“与非”功能;

- 低电平(Active-low)有效时钟门控检查:门控单元具有“或”功能或“或非”功能;

高电平有效和低电平有效是指门控信号的逻辑状态,该逻辑状态用以使能门控单元输出端的时钟信号。如果门控单元是门控关系不明显的复杂功能,例如多路复用器(MUX, multiplexer)或异或门(XOR),则STA输出通常会给出警告,提示没有推断出时钟门控检查。但是,可以通过使用命令set_clock_gating_check为门控单元显式地指定时钟门控关系。在这种情况下,如果set_clock_gating_check命令与门控单元的功能不一致,则

S

T

A

STA

STA通常会给出警告。我们将在本节稍后部分介绍此类命令的示例。

如前所述,只有当时钟不用作下游时钟时,它才可以用作门控信号,考虑图10-11中的示例。由于定义了 C L K A CLKA CLKA的衍生时钟,因此 C L K B CLKB CLKB不用作下游时钟,即 C L K B CLKB CLKB的路径被衍生时钟的定义阻塞了。因此,针对这个与门单元会推断出时钟 C L K A CLKA CLKA的时钟门控检查。

高电平时钟门控(Active-High Clock Gating)

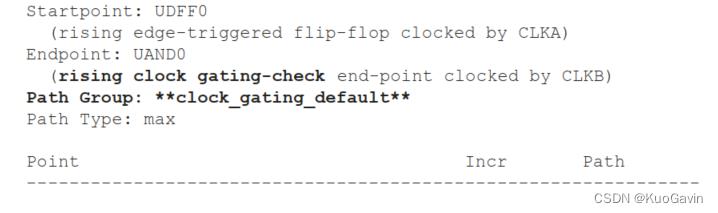

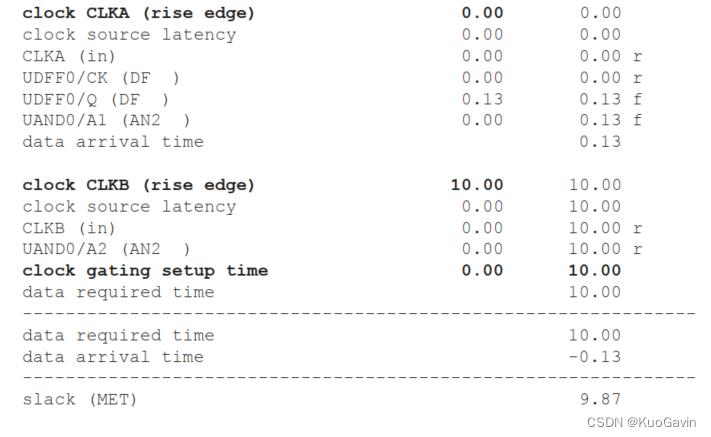

我们现在检视一个高电平时钟门控检查的时序关系。发生在与和非与单元;一个与单元例子如图10-12所示。门控单元的 B B B引脚是时钟信号, A A A引脚是门控信号。

我们假定时钟 C L K A CLKA CLKA和时钟 C L K B CLKB CLKB具有相同的波形。

create_clock -name CLKA -period 10 -waveform 0 5 \\

[get_ports CLKA]

create_clock -name CLKB -period 10 -waveform 0 5 \\

[get_ports CLKB]

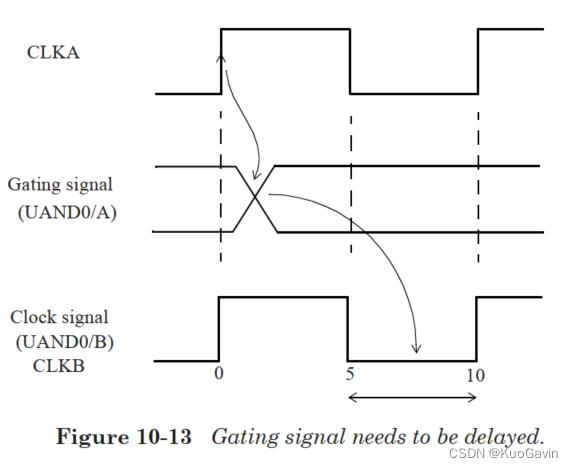

因为它是一个与门单元,所以门控信号引脚 U A N D 0 / A UAND0 / A UAND0/A上为高电平时才会打开门控单元,并允许时钟传播通过。时钟门控检查旨在验证门控引脚的电平切换不会为扇出时钟创建时钟有效沿。对于上升沿触发的逻辑,这意味着门控信号的上升沿发生在时钟的无效周期内(当其为低电平时)。类似地,对于下降沿触发的逻辑,门控信号的下降沿应仅在时钟为低电平时产生。注意,如果时钟同时驱动上升沿和下降沿触发的触发器,则门控信号的任何边沿(上升沿或下降沿)都必须仅在时钟为低电平时产生。图10-13给出了一个在有效周期期间门控信号电平切换的示例,该信号需要延迟才能通过时钟门控检查。

以上是关于鲁棒性检查(中)的主要内容,如果未能解决你的问题,请参考以下文章