ADS1120 备忘

Posted 研究是为了理解

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ADS1120 备忘相关的知识,希望对你有一定的参考价值。

ADS1120 是一个小型、低功耗、16-bit、ΔΣ 模数转换器(ADC):

- 内置 PGA(1~128)

- 内置参考基准(2.048V)

- 内置温度传感器

- 内置 2 个已配对的可编程电流源

- SPI 通讯接口,使用

模式 1,通过 4 个寄存器配置

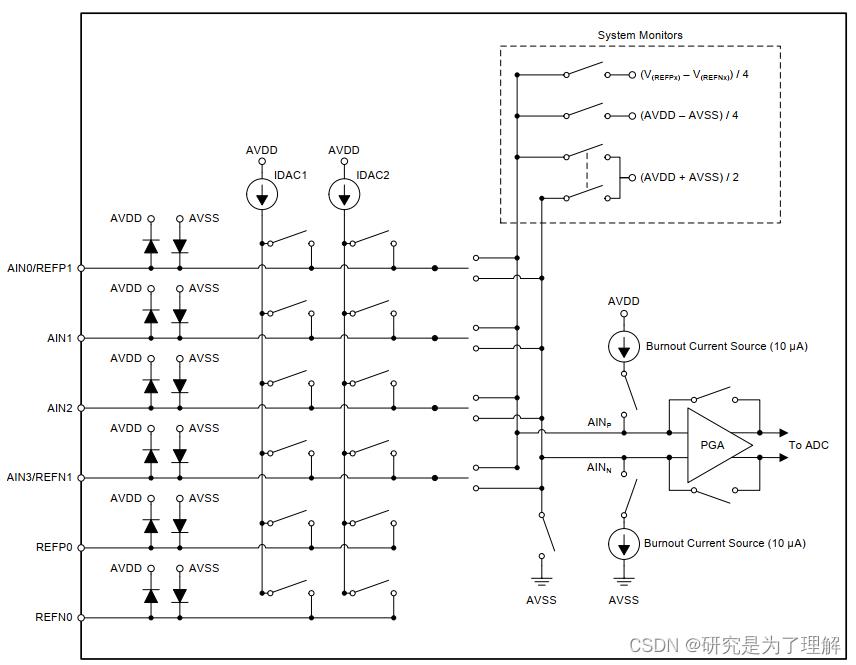

多路复用器

有了多路复用器,就可以测量 4 个单端信号,或者 2 个差分信号,或者1个差分信号加上 2 个单端信号。

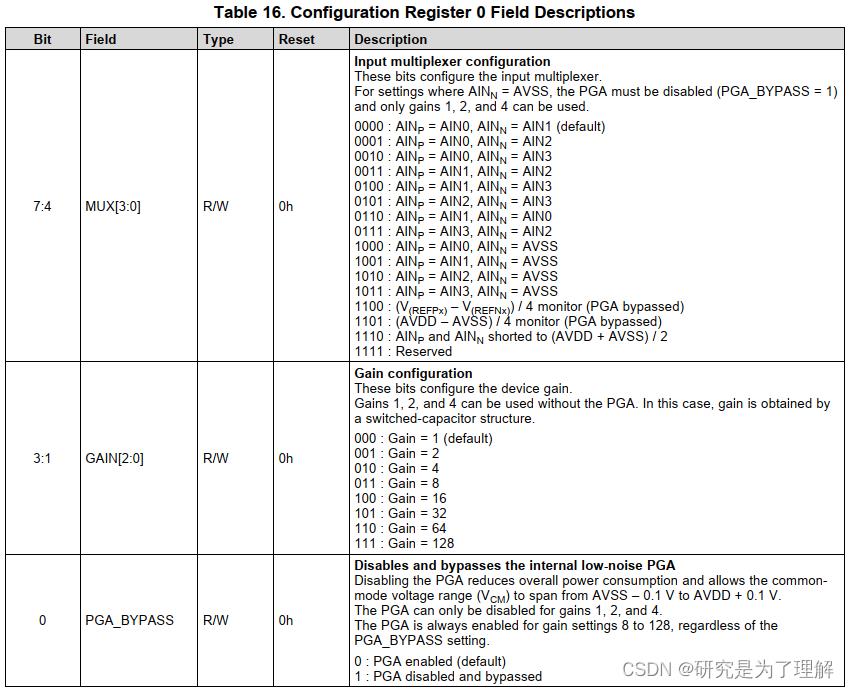

配置寄存器 0 的 bit[7:4] 用于配置多路复用器。

在芯片内部,有静电放电二极管(ESD)保护模拟输入。为了防止 ESD 二极管导通,须确保输入电压为 AVSS-0.3V ~ AVDD+0.3V 之间。如果输入电压有可能超过这个范围,需要加入外部肖特基钳位二极管或者串入电阻(限制输入电流),根据数据表提供的绝对最大值,引脚能承受的最大电流为 10mA。TI 更推荐使用肖特基二极管钳位。

低噪声 PGA

增益为 1 - 128。

为了保证 PGA 的线性操作,输入信号必须满足特定条件。

PGA 的输出不能达到电源轨,在接近电源轨的 200mV 范围内,内部放大器就开始饱和,变得非线性。

条件1 :

V

C

M

(

M

I

N

)

≥

A

V

S

S

+

0.2

V

+

1

2

G

a

i

n

∗

V

I

N

(

M

A

X

)

V_CM(MIN) ≥ AVSS + 0.2V + \\frac12Gain*V_IN(MAX)

VCM(MIN)≥AVSS+0.2V+21Gain∗VIN(MAX)

且:

V

C

M

(

M

I

N

)

≥

A

V

S

S

+

1

4

(

A

V

D

D

−

A

V

S

S

)

V_CM(MIN) ≥ AVSS + \\frac14(AVDD-AVSS)

VCM(MIN)≥AVSS+41(AVDD−AVSS)

条件2:

V

C

M

(

M

A

X

)

≤

A

V

D

D

−

0.2

V

−

1

2

G

a

i

n

∗

V

I

N

(

M

A

X

)

V_CM(MAX)≤ AVDD - 0.2V - \\frac12Gain*V_IN(MAX)

VCM(MAX)≤AVDD−0.2V−21Gain∗VIN(MAX)

这就是 PGA 的 共模电压要求,其中:

- VIN(MAX) :差分最大输入电压

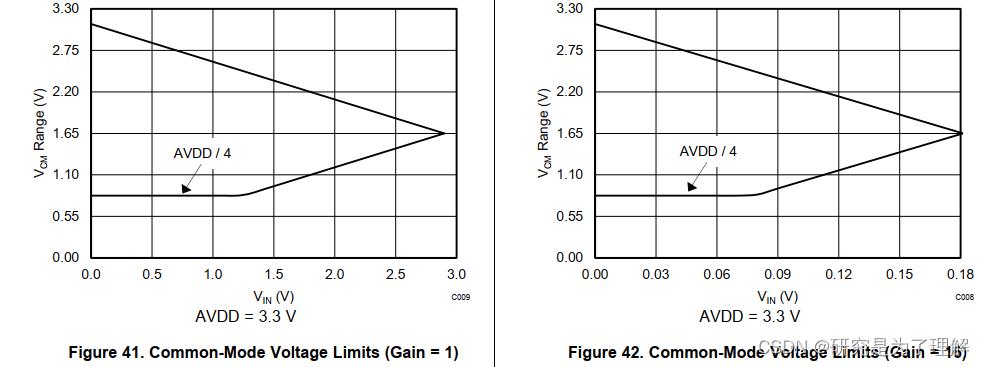

另外数据手册给出了 PGA 共模电压的图解法,分别是增益为 1 和增益 为 16 的图解:

举例说明:

假设一个应用:

AVDD= 3.3VAVSS= 0V- 增益(gain) = 16

- 使用外部参考基准,Vref = 2.5V

易知绝对最大输入电压范围为:±2.5V / 16 = ±0.156V

但是这个应用用不到这么大的输入电压范围,使用的VIN(MAX) = ±0.1V,那么根据上面的公式(条件 1 和条件 2 )可以算出输入共模电压需满足:1.0V ≤ V~CM~ ≤ 2.3V

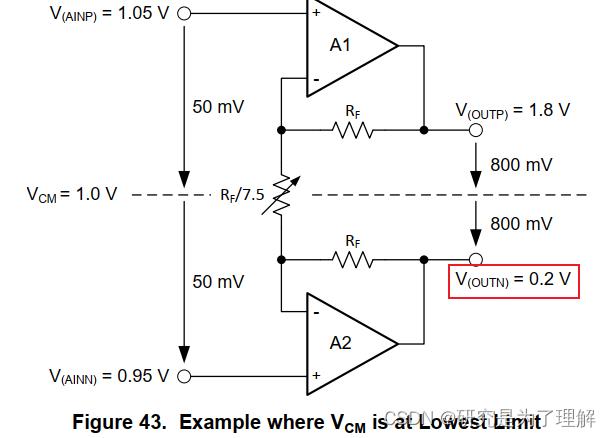

图43 给出一个极限输入极限例子,这个例子中,放大器 A2 的输出已经达到了极限值,如果电压再稍微波动一点,放大器 A2 就会饱和,在设计电路时要避免这种情况,保留一定的余量。

PGA 可以旁路掉。

通过配置寄存器 0 来旁路掉 PGA。旁路掉 PGA 后:

- 增益为 1- 4

- 共模输入电压不再受条件 1 和条件 2 的限制,变为:AVSS - 0.1V ≤ VCM ≤ AVDD + 0.1V

- 可以测量单端信号,AINP = VIN、AINN = AVSS

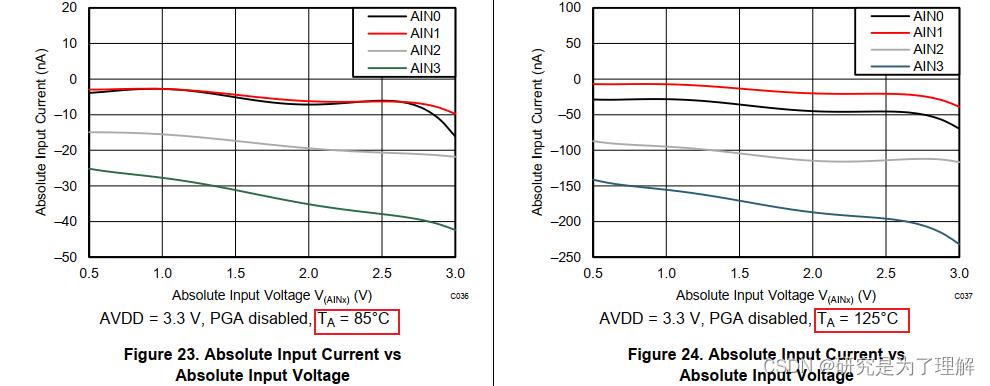

旁路 PGA 后,设备使用带缓冲的开关电容获得增益(1、2、4),尽管使用了缓冲器,也不可避免的对输入产生了影响,根据数据手册给出的图示:

(不同温度下,各输入口的绝对最大电流和绝对最大电压关系图)

(不同温度情况下,各输入口的差分最大电流和差分最大电压关系图)

从这两张图上可以看出:

- 额外输入电流在 nA 级别

- 如果信号源的输出阻抗大,需要外部缓冲放大器,但是外部有源缓冲器一般会引入噪声,也会引入偏移和增益误差。在高精度应用场合需要综合考虑所有因素。

- 如果要减少这种电流影响,优先选择 AIN0 和 AIN1 !!!

数字滤波器

使用 线性相位有限脉冲响应(FIR)数字滤波器 :

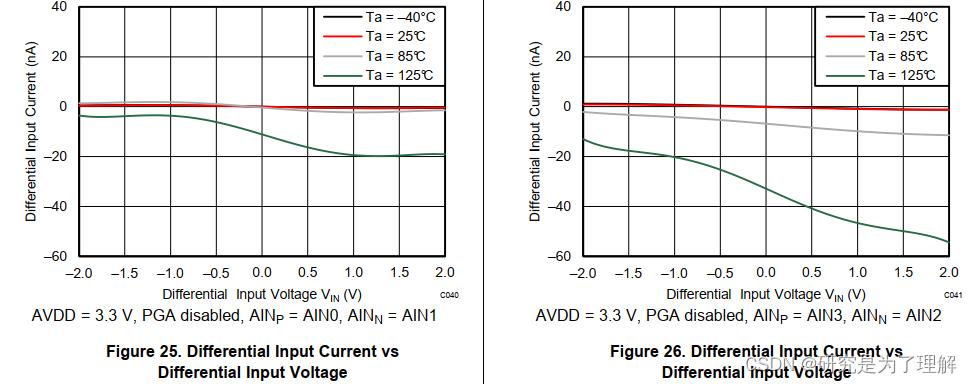

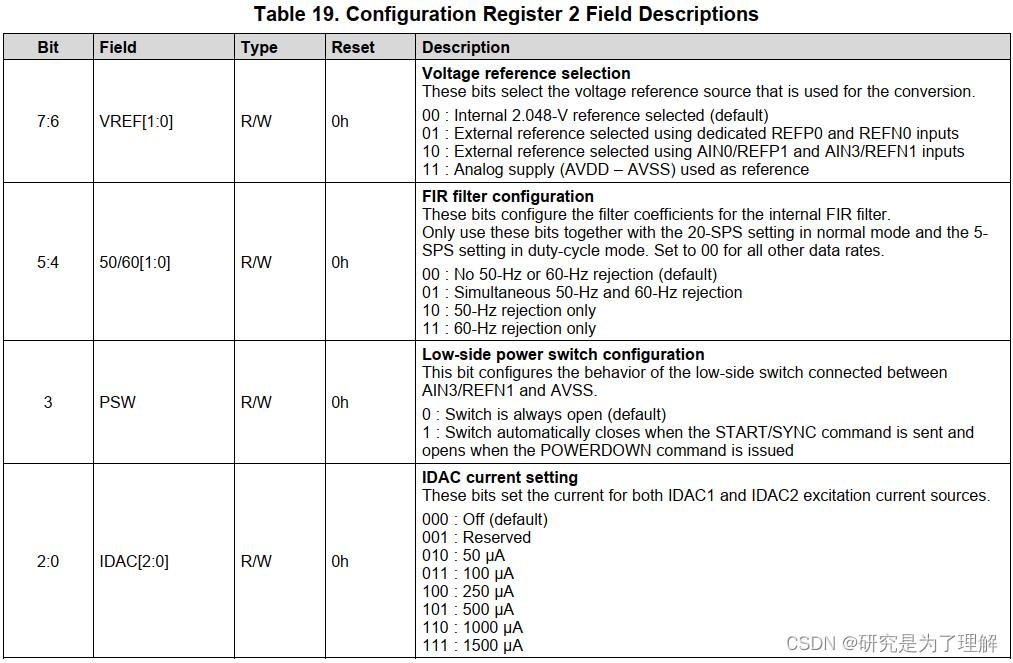

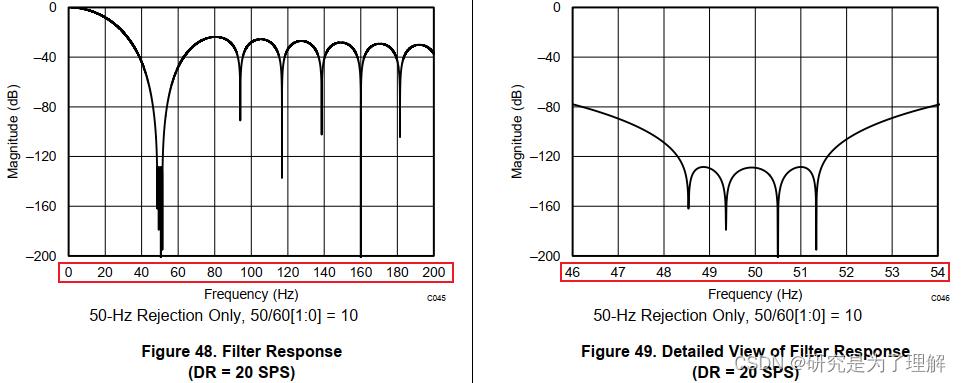

数据转换速率为 5 或者 20 SPS 时,可以对 50Hz 或者 60Hz 或者 50Hz 和 60Hz 进行谐波抑制。需要手动开启,在配置寄存器 2 中的 50/60[1:0] 位:

数字滤波器的效果可能跟文字反映的不太符合,它只是针对特定的频率进行高效抑制,这个频率范围还非常窄,其它频率范围抑制效果有限。

开启 50Hz 抑制效果图,左图是整体效果,右图是 50Hz 附近的放大图:

数据转换速率为90、175、330、600、1K 和 2K SPS 时,仍具有数字滤波功能,只是不能针对 50Hz 、 60Hz 进行谐波抑制。

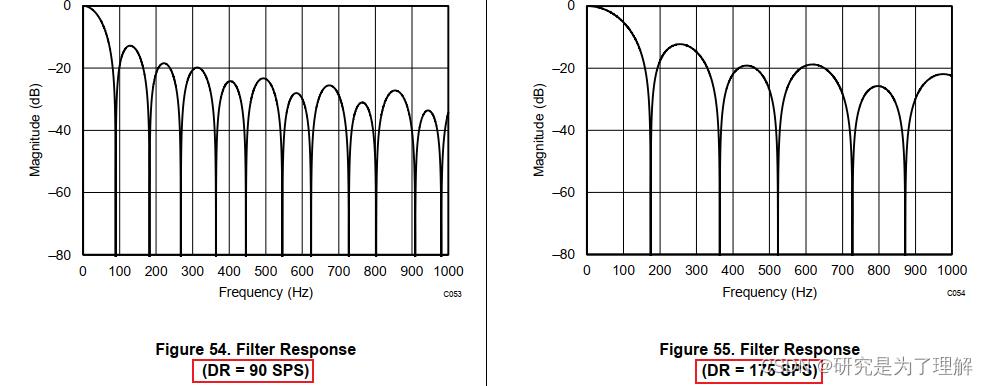

数据转换速率越高,数字滤波器效果越差,比如下面展示了转换速率为 90 SPS 和 175 SPS 时的滤波效果图:

输出数据速率

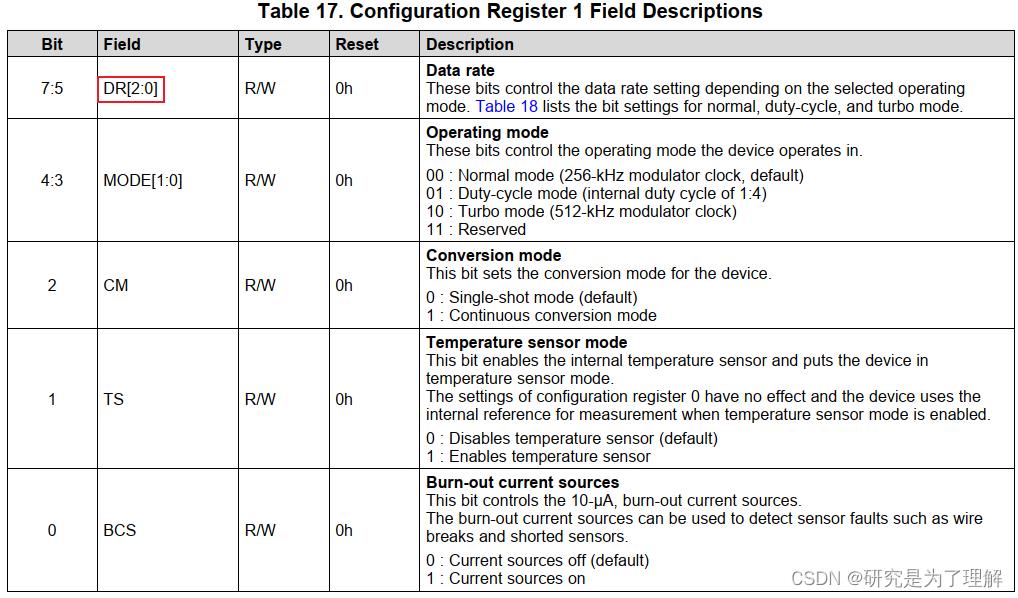

数据速率在配置寄存器 1 中设置,使用 DR[2:0] 位:

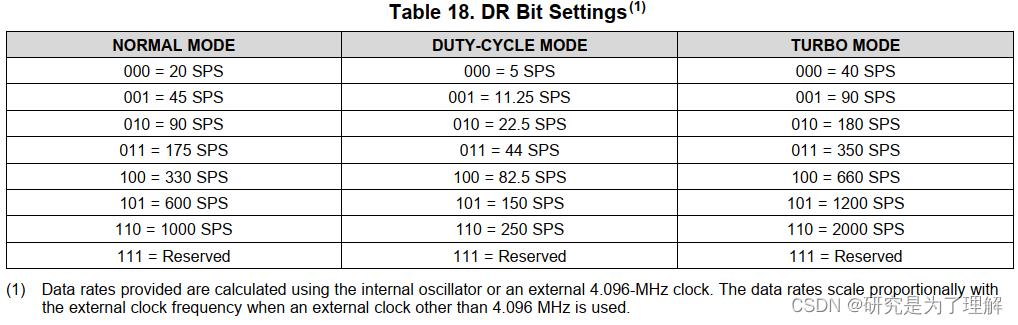

数据速率取决于操作模式,操作模式有三种:Normal、Duty-cycle、Turbo 。不同模式下的数据速率:

注:本表提供的数据速率是使用内部晶振或者外部 4.096MHz 时钟的前提下得出的。如果使用 4.096MHz 以外的外部时钟,本表中的数据需要和外部时钟频率成等比缩放。

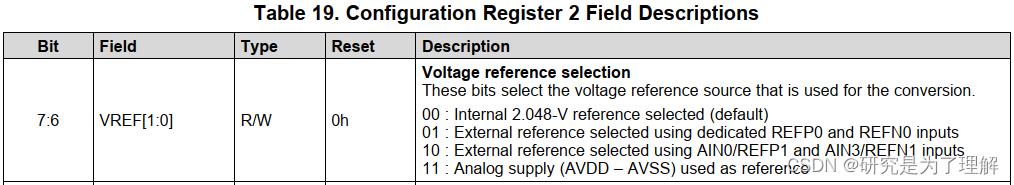

参考电压

内部集成低飘移 2.048V 参考源。芯片的参考电压可以选择外部参考源、内部参考源和模拟电压(AVDD - AVSS)。根据配置寄存器 2 的 VREF[1:0] 来选择。

上电后、退出掉电模式或者从外部参考源切换到内部参考源,最多只需 25us ,内部参考源就能充分稳定。

激励电流源

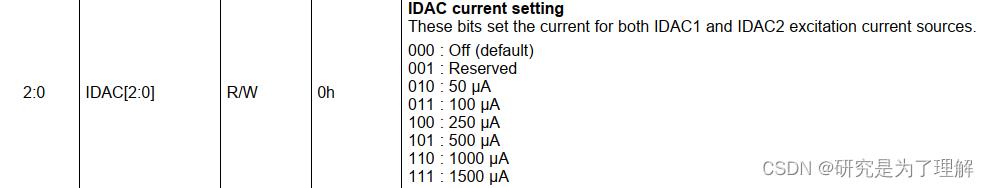

芯片内部集成两路已匹配的激励电流源,一般用于 RTD 温度采集。电流源可以输出不同的电流,使用配置寄存器 2 的 IDAC[2:0] 来选择:

编程输出电流后,需要最多 200us 的时间启动。

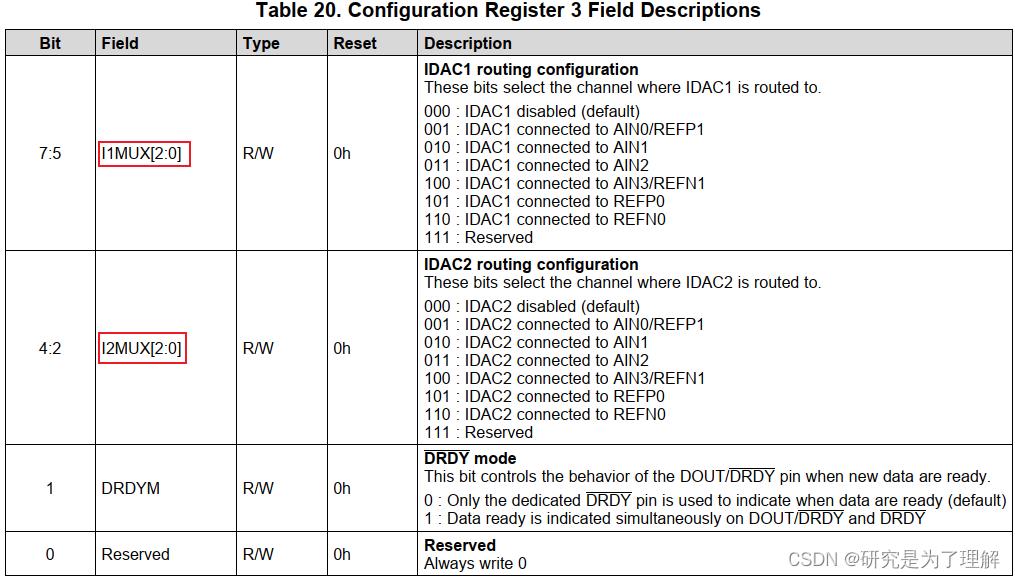

电流源可以从任意模拟引脚输出电流,这需要手动配置,配置寄存器 3 的 I1MUX[2:0] 和 I2MUX[2:0] 用于选择输出引脚:

必须注意电流源有电压限制,IDAC 驱动的负载电压必须 ≤ AVDD - 0.9 V !否则输出电流精度不能保证。

TI 推荐先编程输出电流,再配置电流输出引脚。

失调校准

内部多路复用器可以将 PGA 的两个输入短路到 (AVDD + AVSS) / 2 ,此时可以测量和校准失调电压。方法是在这种情况下获取多个读数,求平均值然后存储起来,称为校准值,后续真实测量读数减去这个校准值。

转换模式

- 单次转换模式

在单次转换模式,仅在发出START/SYNC命令后,设备才执行 1 次转换,并将该值存储在内部数据缓冲器中,然后进入低功耗状态。在低功耗状态下,内部振荡器和所有模拟电路(激励电流源除外)均关闭。

此外,对任意配置寄存器的写操作也会开始新的转换。当转换正在进行时,向任意寄存器的写动作都相当于发出了新的START/SYNC命令:停止当前转换并重启单个新的转换。 - 连续转换模式

在连续转换模式下,设备连续的执行转换。当一个转换完成,设备将转换结果保存到内部数据缓冲区,然后立即开始新的转换。可以随时读取数据,而不必担心数据损坏,并始终反映最近完成的转换。

启动连续转换的步骤为:将配置寄存器 1 的CM位置一,然后跟着发出START/SYNC命令。在发出START/SYNC命令最后一个 SCLK 下降沿后的 210 * tCLK(Normal 模式和 Duty-cycle 模式)或者 114 * tCLK (Turbo 模式)时间后,第一次转换开始。(使用内部晶振时,210 个时钟大约 52.5 us)

当转换正在进行时,向任意寄存器的写动作会重启当前转换。TI 推荐在设置CM位为 1 后,总是立即发送一个START/SYNC命令。

编程

串行接口

使用 SPI 接口通讯。使用模式 1(CPOL = 0,CPHA = 1)。

CS 引脚低有效,为高时,串行接口复位:忽略 SCLK 引脚、DOUT/DRDY 引脚高阻。如果没有和其它设备共享 SPI 总线,CS 引脚可以设置为常低。

SCLK 引脚在空闲时为低电平。在 SCLK 的下降沿,设备锁存 DIN 上的状态,在SCLK 的上升沿,设备向 DOUT/DRDY 引脚 输出新的状态。

SPI超时:这个特性尤其适用于 CS 引脚直连到地的情况。

- Normal 模式和 Duty-cycle 模式下,超过 13955 * tMOD 时,SPI超时发生。在这种情况下,tMOD = 256KHz,所以这个超时时间约为 54.5 毫秒。

- Turbo 模式下,超过 27910 * tMOD 时,SPI超时发生。在这种情况下,tMOD = 512KHz,所以这个超时时间也是约为 54.5 毫秒。

数据格式

以二进制补码的形式提供 16 bits 数据。

1 LSB = +FS / 215

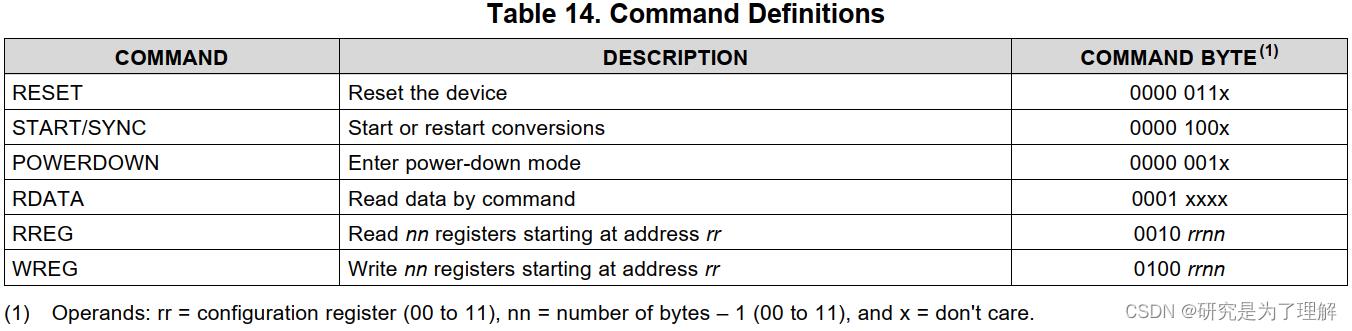

命令

共 6 个不同的命令:

RESET:复位命令。发送复位命令后至少等待 50us + 32 * tCLK 时间后,再发送其它命令。(使用内部晶振时或外部4.096MHz时钟时,32 个 tCLK 为 8us。START/SYNC:启动转换命令。单次转换模式下,用于启动单次转或者在转换期间重启单次转换。连续转换模式下,必须发送一次该命令启动连续转换,在转换期间发送该命令重启连续转换。POWERDOWN:掉电命令。设备进入掉电模式后,内部所有模拟组件掉电、低侧开关打开、两个激励电流源关闭,但保持所有寄存器的值。如果在转换期间发出掉电命令,则在当前转换完成后,再进入掉电模式。一旦发出START/SYNC命令,所有模拟组件恢复到以前的状态。RDATA:读数据命令。读取最近的转换结果。RREG:读配置寄存器命令。读取寄存器rr起始的nn+ 1 个寄存器。WREG:写配置寄存器命令。向寄存器rr起始的nn+ 1 个寄存器写入数据。寄存器将在最后一个 SCLK 下降沿更新新的配置。

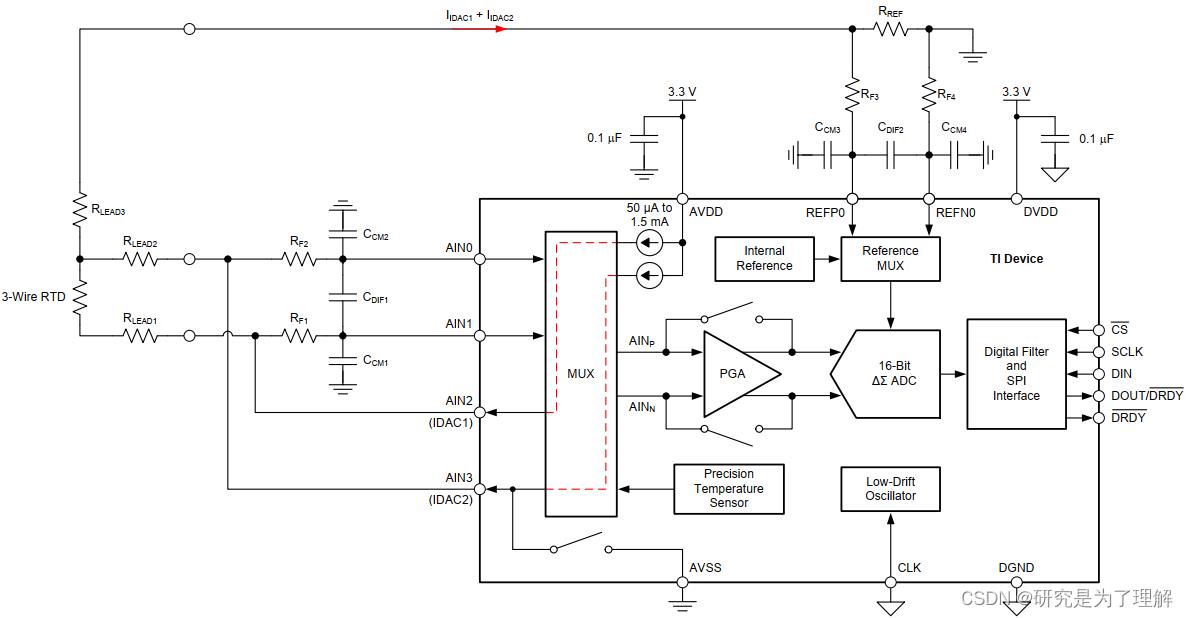

比率式 RTD 当前电阻值推导

三线制比率计原理框图为:

芯片内部激励电流源流过测温电阻 RRTD和参考电阻 RREF,容易得出测温电阻 RRTD上的电压 VRTD 为:

V

R

T

D

=

R

R

T

D

∗

I

I

D

A

C

1

V_RTD = R_RTD * I_IDAC1

VRTD=RRTD∗IIDAC1

容易得出参考电阻 RREF上的电压 VREF 为:

V

R

E

F

=

R

R

E

F

∗

(

I

I

D

A

C

1

+

I

I

D

A

C

2

)

V_REF = R_REF * (I_IDAC1 + I_IDAC2 )

VREF=RREF∗(IIDAC1+IIDAC2)

所以,对于当前测温电阻 RRTD,ADC 当前码值 CodeRTD为:

C

o

d

e

R

T

D

=

V

R

T

D

∗

G

a

i

n

V

R

E

F

∗

C

o

d

e

F

U

L

L

Code_RTD = \\fracV_RTD * GainV_REF * Code_FULL

CodeRTD=VREFVRTD∗Gain∗CodeFULL

其中:

- Gain 为 PGA 增益

- CodeFULL 为 ADC 满量程码值

将 VRTD 和 VREF 的值带入上面公式:

C

o

d

e

R

T

D

=

R

R

T

D

∗

I

I

D

A

C

1

∗

G

a

i

n

R

R

E

F

∗

(

I

I

D

A

C

1

+

I

I

D

A

C

2

)

∗

C

o

d

e

F

U

L

L

Code_RTD = \\fracR_RTD * I_IDAC1 * GainR_REF * (I_IDAC1 + I_IDAC2 ) * Code_FULL

CodeRTD=RREF∗(IIDAC1+IIDAC2)RRTD∗IIDAC1∗Gain∗CodeFULL

假设 IIDAC1 等于 IIDAC2 ,则上式可以简化为:

C

o

d

e

R

T

D

=

R

R

T

D

∗

G

a

i

n

2

∗

R

R

E

F

∗

C

o

d

e

F

U

L

L

Code_RTD = \\fracR_RTD * Gain2 * R_REF * Code_FULL

CodeRTD=2∗RREFRRTD∗Gain∗