CPU运行时优化(高速缓存指令重排内存屏障等)

Posted oahaijgnahz

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了CPU运行时优化(高速缓存指令重排内存屏障等)相关的知识,希望对你有一定的参考价值。

CPU运行时优化(高速缓存、指令重排等)

文章目录

一、CPU高速缓存与缓存一致性协议

1.1 高速缓存

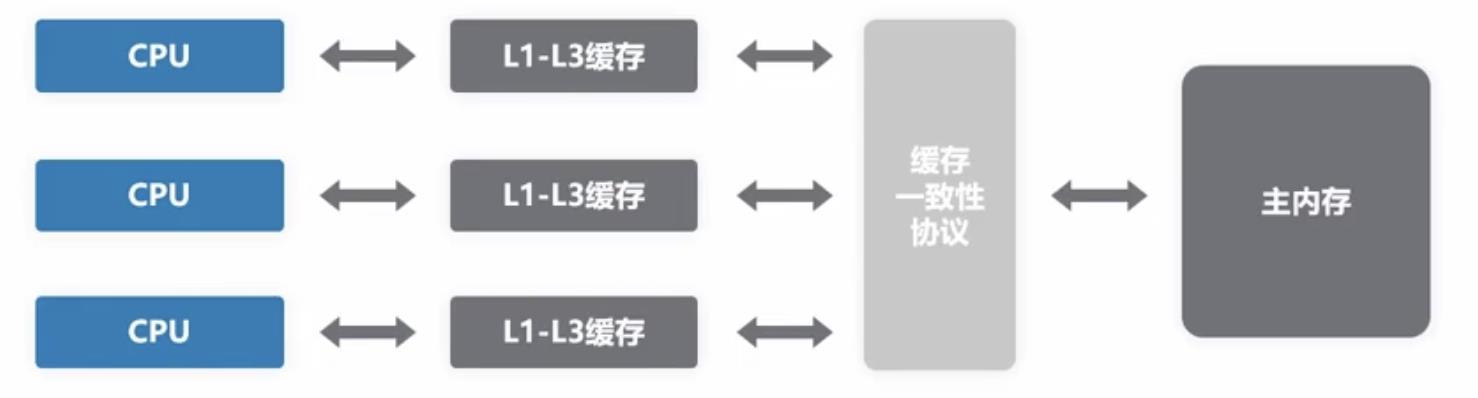

CPU高速缓存主要是用于优化CPU程序执行性能的手段,高速缓存在硬件层面上尽可能地降低处理器访问主内存的时间开销(引申计算机存储结构—磁盘、内存、高速缓存、寄存器)。

L1和L2缓存均是每个CPU独占的缓存区域,往往缓存空间都不大,通常用于数据缓存和指令缓存。L3缓存进一步降低访问内存延迟,同时提升大数据量计算时的处理器性能,L3缓存是多处理器共用的,由此也引出了缓存一致性协议。

1.2 缓存一致性协议(MESI)

MESI协议用于多处理器使用同一高速缓存时,单个CPU对缓存数据的改动需要通知给其他CPU,也就是说CPU要控制自己的读写操作,还要监听其他CPU发出的通知。MESI协议基于此给每条缓存定义了下面四个状态:

- 修改态:此cache行已被修改过(脏行),内容已不同于主内存,为此cache专有。

- 专有态:此cache行内容与主内存中相同,但不出现于其他cache中。

- 共享态:此cache行内容与主内存中相同,同时出现在多行cache中。

- 无效态:此cache行内容无效(空行)。

二、CPU运行时指令重排

三、内存屏障

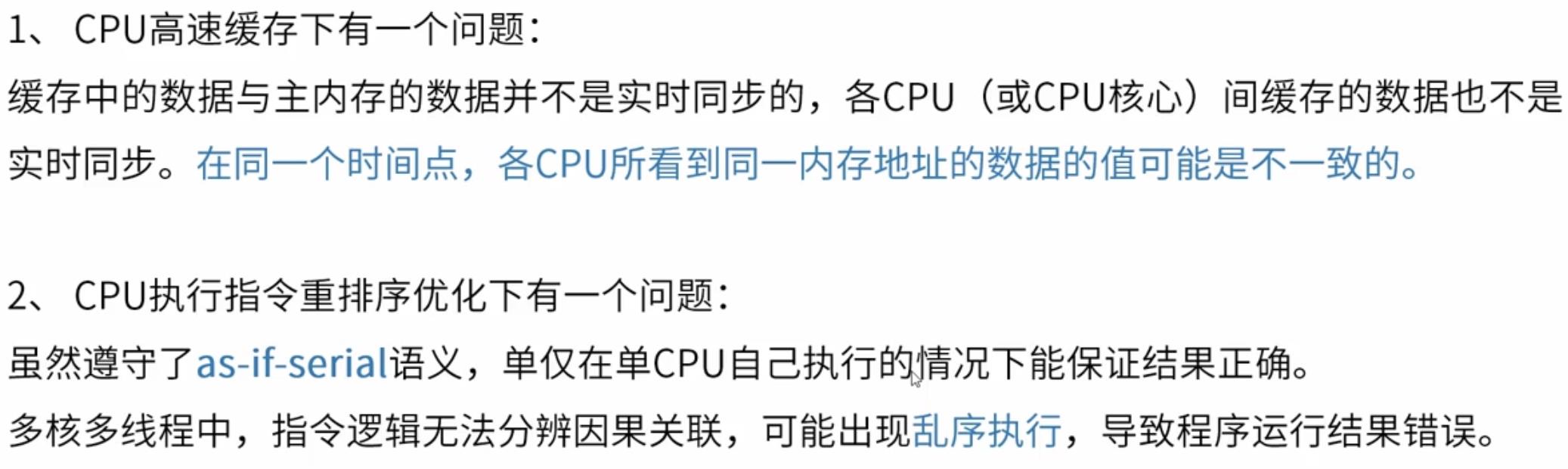

由高速缓存和指令重排引发的两个问题:

对应的解决方案:

- 写内存屏障:在指令后插入写内存屏障指令,让写入缓存中的最新数据更新到主内存中,让其他线程可见。这种强制性的写入主内存操作,CPU就不会因为性能考虑而在此期间进行指令重排。

- 读内存屏障:在指令前插入读内存屏障指令,让高速缓存中的数据失效,强制重新从主内存中加载数据。这种强制性读主内存的操作,使得CPU缓存与主存中的数据保持一致,避免了缓存导致的一致性问题。

实际,读写屏障就是强制让缓存数据和主内存进行更新,来保证之前执行结果的确定性,如此便形成了指令重排序不可逾越的内存屏障。Java中的volatile就是通过读写屏障实现可见性和禁止对应变量指令重排的。

ps:读写内存屏障指令是CPU并发层面上的概念,而JVM在维护卡表(HotSpot用于解决跨代引用问题的记忆集的数组实现),其中卡页的是否变脏是虚拟机中定义的写屏障实现的,但并非上述CPU读写屏障的概念。

以上是关于CPU运行时优化(高速缓存指令重排内存屏障等)的主要内容,如果未能解决你的问题,请参考以下文章