Verilog学习笔记(06)

Posted 高山流水123a s d

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Verilog学习笔记(06)相关的知识,希望对你有一定的参考价值。

文章目录

参考:Verilog数字VLSI设计教程

硬件描述语言Verilog

Verilog HDL数字设计与综合

Verilog HDL 数字集成电路高级程序设计

7. 时序逻辑电路

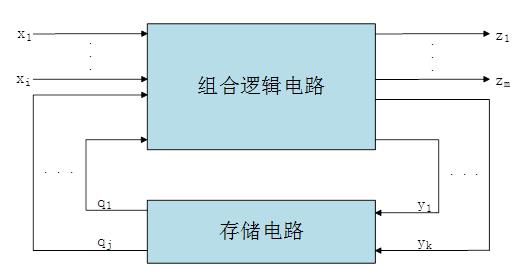

对于一个时序电路,可以把它分为一部分组合逻辑和一部分存储逻辑

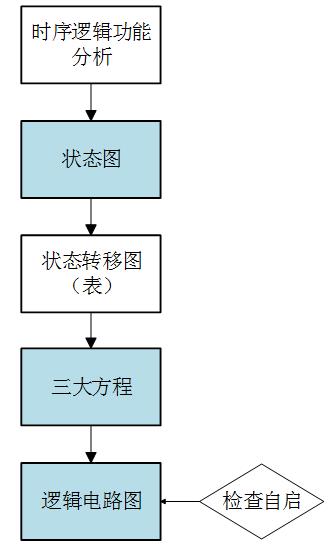

时序电路的三大方程

典型的时序电路设计流程

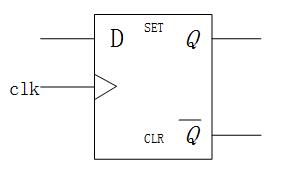

1.触发器

(1)D触发器

module dff(clk,clr,rst,d,q);

input clk,clr,rst,d;

output q;

reg q;

always @(posedge clk or posedge clr)

if(clr==1'b1) q<=1'b0;

else if(rst==1'b1) q<=1'b1;

else q<=d;

endmodule

module dff_tb;

reg clk,clr,rst,d;

wire q;

always begin

#10 clk=1'b1;

#10 clk=1'b0;

end

initial begin

clk=1'b0;

clr=1'b0;

rst=1'b0;clr=1'b0;d=1'b0;

#10 rst=1'b1;clr=1'b0;d=1'b0;

#10 clr=1'b1;rst=1'b1;d=1'b1;

#10 clr=1'b0;rst=1'b0;d=1'b1;

#20 d=1'b0;

#20 d=1'b1;

end

dff u1(clk,clr,rst,d,q);

endmodule

8位D触发器

module eight_register(d,clk,q);

input [7:0] d;

input clk;

output [7:0] q;

reg [7:0] q;

always @(posedge clk)

q<=d;

endmodule

module dff8_tb;

reg [7:0] d;

reg clk;

wire [7:0] q;

always begin

#10 clk=1'b1;

#10 clk=1'b0;

end

initial begin

clk=1'b0;

d=8'b00000000;

#10 d=8'b00000011;

#10 d=8'b00000000;

#10 d=8'b00000111;

#20 d=8'b00001111;

#20 d=8'b00011111;

#20 d=8'b00111111;

end

dff8 u1(.d(d),.clk(clk),.q(q));

endmodule

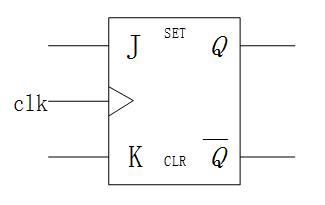

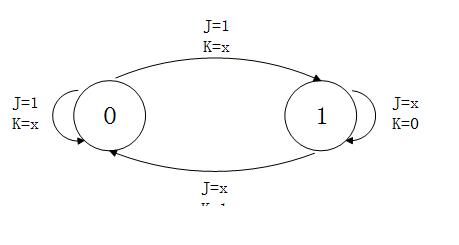

(2)JK触发器

module jk_trigger(clk,j,k,q,qb);

input clk,j,k;

output q,qb;

reg q;

always@(posedge clk)

begin

case(j,k)

2'b00:q<=q;

2'b01:q<=1'b0;

2'b10:q<=1'b1;

2'b11:q<=~q;

default: q<=q;

endcase

end

assign qb=~q;

endmodule

module jk_trigger_tb;

reg clk,j,k;

wire q,qb;

always begin

#10 clk=1'b1;

#10 clk=1'b0;

end

initial begin

clk=1'b0;j=1'b0;k=1'b0;

#10 j=1'b0;k=1'b0;

#20 j=1'b0;k=1'b1;

#20 j=1'b1;k=1'b0;

#20 j=1'b1;k=1'b1;

#20 j=1'b1;k=1'b0;

end

jk_trigger u1(clk,j,k,q,qb);

endmodule

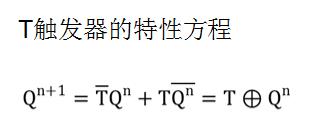

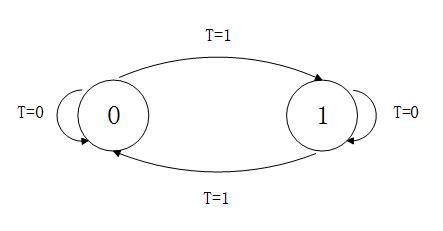

(3)T触发器

module t_trigger(clk,rst,T,dout);

input clk,rst,T;

output dout;

reg dout;

always @(posedge clk or posedgerst)

if(rst==1) dout<=1'b0;

else if(T==1) dout<=~dout;

endmodule

module t_trigger_tb;

reg clk,rst,T;

wire dout;

always begin

#10 clk=1'b1;

#10 clk=1'b0;

end

initial begin

clk=1'b0;

rst=1'b0;T=1'b0;

#10 rst=1'b1;T=1'b1;

#10 rst=1'b0;T=1'b0;

#20 T=1'b1;

#20 T=1'b0;

#20 T=1'b1;

end

t_trigger u1(clk,rst,T,dout);

endmodule

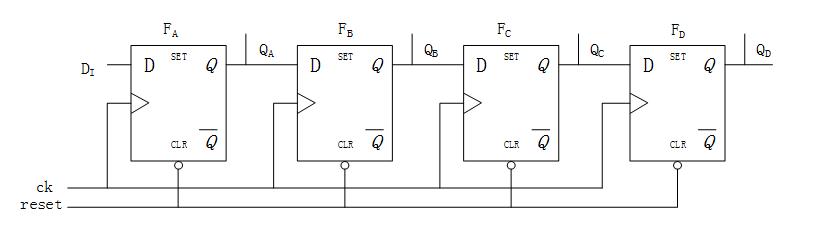

2. 移位寄存器

(1)右移寄存器

module register_right(clk,din,dout);

input clk;

input din;

output [15:0] dout;

reg [15:0] dout;

always @(posedge clk)

dout<=din,dinout[15:1];

endmodule

module register_right_tb;

reg clk;

reg din;

wire [15:0] dout;

always

begin

#10 clk=1'b1;

#10 clk=1'b0;

end

initial begin

clk=1'b0;

din=1'b0;

#10 din=1'b1;

#20 din=1'b0;

#20 din=1'b1;

#100;

end

register_right u1(clk,din,dout);

endmodule

(2)左移寄存器

module register_left(clk,din,dout);

input clk;

input [15:0] din;

output [15:0] dout;

reg [15:0] dout;

always @(posedge clk)

dout<=din[14:0],din[15];

endmodule

module register_left_tb;

reg clk;

reg [15:0] din;

wire [15:0] dout;

always

begin

#10 clk=1'b1;

#10 clk=1'b0;

end

initial begin

clk=1'b0;

din=16'b0000000000000000;

#10 din=16'b0000000000000001;

#20 din=16'b0000000000000011;

#20 din=16'b0000000000000101;

end

register_left u1(clk,din,dout);

endmodule

3. 计数器

(1)反馈清零计数器

module count12(clk,rst_n,co,dout);

input clk,rst;

output co;

output [3:0] dout;

reg [3:0] dout;

always @ (posedge clk)

begin

if(rst_n==1'b0) dout=4'b0000;

else if(dout==4'b1011) dout<=4'b0000;

else dout<=dout+1'b1;

end

assign co=dout[3]&&dout[1]&&dout[0];

endmodule

module count12_tb;

reg clk,rst_n;

wire oc;

wire [3:0] dout;

always begin

#10 clk=1'b1;

#10 clk=1'b0;

end

initial begin

clk=1'b0;

rst_n=1'b0;

#20 rst_n=1'b1;

#100;

end

count12 u1(clk,rst_n,oc,dout);

endmodule

(2)反馈置数计数器

module count10(clk,rst,load,din,dout);

input clk,rst,load;

input [3:0] din;

output [3:0] dout;

reg [3:0] dout;

always @ (posedge clk or posedge rst)

begin

if(rst==1'b1) dout=4'b0000;

else if(load==1'b 1) dout=4'b1001;

else if(dout==4'b0000) dout<=4'b1001;

else dout<=dout-1'b1;

end

endmodule

module count10_tb;

reg clk,rst,load;

reg [3:0] din;

wire [3:0] dout;

always begin

#10 clk=1'b1;

#10 clk=1'b0;

end

initial begin

clk=1'b0;

rst=1'b0;load=1'b0;

#10 rst=1'b1;

#10 rst=1'b0;

#50 load=1'b1;

#10 load=1'b0;

#100;

end

count10 u1(clk,rst,load,din,dout);

endmodule

(3)计数器级联

module count10(clk,rst_n,en,dout,co);

input clk,rst_n,en;

output[3:0] dout;

output co;

reg [3:0] dout;

always @ (posedge clk or negedge rst_n)

begin

if(rst_n ==1'b 0) dout<=4'b0000;

else if(en==1'b1)

if(dout==4'b1001) dout<=4'b0000;

else dout<=dout+1'b1;

else dout<=dout;

end

assign co=dout[0]&dout[3];

endmodule

module count6(clk,rst_n,en,dout,co);

input clk,rst_n,en;

output[3:0] dout;

output co;

reg [3:0] dout;

always @ (posedge clk or negedge rst_n)

begin

if(rst_n ==1'b 0) dout<=4'b0000;

else if(en==1'b1)

if(dout==4'b0101) dout<=4'b0000;

else dout<=dout+1'b1;

else dout<=dout;

end

assign co=dout[0]&dout[2];

endmodule

module count60(clk,rst_n,en,dout,co);

input clk,rst,en;

output[7:0] dout;

output co;

wire c010,co6;

wire[3:0] dout10,dout6;

counter_10 u1(.clk(clk),.rst_n(rst_n),.en(en),.dout(dout10),.co(co10));

counter_6 u2(.clk(clk),.rst_n(rst_n),.en(co10),.dout(dout6),.co(co6));

and u3(co,co10,co6);

assign dout=dout6,dout10;

endmodule

module count60_tb ;

reg clk,rst_n,en ;

wire [7:0] dout ;

wire co ;

always

begin

#1 clk=1'b1 ;

#1 clk=1'b0 ;

end

initial

begin

clk=1'b0 ;

rst_n=1'b1 ;

en=1'b1;

#1 rst_n=1'b0 ;

#1 rst_n=1'b1 ;

end

count60 U1(.clk(clk),.rst_n(rst_n),.en(en),.dout(dout),.co(co));

endmodule

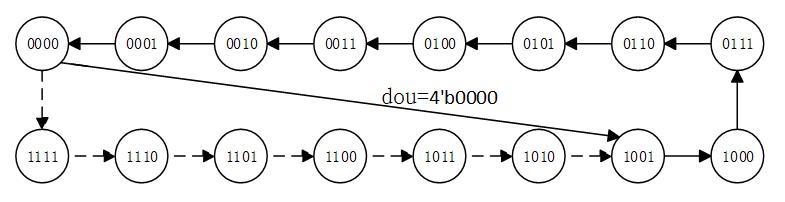

(3)移位计数器

扭环计数器

module twisted_counter(clk,rst_n,dout);

input clk,rst_n;

output[3:0] dout;

reg [3:0] dout;

always @(posedge clk or negedge rst_n)

if(!rst_n) dout<=4'b0000;

else begin

dout<=dout[2:0],~dout[3] ;

endmodule

module twisted_counter_tb;

reg clk,rst_n;

wire [3:0] dout;

always begin

#10 clk=1'b1;

#10 clk=1'b0;

end

initial begin

clk=1'b0;

rst_n=1'b1;

#10 rst_n=1'b0;

#10 rst_n=1'b1;

#100;

end

twisted_counter u1(clk,rst_n,dout);

endmodule

4. 信号产生器

(1)最大循环长度序列码,M=2n。

(2)最长线形序列码(m序列码),M=2n-1。

(3)任意循环长度序列码,M<2n。

(1)状态图类型

有限状态机方式实现001011序列信号产生器

module sequence_signal_fsm(clk,rst_n,dout);

input clk,rst_n;

output dout;

reg dout;

reg [2:0] pre_state,next_state;

parameter s0=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100,s5=3'b101;

always @(posedge clk or negedge rst_n)

if(rst_n ==1'b0)

pre_state<=s0;

else

pre_state<=next_state;

always @(pre_state)

case(pre_state)

s0:

begin

dout<=1'b0;

next_state<=s1;

end

s1:

begin

dout<=1'b0;

next_state<=s2;

end

s2:

begin

dout<=1'b1;

next_state<=s3;

end

s3:

begin

dout<=1'b0;

next_state<=s4;

end

s4:

begin

dout<=1'b1;

next_state<=s5;

end

s5:

begin

dout<=1'b1;

next_state<=s0;

end

default next_state<=s0;

endcase

endmodule

module sequence_signal_fsm_tb;

reg clk,rst_n;

wire dout;

sequence_signal_fsm u1(clk,rst_n,dout);

always #10 clk=~clk;

initial

begin

clk=1'b0;

rst_n=1'b1;

#5 rst_n=1'b0;

#5 rst_n=1'b1;

end

endmodule

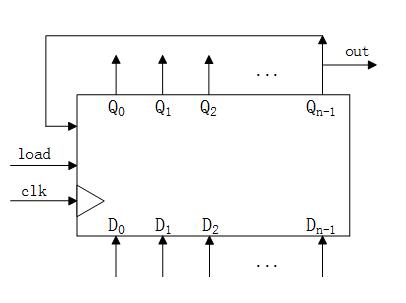

(2)移位寄存器类型

移位寄存器型序列信号产生器

module signal_generator_shifter_reg(clk,rst,din,dout);

input clk,rst;

input [5:0] din;

output dout;

reg dout;

reg [5:0] temp;

always @(posedge clk)

begin

if(rst==1'b1) temp<=din;

else begin

dout<=temp[5];

temp<=temp[4:0],temp[5];

end

end

endmodule

module signal_generator_shifter_reg_tb;

reg clk,rst;

reg [5:0] din;

wire dout;

signal_generator_shifter_reg u1(.clk(clk),.rst(rst),.din(din),.dout(dout));

always #10 clk=~clk以上是关于Verilog学习笔记(06)的主要内容,如果未能解决你的问题,请参考以下文章