CPU的分级缓冲

Posted 雪靡

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了CPU的分级缓冲相关的知识,希望对你有一定的参考价值。

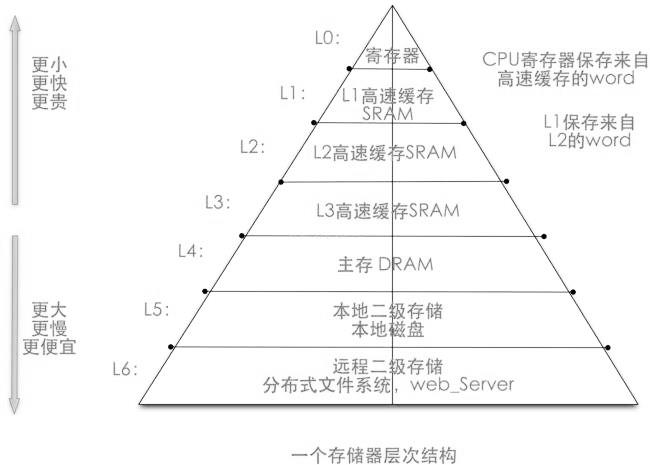

储存层次为:

- L0寄存器

- L1高速缓冲SRAM

- L2高速缓冲SRAM

- L3高速缓冲SRAM

- 主存DRAM

- 本地二级储存 本地磁盘

- 远程二级存储 分布式文件系统,web_server

深入理解处理器高速缓存的工作机制 - snsart - 博客园 https://www.cnblogs.com/snsart/p/10700599.html

CPU多级缓存 - 知乎 https://zhuanlan.zhihu.com/p/40381275

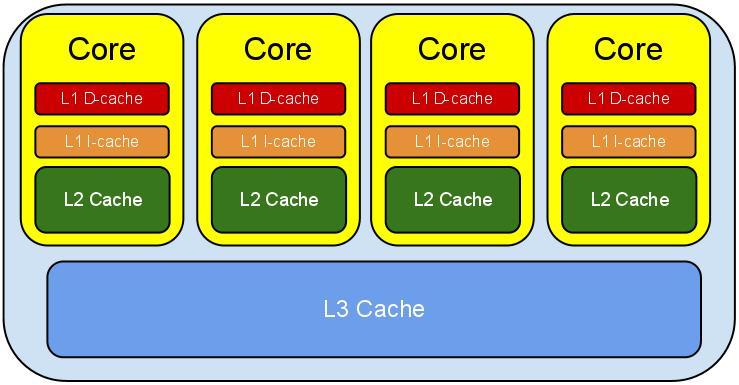

CPU多级缓存架构-现代CPU多级缓存

高速缓存L1、L2、L3

3级是所有cpu共享的,2级是独有的,1级是在独有的基础上,分为数据缓存和指令缓存。

下面是三级缓存的处理速度参考表:

| 从CPU到 | 大约需要的CPU周期 | 大约需要的时间(单位ns) |

|---|---|---|

| 寄存器 | 1 cycle | |

| L1 Cache | ~3-4 cycles | ~0.5-1 ns |

| L2 Cache | ~10-20 cycles | ~3-7 ns |

| L3 Cache | ~40-45 cycles | ~15 ns |

| 跨槽传输 | ~20 ns | |

| 内存 | ~120-240 cycles | ~60-120ns |

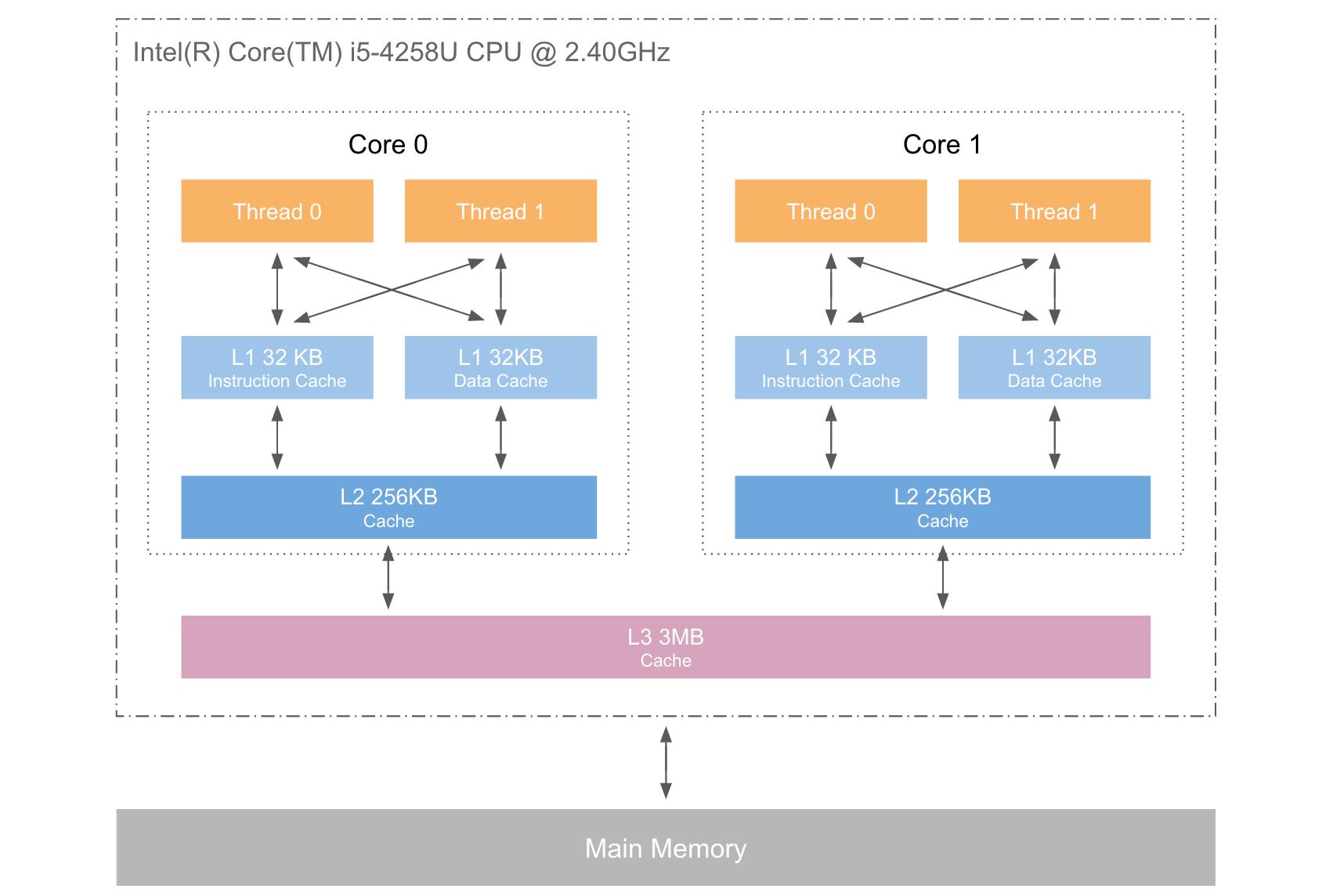

下图是Intel Core i5-4285U的CPU三级缓存示意图:

CPU多级缓存 | 闪烁之狐 https://blinkfox.github.io/2018/11/18/ruan-jian-gong-ju/cpu-duo-ji-huan-cun/

以上是关于CPU的分级缓冲的主要内容,如果未能解决你的问题,请参考以下文章