医院呼叫系统基于FPGA的简易医院呼叫系统实现

Posted fpga和matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了医院呼叫系统基于FPGA的简易医院呼叫系统实现相关的知识,希望对你有一定的参考价值。

1.软件版本

quartusii12.1

2.系统设计概述

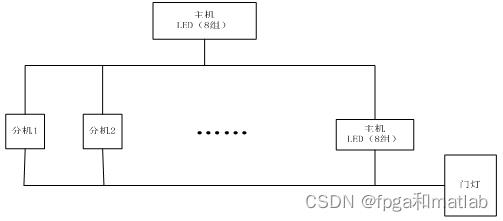

设计一个FPGA对LED进行静态和动态显示的数字时钟控制NBW-8路主机可接8个分机的系统。根据系统设计要求,系统的组成如框图,包括主机FPGA对LED进行静态和动态显示的数字时钟控制程序,以及各个分机电路模板。

系统具有以下功能:

1.主机有LED显示:主机采用显示屏,可显示护理级别,系统状态。主机面板有16/8个双色LED指示灯,可显示每个分机的工作状态。

2.不间断呼叫:主机可显示多路分机的呼叫,并记忆保持。

3.二级护理:可在主机上设计护理级别,有高级和普通二种护理级别。

4.并机功能:主机有并功能,同一台主机可并多台主机,实现多极管理。

5.各分机与门灯连接。

系统包括LED显示屏电路模板,路选分机开关,路选分机指示灯等。接好线再检查确保无误后,打开主机电源,主机自动进入对分机的检查状态,主机从1号机开始检测:分机正常显示等闪亮一下,如某路分机有故障或该路未接分机,则相应的路选指示灯亮绿色保持,对全部的16/8路分机检测,检测完毕后,保持亮绿色的指示灯5秒再熄灭。检测完毕,主机自动回到待机状态。

主机采用FPGA对LED进行静态和动态显示的数字时钟控制程序,和所有分机相连接。分机只需一条两芯总线和主机上的端口相连,可按手持呼叫器上的CALL键或分机上的呼叫/解除键呼叫主机。门灯一般安装在该病房门外,以便于走廊中的护士观察;病床呼叫护士站时,该病房的门灯闪亮。病床解除呼叫或护士对讲时,该病房门外的等熄灭。

系统设计要求:设计一个FPGA对LED进行静态和动态显示的数字时钟控制NBW-8路主机可接8个分机的系统,具有以下功能:

1.主机有LED显示:主机采用显示屏,可显示护理级别,系统状态。主机面板有16/8个双色LED指示灯,可显示每个分机的工作状态。

2.不间断呼叫:主机可显示多路分机的呼叫,并记忆保持。

3.二级护理:可在主机上设计护理级别,有高级和普通二种护理级别。

4.并机功能:主机有并功能,同一台主机可并多台主机,实现多极管理。

5.各分机与门灯连接。

接好线再检查确保无误后,打开主机电源,主机自动进入对分机的检查状态,主机从1号机开始检测:分机正常显示等闪亮一下,如某路分机有故障或该路未接分机,则相应的路选指示灯亮绿色保持,对全部的16/8路分机检测,检测完毕后,保持亮绿色的指示灯5秒再熄灭。检测完毕,主机自动回到待机状态。

3.部分源码

4.1 分机模块设计

由于本课题并没有具体要求设计分机模块,所以在这里我们只设计其基本功能,即当分机出现错误的时候,分机像主机发出信号,告诉主机某个分机发生错误。其主要代码如下:

input clk;

input rst;

input in;

output out;

reg out;

always @(posedge clk or negedge rst)

begin

if(!rst)

out<=1'b0;

else out<=in;

end

当我们模拟分机发生错误的时候,只要在输入信号输入一个信号,那么分机就可以像主机发出出错的指令,告诉主机发生错误。改模块比较简单,这里不做具体的介绍了。

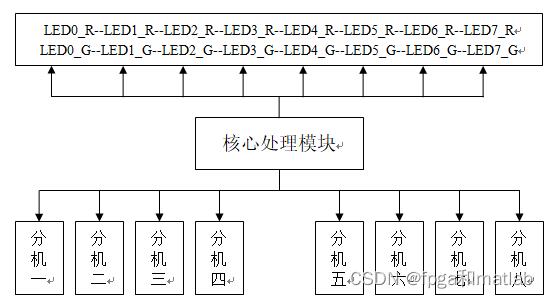

4.2 LDE指示灯设计

本系统LED设计采用红绿双LED显示模式,当用户发出求救信号的时候,那么在显示端红色LED显示,说明某个分机发出求救信号,而当某个分机发生错误的时候,则绿色LED亮,告诉总机某个分机发生错误。

其中用户请求显示模块设计如下:

always @(posedge clk or negedge rst)

begin

if(!rst)

begin

led_red<=1'b0;

end

else begin

if(require==1'b1) //接收到一个请求信号

led_red<=1'b0; //红灯亮,说明有请求信号

else

led_red<=1'b1; //红灯不亮,说明没有请求信号

end

end

当求救信号require发出信号的时候,红色LED信号led_red变低电平,说明某个分机有求救信号。而没有require信号的时候,则led_red信号不显示。

显示分机状态的模块设计如下:

else if(en==1'b1)

begin

if(end_check==1'b0)

begin

if(led_flag==1'b0)led_green<=1'b0;

else

led_green<=1'b0;

end

else begin

if(led_flag==1'b0)led_green<=1'b1;

else

led_green<=1'b0;

end

end

else if(en==1'b0)

begin

if(end_check==1'b0)

begin

if(led_flag==1'b0)led_green<=1'b1;

else

led_green<=1'b0;

end

else begin

if(led_flag==1'b0)led_green<=1'b1;

else

led_green<=1'b0;

end

end

在这个程序段中有很多信号在之前没有具体讨论过,我们将在最后的核心控制模块中介绍,这里仅仅介绍led_green的情况,当主机扫描到某个分机的时候,如果分机正确,那么在扫描这个分机的时候,绿色LED则亮一下,说明这个分机是正确的,如果分机出现错误,那么这个绿色LED将一直亮下去,知道总机完成所有的分机扫描才熄灭。

4.3 总控制器设计

首先要接收八个分机的错误使能信号,具体设计如下,我们只要调用分机模块就可以了:

fenji fenji_u0(

.clk (clk),

.rst (rst),

.in (err[0]),

.out (err_signal[0])

);

…………………………

fenji fenji_u7(

.clk (clk),

.rst (rst),

.in (err[7]),

.out (err_signal[7])

);

通过以上的程序,我们可以得到来自分机的错误使能信号。

下面介绍总控制器是如何工作的,具体的代码如下:

case(cnt)

4'b0001:begin

if(err_signal[0]==1'b1)

begin flag[0]<=1'b0;flag[7:1]<=flag[7:1];end//have no problem

else

begin flag[0]<=1'b1;flag[7:1]<=flag[7:1];end//have some problem

end

……………………………

4'b1000:begin

if(err_signal[7]==1'b1)

begin flag[7]<=1'b0;end//have no problem

else

begin flag[7]<=1'b1;end//have some problem

end

default:flag<=flag;

endcase

即当总机接收到错误信号的时候,总机像显示模块发送错误控制信号flag.信号flag是一个8位的并行信号,其每一位信号对应控制着每一个显示模块信号。

剩下的就是系统显示模块,比较简单,这里就不做介绍了。

4.仿真结论

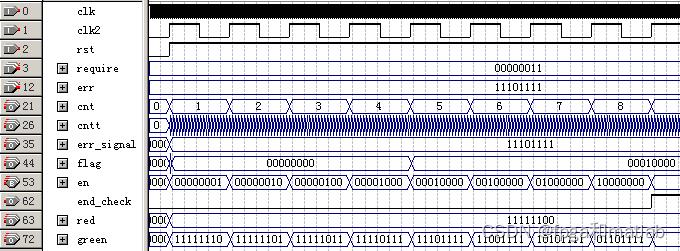

图2 系统仿真图1

从上面的图我们可以看到,我们模拟分机五发生错误,那么对应的FALG信号将将在主机扫描到第五个分机的时候,FLGA[4]的值变为1,说明分机五发生错误,在总机的显示段,绿色LED将一直显示下去,而其他的LED则仅仅在扫描对应分机的时候才亮。

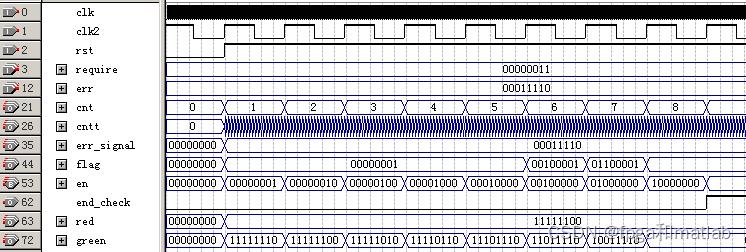

图3系统仿真图2

这里再给出另一张系统仿真图,当多个分机发生错误的时候,我们发现对应的绿色LED也做出正确的判别,可见系统是正确的。

当分机系统发出错误使能信号的时候,当总机检测到错误信号的时候,如果分机发出了错误使能信号err_signal的时候,flag[0]信号则发出0,而其他位的信号保持不变:flag[7:1]<=flag[7:1]。如果没有检测到错误使能信号err_signal,则flag[0]信号则发出1,而其他位的信号保持不变:flag[7:1]<=flag[7:1]。扫描完第一个分机后再扫描后面的分机,具体工作原理相同。

当扫描完所有的分机以后,发出end_check信号,说明总机已经完成了所有的分机扫描工作。

以上就是基于FPGA的医疗呼叫系统的主要模块实现。A02-30

以上是关于医院呼叫系统基于FPGA的简易医院呼叫系统实现的主要内容,如果未能解决你的问题,请参考以下文章