verilog作业

Posted 揭航

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了verilog作业相关的知识,希望对你有一定的参考价值。

verilog作业

2020-5-30

1.按键

采用硬件描述语言(Verilog HDL),设计4个独立按键的按键检测电路,在数码管上显示优先级最高按键的键值。要求:无键按下时,数码管不显示(灭掉)。……具体代码如下,试补充完空白处的代码。

module My_key_Display(Key_In,Seg_out,Led_out);

input [3:0] Key_In; // 按键输入

output reg [3:0] Led_out; //LED显示

output reg __________; // 数码管显示

wire [1:0] Key_Value; // 键值编码变量

wire En_out; // 按键标记变量

assign Key_Value[1]=~ Key_In[3]| Key_In[3]&(~ Key_In[2]);

assign Key_Value[0]=~ Key_In[3]| Key_In[3]& Key_In[2]&(~ Key_In[1]);

assign En_out =~(Key_In[3]& Key_In[2]& Key_In[1]& Key_In[0]);

always @(Key_Value)

begin

if(En_out)

begin

case(______________)

2'b00: begin Led_out=4'b0001; Seg_out=7'b0000001; end

2'b01: begin Led_out=4'b0010; Seg_out=7'b1001111; end

2'b10: begin Led_out=4'b0100; Seg_out=7'b0010010; end

2'b11: begin Led_out=4'b_____; Seg_out=7'b0000110; end

endcase

end

else

begin

Led_out=4'b0000;

Seg_out=7'b1111111;

end

end

endmodule

// 采用硬件描述语言(Verilog HDL),设计4个独立按键的按键检测电路,

// 在数码管上显示优先级最高按键的键值。

// 要求:无键按下时,数码管不显示(灭掉)。……具体代码如下,试补充完空白处的代码。

module My_key_Display(Key_In,Seg_out,Led_out);

input [3:0] Key_In; // 按键输入

output reg [3:0] Led_out; //LED显示

output reg Seg_out; // 数码管显示

wire [1:0] Key_Value; // 键值编码变量

wire En_out; // 按键标记变量

assign Key_Value[1]=~ Key_In[3]| Key_In[3]&(~ Key_In[2]);

assign Key_Value[0]=~ Key_In[3]| Key_In[3]& Key_In[2]&(~ Key_In[1]);

assign En_out =~(Key_In[3]& Key_In[2]& Key_In[1]& Key_In[0]);

always @(Key_Value)

begin

if(En_out)

begin

case(Key_Value)

2'b00:

begin

Led_out=4'b0001;

Seg_out=7'b0000001;

end

2'b01:

begin

Led_out=4'b0010;

Seg_out=7'b1001111;

end

2'b10:

begin

Led_out=4'b0100;

Seg_out=7'b0010010;

end

2'b11:

begin

Led_out=4'b1000;

Seg_out=7'b0000110;

end

endcase

end

else

begin

Led_out=4'b0000;

Seg_out=7'b1111111;

end

end

endmodule

2.七段显示译码器

采用Verilog HDL代码描述某BCD–七段显示译码器,代码如下,试补充完空白处代码。

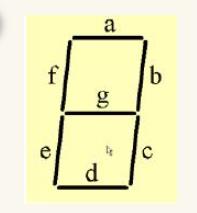

7段数码管是利用不同发光段组合的方式来显示不同的数码,为了试数码管能将数码所代表的数显示出来,必须将数码经译码器译出,然后经驱动器点亮对用的段。结构图如下图1.1。 比如要显示数值5,须将a, f, g, c, d各段点亮。

module My_7Seg_Display(In_Data,En,Seg_out);

input ______________ ;

input En;

output __________________; //七段显示译码器输出端

always @(En, In_Data)

begin

if (En)

begin

case(_____________)

4'd0:

Seg_out=7'b__________;

4'd1:

Seg_out=7'b1111001;

4'd2:

Seg_out=7'b0100100;

4'd3:

Seg_out=7'b0110000;

4'd4:

Seg_out=7'b0011001;

4'd5:

Seg_out=7'b0010010;

4'd6:

Seg_out=7'b0000011;

4'd7:

Seg_out=7'b1111000;

4'd8:

Seg_out=7'b0000000;

4'd9:

Seg_out=7'b0011000;

default:

Seg_out=7'b1111111;

endcase

end

else

Seg_out=_________________;

end

endmodule

上面显示的是_____共阳__ 类型的七段显示译码器?(填写:共阴或者共阳)

// 采用Verilog HDL代码描述某BCD--七段显示译码器,代码如下,试补充完空白处代码。

module My_7Seg_Display(In_Data,En,Seg_out);

input In_Data ;

input En;

output Seg_out; //七段显示译码器输出端

always @(En, In_Data)

begin

if (En)

begin

case(In_Data)

4'd0:

Seg_out=7'b1000000;

4'd1:

Seg_out=7'b1111001;

4'd2:

Seg_out=7'b0100100;

4'd3:

Seg_out=7'b0110000;

4'd4:

Seg_out=7'b0011001;

4'd5:

Seg_out=7'b0010010;

4'd6:

Seg_out=7'b0000011;

4'd7:

Seg_out=7'b1111000;

4'd8:

Seg_out=7'b0000000;

4'd9:

Seg_out=7'b0011000;

default:

Seg_out=7'b1111111;

endcase

end

else

Seg_out=7'b1111111;

end

endmodule

3.序列信号发生器

某序列信号发生器的电路符号如下图所示,对应的Verilog HDL代码如下,试补充完空白处代码。

// 某序列信号发生器的电路符号如下图所示,对应的Verilog HDL代码如下,试补充完空白处代码。

module xl_generate(dout, clk, clr);

output dout;

input clk, clr;

_______________;

reg [7:0] q;

always @(posedge clk)

begin

if(clr)

begin

dout<=0;

q<=8'b10110101;

end

else

begin

dout<=q[7];

q<=q[6:0],________;

end

end

endmodule

// 某序列信号发生器的电路符号如下图所示,对应的Verilog HDL代码如下,试补充完空白处代码。

module xl_generate(dout, clk, clr);

output dout;

input clk, clr;

reg dout;

reg [7:0] q;

always @(posedge clk)

begin

if(clr)

begin

dout<=0;

q<=8'b10110101;

end

else

begin

dout<=q[7];

q<=q[6:0],q[7];

end

end

endmodule

4.分频器

采用Verilog,设计一个分频器,将50MHz时钟分频得到占空比为50%的2Hz时钟。试补充完空白处代码。

module Counter_50MHz(clk_in,clk_out);

input clk_in;

output reg clk_out;

reg [25:0] count;

parameter N=26'd25000000;

always @(posedge _______)

begin

if(count==N/2-1)

begin

clk_out=_________;

count<=0;

end

else

begin

count<=_________;

end

end

endmodule

module Counter_50MHz(clk_in,clk_out);

input clk_in;

output reg clk_out;

reg [25:0] count;

parameter N=26'd25000000;

always @(posedge clk_in)

begin

if(count==N/2-1)

begin

clk_out=~clk_out;

count<=0;

end

else

begin

count<=count+1;

end

end

endmodule

5.可变计数器

下面为某可变计数器的Verilog HDL代码,当A=1时,为7进制;当A=0时,为9进制。试补充完空白处代码。

module Alterable_Counter(A, clk, Q);

input clk, A;

output reg [3:0] Q;

parameter N=7;

parameter M=9;

always @(posedge clk)

begin

if(A)

begin

if (__________)

begin

Q<=0;

end

else

begin

Q<=_______;

end

end

else

begin

if (___________)

begin

Q<=0;

end

else

begin

Q<=Q+1;

end

end

end

endmodule

module Alterable_Counter(A, clk, Q);

input clk, A;

output reg [3:0] Q;

parameter N=7;

parameter M=9;

always @(posedge clk)

begin

if(A)

begin

if (Q==N-1)

begin

Q<=0;

end

else

begin

Q<=Q+1;

end

end

else

begin

if (Q==M-1)

begin

Q<=0;

end

else

begin

Q<=Q+1;

end

end

end

endmodule

6.等级判别电路

采用Verilog,设计产品等级判别电路。要求:某产品有三项指标。现规定,当3项指标全部达标为一等品;当A达标,而B和C仅有一项达标为二等品;当A不达标,B和C同时达标为三等品。具体代码如下,试补充完空白处的代码。(注意字母都是大写的)

module Product_detector(A,B,C,F1,F2,F3);

input A,B,C;

output F1,F2,F3;

assign F1=_______________;

assign F2=_______________;

assign F3=_______________;

endmodule

module Product_detector(A,B,C,F1,F2,F3);

input A,B,C;

output F1,F2,F3;

assign F1=A&B&C;

assign F2=~A&B&C;

assign F3=(A&~B&C)|(A&B&~C);

endmodule

以上是关于verilog作业的主要内容,如果未能解决你的问题,请参考以下文章