异部时钟电路的FPGA设计

Posted fpga&matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了异部时钟电路的FPGA设计相关的知识,希望对你有一定的参考价值。

整体系统结构如下图所示:

这个设计的输入输出信号如下

input req_in – 输入请求信号 1bit

input addr_input – 输入地址信号 7bits

input clear – 输入clear信号,清除req_out

inputreset – reset信号

output ack_in – 完成8个神经元计算就产生ack信号

output req_out – 如果有计算大于2的结果,则产生Req_out

output addr_output – 输出计算结果大于2的寄存器编号(0,1,2,3,4,5,6,7)

最终跑完simulation, synthesis, implementation,memory选择DATA_WIDTH = 8, MEM_DEPTH =8192, 就是13位地址位是(7bit addr_input +6bit寄存器编号(0,1,2,3,4,5,6,7))。

输入信号是1K~1MHz的6bit地址数据和1bit req_in,两个同时送到。

得到地址后Memory输出存储好的权重,和对应的8个神经元依次(其实就是寄存器值)相加,得到的数如果大于2就清零这个寄存器,并产生1个Req信号,如果不大于2就把数值存入寄存器。

举个例子,如果有1个Req和起始地址数据2,则从MEM提取一个权重数据,提取的地址分别是20,21,22,23,24,25,26,27,每提取到权重数据,就和相应的寄存器值(0,1,2,3,4,5,6,7)相加,如果和大于2则清零相应寄存器值,如果小于等于2就把新的值存入相应的寄存器值。

最终跑完simulation, synthesis, implementation,memory选择DATA_WIDTH = 8, MEM_DEPTH =8192, 就是13位地址位是(7bit addr_input +6bit寄存器编号(0,1,2,3,4,5,6,7))。

输入信号是1K~1MHz的6bit地址数据和1bit req_in,两个同时送到。

得到地址后Memory输出存储好的权重,和对应的8个神经元依次(其实就是寄存器值)相加,得到的数如果大于2就清零这个寄存器,并产生1个Req信号,如果不大于2就把数值存入寄存器。

举个例子,如果有1个Req和起始地址数据2,则从MEM提取一个权重数据,提取的地址分别是20,21,22,23,24,25,26,27,每提取到权重数据,就和相应的寄存器值(0,1,2,3,4,5,6,7)相加,如果和大于2则清零相应寄存器值,如果小于等于2就把新的值存入相应的寄存器值。

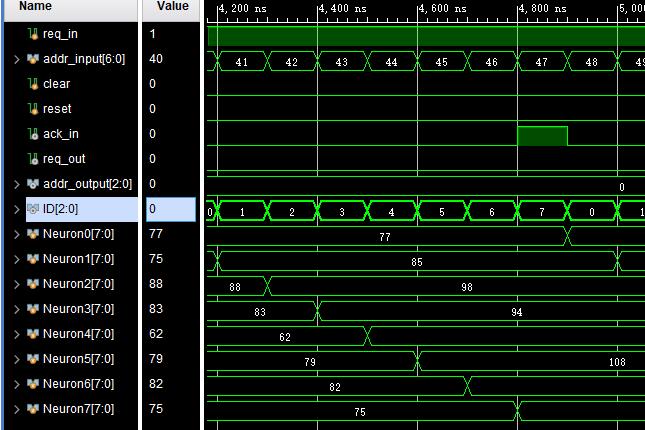

下面对这个功能进行验证:

第一、看clear,当clear=1的时候,reqout就清空,输出始终为0;

第二、放大仿真图,可以看到,当ID=7,即第八个神经元完成计算之后,ackin输出1,表示完成一轮计算。如下图所示。

第三、(这里,假设100为实际的1,200为实际的2)可以看到,当如下图所示,当第3个神经元,其数值为214,即大于2,那么清零,因此后一个值,其清空变为0。之后,第7个神经元为219大于2,那么之后其清零。当出现大于2的情况,reqout会输出一个高电平。。。。。

A42-006

以上是关于异部时钟电路的FPGA设计的主要内容,如果未能解决你的问题,请参考以下文章