[SystemVerilog] MIPS架构下的五级流水线CPU设计

Posted Hellsegamosken

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了[SystemVerilog] MIPS架构下的五级流水线CPU设计相关的知识,希望对你有一定的参考价值。

众所周知,MIPS体系的五级流水线CPU分为五个阶段:取指(IF)、译码(ID)、执行(EX)、存储器(MEM)、写回(WB)。所以这根本算不上“设计”,基本上就是把这个图翻译一遍:

可以发现节点数比较多,为了减少出错(对自己静态调试能力较为自信.jpg),那么程序的框架就显得比较重要了。

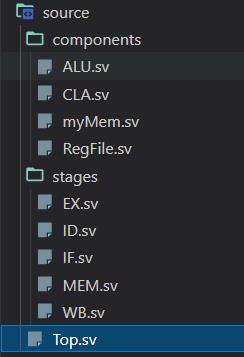

我采用了按阶段划分的方式,每个阶段一个模块,然后ALU、内存、寄存器文件又单列出来,最后在顶层处理模块间的连线,同时完成冲突模块的设计。

这样做的好处是每个模块独立性较强,几十行代码即可解决,静态查错比较方便;模块间连接也比较规范,很好处理。坏处就是一个节点名会敲很多次…

最后代码加起来好像还没有数字钟长?

以上是关于[SystemVerilog] MIPS架构下的五级流水线CPU设计的主要内容,如果未能解决你的问题,请参考以下文章