STM32F4 HAL库开发 -- NVIC 中断优先级管理

Posted 聚优致成

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了STM32F4 HAL库开发 -- NVIC 中断优先级管理相关的知识,希望对你有一定的参考价值。

一、中断寄存器

STM32F429xx的96个中断里面,包括10个内核中断和91个可屏蔽中断,具有16级可编程的中断优先级,而我们常用的就是这91个可屏蔽中断。在MDK内,与NVIC相关的寄存器,MDK为其定义了如下的结构体。

/**

\\brief Structure type to access the Nested Vectored Interrupt Controller (NVIC).

*/

typedef struct

__IOM uint32_t ISER[8U]; /*!< Offset: 0x000 (R/W) Interrupt Set Enable Register */

uint32_t RESERVED0[24U];

__IOM uint32_t ICER[8U]; /*!< Offset: 0x080 (R/W) Interrupt Clear Enable Register */

uint32_t RSERVED1[24U];

__IOM uint32_t ISPR[8U]; /*!< Offset: 0x100 (R/W) Interrupt Set Pending Register */

uint32_t RESERVED2[24U];

__IOM uint32_t ICPR[8U]; /*!< Offset: 0x180 (R/W) Interrupt Clear Pending Register */

uint32_t RESERVED3[24U];

__IOM uint32_t IABR[8U]; /*!< Offset: 0x200 (R/W) Interrupt Active bit Register */

uint32_t RESERVED4[56U];

__IOM uint8_t IP[240U]; /*!< Offset: 0x300 (R/W) Interrupt Priority Register (8Bit wide) */

uint32_t RESERVED5[644U];

__OM uint32_t STIR; /*!< Offset: 0xE00 ( /W) Software Trigger Interrupt Register */

NVIC_Type;

下面重点介绍这几个寄存器:

ISER[8]:

ISER全称是:Interrupt Set-Enable Registers,这是一个中断使能寄存器组。

CM4内核支持256个中断,这里用8个32位寄存器来控制,每个位控制一个中断。但是STM32F429的可屏蔽中断最多只有91个,所以对我们来说,有用的就是三个(ISER[0~2]),总共可以表达96个中断。而STM32F429只用了其中的91个。

ISER[0]的bit0 ~ 31分别对应中断0 ~ 31;ISER[1]的bit0 ~ 32对应中断32 ~ 63;ISER[2]的bit0 ~ 26对应中断64 ~ 90;这样总共91个中断就分别对应上了。你要使能某个中断,必须设置对应的ISER位为1,使该中断被使能(这里仅仅是使能,还要配合中断分组、屏蔽、IO口映射等设置才算是一个完整的中断设置)。

ICER[8]:

ICER全称是:Interrupt Clear-Enable Registers,是一个中断除能寄存器组。该寄存器组与ISER的作用恰恰相反,是用来清除某个中断的使能的。其对应位的功能,也和ISER一样。

这里要专门设置一个ICER来清除中断位,而不是向ISER写0来清除,是因为NVIC的这些寄存器都是写1有效,写0无效的。

ISPR[8]:

ISPR全称是:Interrupt Set-Pending Registers,是一个中断挂起控制寄存器组。每个位对应的中断和ISER是一样的。通过置1,可以将正在进行的中断挂起,而执行同级或更高级别的中断。写0是无效的。

ICPR[8]:

ICPR全称是:Interrupt Clear-Pending Registers,是一个中断解挂控制器组。其作用于ISPR相反,对应位也和ISER是一样的。通过设置1,可以将挂起的中断解挂。写0无效。

IABR[8]:

IABR全称是:Interrupt Active Bit Registers,是一个中断激活标志位寄存器组。对应位所代表的中断和ISER一样,如果为1,则表示该位所对应的中断正在被执行。这是一个只读寄存器,通过它可以知道当前在执行的中断是哪一个。在中断执行完了由硬件自动清零。

IP[240]:

IP全称是:Interrupt Priority Registers,是一个中断优先级控制的寄存器组。

这个寄存器相当重要。STM32F429的中断分组与这个寄存器组密切相关。IP寄存器组有240个8bit的寄存器组成,每个可屏蔽中断占用8bit,这样总共 可以表示240个可屏蔽中断。而STM32F429只用到了其中的91个。IP[90]~IP[0]分别对应中断90 ~ 0。而每个可屏蔽中断占用的8bit并没有全部使用,而是只用了高4位。这4位,又分为抢占优先级和子优先级。抢占优先级在前,子优先级在后。而这两个优先级各占几位又要根据SCB->AIRCR中的中断分组设置来决定。

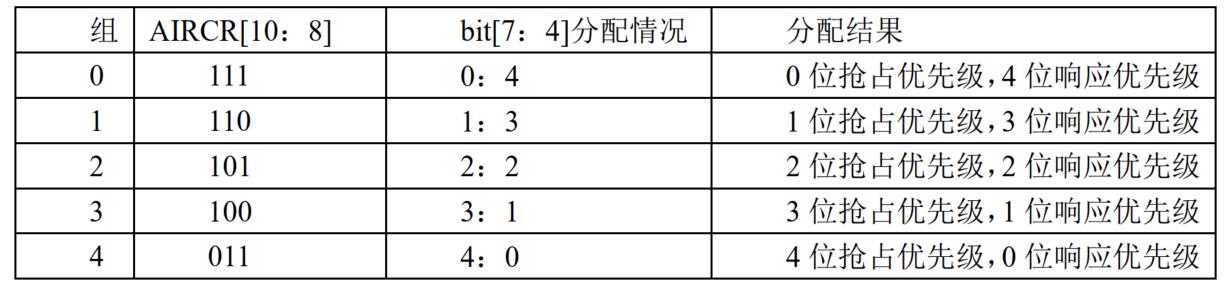

STM32F429的中断分组:STM32F429将中断分为5个组,组0 ~ 4。该分组的设置是由SCR->AIRCR寄存器的bit0 ~ 8来定义的。具体分配关系如下图:

通过这个表,我们就可以清楚的看到组0 ~ 4对应的配置关系,例如组设置为3,那么此时所有的91个中断,每个中断的中断优先级寄存器的高四位中的最高3位是抢占优先级,低1位是响应优先级。每个中断,你可以设置抢占优先级为0 ~ 7,响应优先级为1或0.抢占优先级的级别高于响应优先级的。而数值越小所代表的优先级就越高。

这里需要注意两点:第一,如果两个中断的抢占优先级和响应优先级都是一样的话,则看哪个中断先发生就先执行;第二,高优先级的抢占优先级是可以打断正在进行的低抢占优先级中断的。而抢占优先级相同的中断,高优先级的响应优先级不可以打断低响应优先级的中断。

结合实例说明一下:假定设置中断优先级组为2,然后设置中断3(RTC_WKUP中断)的抢占优先级为2,响应优先级为1.中断6(外部中断0)的抢占优先级为3,响应优先级为0。中断7(外部中断1)的抢占优先级为2,响应优先级为0。那么这3个中断的优先级顺序为:中断7>中断3>中断6。

上面例子中的中断3和中断7都可以打断中断6的中断。而中断7和中断3却不可以相互中断。

二、HAL 库实现以上中断分组设置以及中断优先级管理

NVIC中断管理相关函数主要在HAL库关键文件stm32f4xx_hal_cortex.c 中定义。

1、中断优先级分组函数HAL_NVIC_SetPriorityGrouping

函数声明:void HAL_NVIC_SetPriorityGrouping(uint32_t PriorityGroup);

函数定义:

/**

* @brief Sets the priority grouping field (preemption priority and subpriority)

* using the required unlock sequence.

* @param PriorityGroup The priority grouping bits length.

* This parameter can be one of the following values:

* @arg NVIC_PRIORITYGROUP_0: 0 bits for preemption priority

* 4 bits for subpriority

* @arg NVIC_PRIORITYGROUP_1: 1 bits for preemption priority

* 3 bits for subpriority

* @arg NVIC_PRIORITYGROUP_2: 2 bits for preemption priority

* 2 bits for subpriority

* @arg NVIC_PRIORITYGROUP_3: 3 bits for preemption priority

* 1 bits for subpriority

* @arg NVIC_PRIORITYGROUP_4: 4 bits for preemption priority

* 0 bits for subpriority

* @note When the NVIC_PriorityGroup_0 is selected, IRQ preemption is no more possible.

* The pending IRQ priority will be managed only by the subpriority.

* @retval None

*/

void HAL_NVIC_SetPriorityGrouping(uint32_t PriorityGroup)

/* Check the parameters */

assert_param(IS_NVIC_PRIORITY_GROUP(PriorityGroup));

/* Set the PRIGROUP[10:8] bits according to the PriorityGroup parameter value */

NVIC_SetPriorityGrouping(PriorityGroup);

这个函数的作用是对中断的优先级进行分组,这个函数在系统中只需要被调用一次,一旦分组确定就最好不要更改,否则容易造成程序分组混乱。

从函数体以及注释可以看出,这个函数是通过调用函数NVIC_SetPriorityGrouping来进行中断优先级分组设置。再查看NVIC_SetPriorityGrouping:

/**

\\brief Set Priority Grouping

\\details Sets the priority grouping field using the required unlock sequence.

The parameter PriorityGroup is assigned to the field SCB->AIRCR [10:8] PRIGROUP field.

Only values from 0..7 are used.

In case of a conflict between priority grouping and available

priority bits (__NVIC_PRIO_BITS), the smallest possible priority group is set.

\\param [in] PriorityGroup Priority grouping field.

*/

__STATIC_INLINE void __NVIC_SetPriorityGrouping(uint32_t PriorityGroup)

uint32_t reg_value;

uint32_t PriorityGroupTmp = (PriorityGroup & (uint32_t)0x07UL); /* only values 0..7 are used */

reg_value = SCB->AIRCR; /* read old register configuration */

reg_value &= ~((uint32_t)(SCB_AIRCR_VECTKEY_Msk | SCB_AIRCR_PRIGROUP_Msk)); /* clear bits to change */

reg_value = (reg_value |

((uint32_t)0x5FAUL << SCB_AIRCR_VECTKEY_Pos) |

(PriorityGroupTmp << SCB_AIRCR_PRIGROUP_Pos) ); /* Insert write key and priority group */

SCB->AIRCR = reg_value;

可以看到,函数的最开头有这样一行函数:

assert_param(IS_NVIC_PRIORITY_GROUP(PriorityGroup));

其中函数 assert_param是断言函数,它的作用主要是对入口参数的有效性进行判断。也就是说我们可以通过这个函数知道入口参数在哪些范围内是有效的。

查看IS_NVIC_PRIORITY_GROUP:

#define IS_NVIC_PRIORITY_GROUP(GROUP) (((GROUP) == NVIC_PRIORITYGROUP_0) || \\

((GROUP) == NVIC_PRIORITYGROUP_1) || \\

((GROUP) == NVIC_PRIORITYGROUP_2) || \\

((GROUP) == NVIC_PRIORITYGROUP_3) || \\

((GROUP) == NVIC_PRIORITYGROUP_4))

从这个内容可以看出,当GROUP的值为NVIC_PRIORITYGROUP_0 ~ NVIC_PRIORITYGROUP_4的时候,IS_NVIC_PRIORITY_GROUP的值才为真。这也就是我们上面讲的,分组范围为0~4,对应的入口参数为宏定义值NVIC_PRIORITYGROUP_0 ~ NVIC_PRIORITYGROUP_4。比如我们设置整个系统的中断优先级分组值为2,那么方法是:

HAL_NVIC_SetPriorityGroupin(NVIC_PRIORITYGROUP_2);

这样就确定了中断优先级分组为2,也就是2位抢占优先级,2位响应优先级,抢占优先级和响应优先级的值得范围均为0 ~ 3。

打开stm32f4xx_hal.c 文件可以看到,文件内部定义了HAL库初始化函数HAL_Init,这个函数非常重要,其作用主要是对中断优先级分组,FLASH以及硬件层进行初始化。在HAL_Init内部,有如下一行代码:

HAL_NVIC_SetPriorityGrouping(NVIC_PRIORITYGROUP_4);

这行代码的作用是把系统中断优先级分组设置为分组4,也就是说,在主函数中调用HAL_Init函数之后,在HAL_Init函数内部会通过调用HAL_NVIC_SetPriorityGrouping 函数来进行系统中断优先级分组设置。所以,我们要进行中断分组设置,只需要修改HAL_Init函数内部的这行代码即可。

2、设置抢占优先级和响应优先级

官方 HAL 库文件 stm32f4xx_hal_cortex.c 中定义了三个单个中断优先级设置

函数。函数如下:

//用来设置单个优先级的抢占优先级和响应优先级的值

void HAL_NVIC_SetPriority(IRQn_Type IRQn,uint32_t PreemptPriority, uint32_t SubPriority);

//用来使能某个中断通道

void HAL_NVIC_EnableIRQ(IRQn_Type IRQn);

//用来清除某个中断使能的,也就是中断失能

void HAL_NVIC_DisableIRQ(IRQn_Type IRQn);

这里大家还需要注意,中断优先级分组和中断优先级设置是两个不同的概念。

中断优先级分组是用来设置整个系统对于中断分组设置为哪个分组,分组号为0 ~ 4,设置函数为HAL_NVIC_SetPriorityGrouping,确定了中断优先级分组号,也就确定了系统对于单个中断的抢占优先级和响应优先级设置各占几个位。(NVIC_PRIORITYGROUP_4 为4个抢占优先级,0位响应优先级)。设置好中断优先级分组,确定过了分组号之后,接下来我们就是要对单个优先级进行中断优先级设置。

最后总结一下中断优先级设置的步骤:

(1)系统运行开始的时候设置中断分组。确定组号,也就是确定抢占优先级和响应优先级的分配位数。设置函数为HAL_NVIC_SetPriorityGrouping。对于HAL库,在文件 stm32f4xx_hal.c内部定义函数 HAL_Init 中有调用 HAL_NVIC_PriorityGroupConfig 函数进行相关设置,所以我们只需要修改HAL_Init内部对中断优先级分组设置即可。

(2)设置单个中断的中断优先级别和使能响应中断通道,使用到的函数主要为:

HAL_NVIC_SetPriority 和HAL_NVIC_EnableIRQ。

以上是关于STM32F4 HAL库开发 -- NVIC 中断优先级管理的主要内容,如果未能解决你的问题,请参考以下文章