STM32 ADC采样频率的理解

Posted 果果小师弟

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了STM32 ADC采样频率的理解相关的知识,希望对你有一定的参考价值。

最大采样率

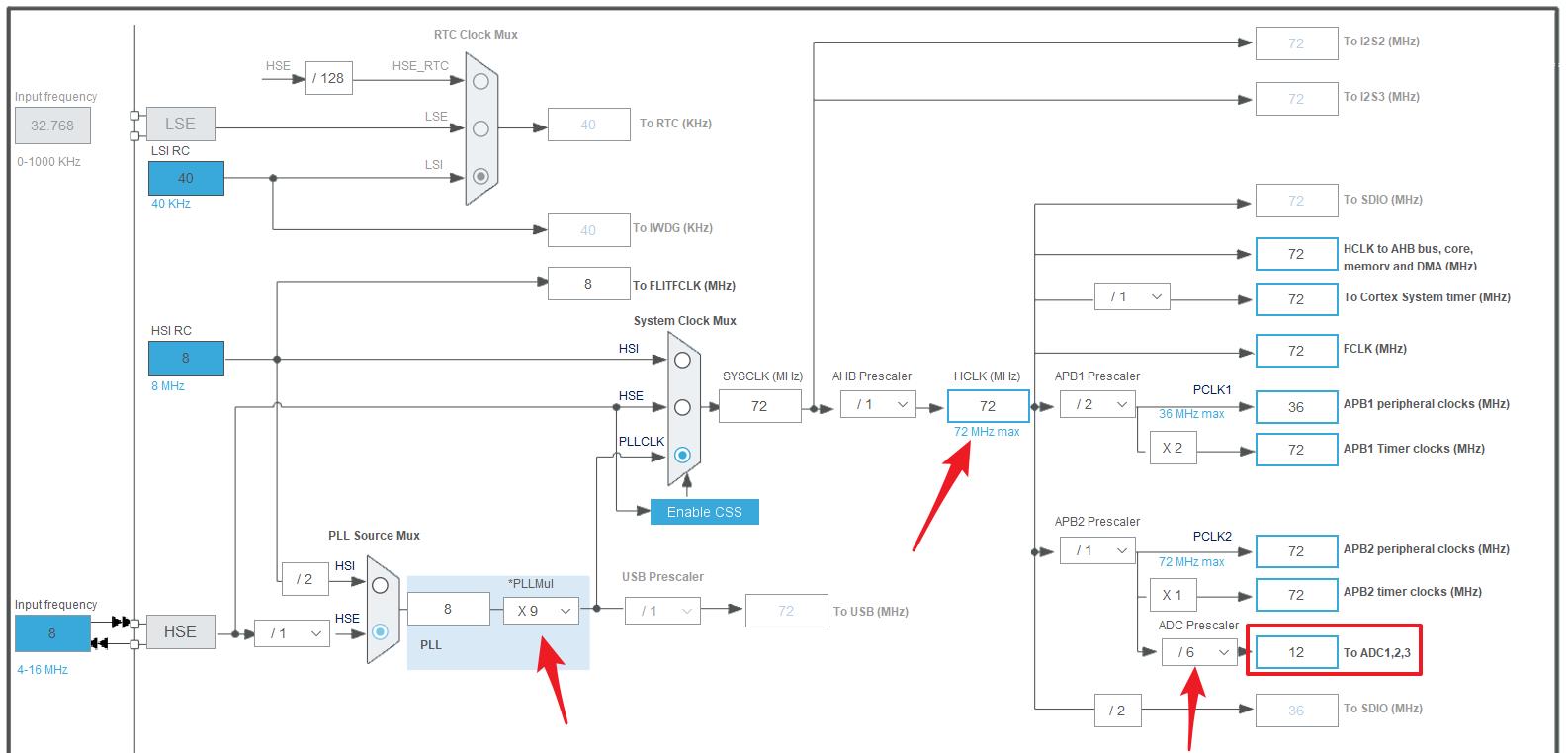

如果设置PLCK2为6分频,那么ADCCLK为:72M/6=12MHz。在外部晶振为8MHZ的情况下,这是F103系列ADC得到的最大时钟频率。

最小采样周期为1.5个周期+12.5周期=14周期。

那么最大采样频率为:12MHZ/14周期=851.142KHZ≈851KHZ

也就是1s可以采样851K个数据,对于STM32F1这个采样率已经是最大能力了。

最小采样率

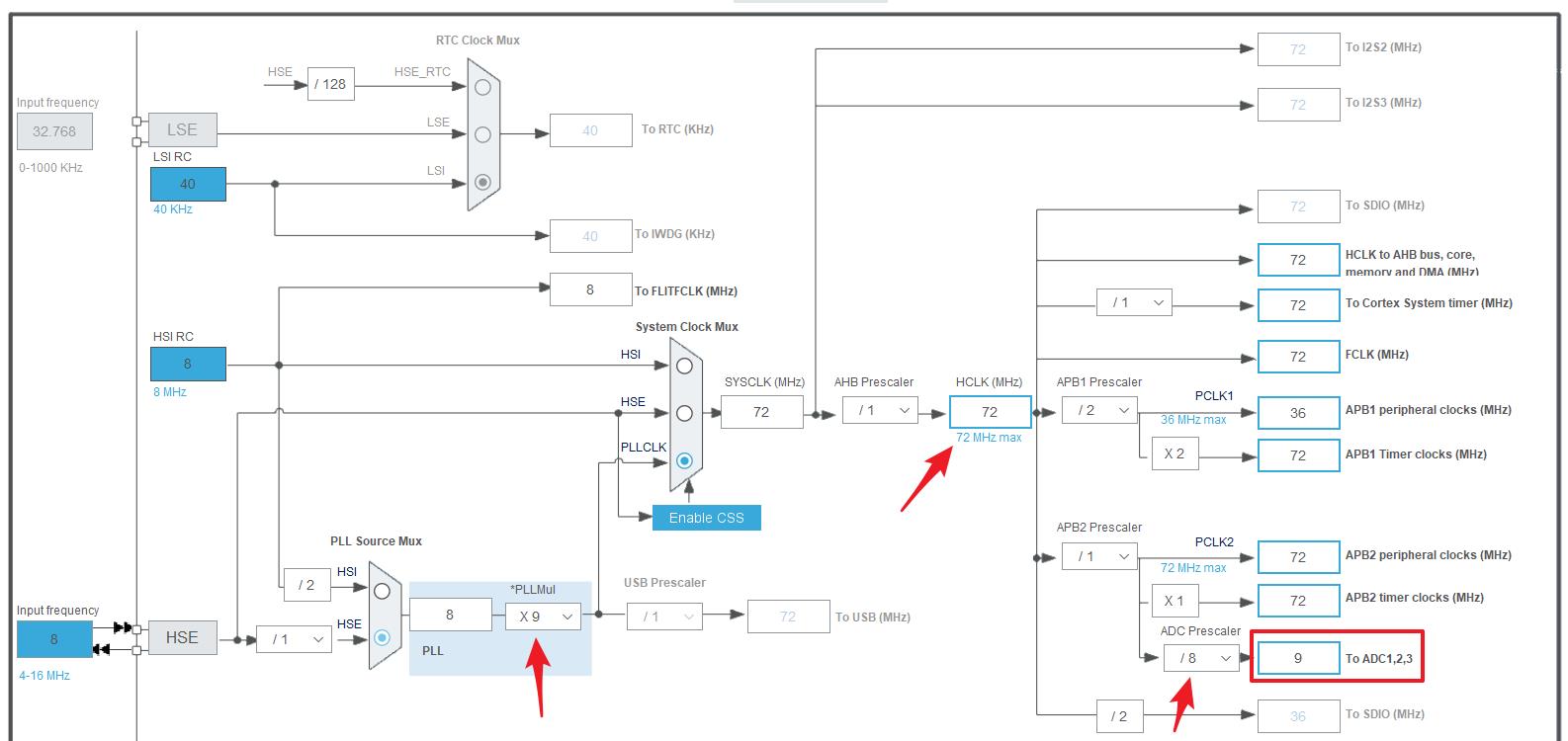

如果设置PLCK2为8分频,那么ADCCLK为:72M/8=9MHz。在外部晶振为8MHZ的情况下,这是F103系列ADC得到的最小时钟频率。

最大采样周期为239.5个周期+12.5周期=252周期。

那么最大采样频率为:9MHZ/252周期=35.714KHZ≈35.7KHZ

也就是1s可以采样35.7K个数据,对于STM32F1这个采样率时其最小的采样能力。

以上是关于STM32 ADC采样频率的理解的主要内容,如果未能解决你的问题,请参考以下文章

虚心求教:stm32使用hal库中adc采样频率如何查看和修改?