面向深度学习的缓存替换算法

Posted xioacd99

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了面向深度学习的缓存替换算法相关的知识,希望对你有一定的参考价值。

这是我的课程论文,写的时候发现针对性的内容很少,因此写完后放出来供大家参考。水平欠佳,劳烦赐教。

公式原来是用 latex 敲的,因为有些语法是扩展的,懒得再和 markdown 折腾了

面向深度学习的缓存替换算法

摘要:本文针对深度学习的落地痛点进行了分析并提出通过改善高速缓存替换算法的方式来提升深度学习的落地能力。具体而言,我们从降低能耗、存储介质材料、降低算法实现难度、综合考虑各级存储、结合机器(深度)学习等方面都进行了详细的分析并给出了几种可行的改进思路。

关键字:缓存;替换算法;深度学习;机器学习

1. 引言

今天的人工智能可以取得如此辉煌的进步,很大程度上要归功于深度学习的蓬勃发展。虽然近几年来深度学习在图像识别、语音处理、机器翻译、智慧城市等领域都取得了一些落地成果,但无比庞大的计算量仍然是深度学习难以得到广泛推广应用的痛点之一。

在高性能计算机系统中,内存性能往往是最为关键的问题之一,其中对高速缓存的改进更是提升内存性能最简单、最经济有效的方法[1]。幸运的是,训练深度学习模型的过程体现了非常强的空间局部性和时间局部性(如对计算机视觉领域的卷积神经网络而言,当核遍历到某个位置时,核周围的数据紧接着就会被访问;自然语言处理领域广泛使用的自注意力机制、长短期网络等都会综合考虑以往访问过的数据),这使得我们可以针对性地对现有的缓存替换算法进行改进,从而有效提高深度学习的落地能力。

2. 降低能耗

2.1 背景

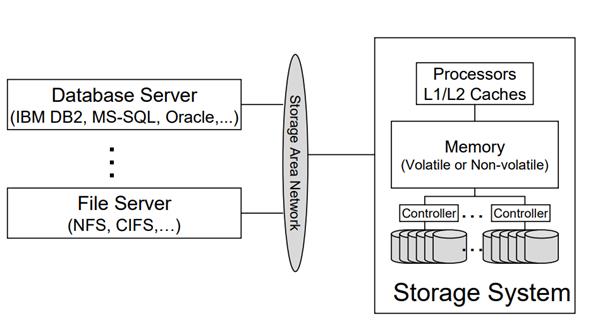

20 年前,一个仅提供数据存储和内容分发的数据中心的电力需求就能以每年 100W/ft2 的速度增长,对应的能源成本几乎以每年 25% 的速率增长[2]。对现代存储体系结构(图 2.1.1)的数据中心而言,存储器几乎是最大的能源消耗,各种开销大约占据了总能源消耗量的 27%[3]。

图 2.1.1 现代存储体系结构

20 年后深度学习蓬勃发展,各类大数据应用层出不穷的今天,存储器市场的需求每年还保持着不低于 60% 的攀升比例[4]。近几年 Google、Microsoft、Nvidia、阿里巴巴、腾讯等互联网公司在深度学习、大数据等领域掀起了一股超巨大模型的风气,仅 2017 年 Google 提出 Transformer 模型到 2021 年短短的 4 年间,深度学习模型的参数大小已经断崖式上涨到了 10 万亿(2021 年 11 月阿里巴巴达摩院以分布式的方式使用 512 张 Nvidia Tesla 训练 10 天得到的超大规模通用性人工智能模型 M6-10T)。

Nvidia 在 2021 年 5 月曾经公布过一个 2.5T 参数大小的模型训练成本,其中仅电力需求就相当于一个小型核电厂的全年发电量。更糟糕的是,存储器性能的提高会导致更高的功率和更多的通信耗费,一个用于信号处理的嵌入式应用程序仅内存通信就耗费了总功率的 50~80%[5]。因此,降低能耗是深度学习发展必须直面的一个关键问题。

2.2 传统方法存在的问题

针对缓存和存储器存在的高能耗问题,传统方法主要有两种解决方式,一种是根据运行情况让存储器在休眠和运行两种状态间切换,另一种是以高计算量为代价对存储器进行动态管理。

采用休眠-运行策略的存储器只能工作在全功率模式下的运行状态,虽然休眠状态下的能耗远低于运行状态,但存储器从休眠状态转变为运行状态时会产生非常大的延迟和能耗[6]。此外,受到传统功率模型的限制,采用休眠-运行策略的存储器访问空闲时间过短,不适应其昂贵的开机、休眠成本[7–10]。

以高计算量为代价的算法通常比较复杂,还需要对每个工作负载进行繁琐的参数调优,难以应用于实际系统。PA-LRU[11]是这类算法中的一个典型例子,它至少有四个参数,每个参数都需要根据当前工作负载、运行情况等进行动态调整,因此很难找到一组适用范围较广的参数。此外,PA-LRU 算法的许多参数与存储器能耗、响应时间等没有直接关系,很难通过对原有算法的扩展来实现自适应参数调优。

2.3 算法方面的改进

对于休眠-运行策略,当下主流的方法是通过引入多级中间态进行动态管理[9,10]。与休眠-运行策略下的全功率模型相比,多级中间态模型能耗更低,不同转速间切换所需的延迟和能耗也远低于全功率模型。遗憾的是,多级中间态模型在硬件实现上还存在一些难题,难以缓解当下的高计算量问题。

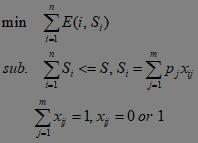

对现实存储系统运行情况的大量统计结果表明,性能最优(命中率最高)的缓存替换算法并非是能耗最优的,存储系统运行过程中各级子系统、各分区的负载也并不服从均匀分布[11]。因此在不影响缓存性能的前提下,可以通过牺牲部分缓存命中率的方式来降低存储器能耗。PB-LRU[6]给出了一种可行的改进思路,它提出针对各级子系统、各级分区设计缓存替换算法来降低整个系统的失效率,进而能量最优问题[11]转换为多重背包问题采用动态规划求解。

假设整个存储系统的大小为 S,首先将整个存储系统划分为 n 个子系统 1…n,再将每个子系统划分为 m 个分区,对应大小 0 < p1 < p2 < …< pm <= S。令 xij 表示子系统 i 是否存在大小为 j 的分区,E(i, s) 为 s 大小的存储器所对应的能耗,整个问题转换为:

由于多重背包是一个 NP-Hard 问题,因此当前还无法在多项式时间复杂度内完成求解。PB-LRU[6]使用动态规划完成了求解,对应状态转移公式如下所示:

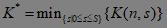

算法中各分区的大小是影响最后结果的一个重要因素,对此 PB-LRU 做了大量仿真实验,得到的最优划分如图 2.3.1 所示

图 2.3.1 PB-LRU 最优分区划分

动态存储器管理的另一个难点在于如何综合功耗、失效率、命中率等各个指标来合理、实时地评估现在的效益。马特森栈算法以跟踪文件的方式来实时确定所有不同大小的缓存的命中率曲线[12,13],但并不能给出不同分区大小下的能耗曲线[6]。PB-LRU 在马特森算法的基础上进行了改进,较好地解决了这一问题,估计值较真实值的误差仅有 1.8%(图 2.3.2),具体步骤如下所示:

图 2.3.2 PB-LRU 改进马特森栈算法的能耗估计结果对比

首先使用马特森栈算法确定不同分区大小的请求是否会导致缓存命中或错过。如果一个请求在大小为 p 及其所有更小的分区中未命中,那么该请求将会访问相应的存储器。当我们知道了对这个存储器的最后访问时间,我们就可以根据底层电源管理方案估计出从最后一次操作到当前操作的能源消耗。如果确定了实际的的功耗管理方案,我们就可以计算空闲期间消耗了多少能量,包括从休眠状态切换到全速状态所需的能量。

在每次更新栈的时候完成下列操作

① 在适当存储器的堆栈中搜索请求的块编号,如果它是堆栈顶部的第 i 个元素,即把它的深度设置为 i;如果没有找到,那么将其深度设置为 ∞。

② 对于所有小于当前深度的分区大小都增加他们的能源消耗估计,并且将之前累计的失效时间合并到当前的访问时间中。

③ 使用与真实缓存相同的替换策略更新堆栈并将请求的块编号带到堆栈的顶部。

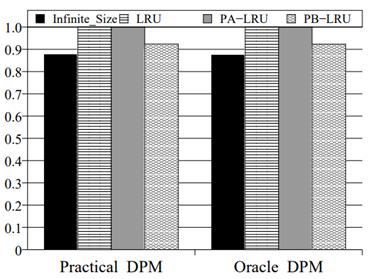

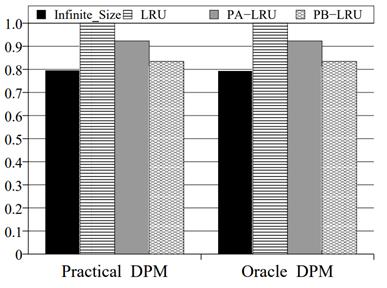

PB-LRU 在不同的基准程序上的实验结果如图 2.3.3 ~ 图 2.3.8 所示

图 2.3.3 能耗对比 (OLTP)

图 2.3.4 能耗对比 (Cello96)

图 2.3.5 能耗对比 (Exponential)

图 2.3.6 能耗对比 (Pareto)

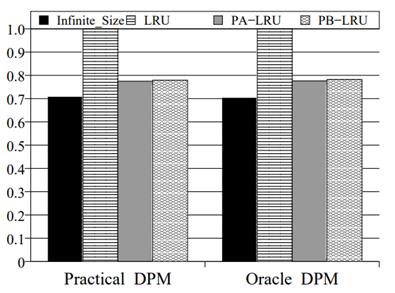

图 2.3.7 平均响应时间 (OLTP and Cello96)

图 2.3.8 平均响应时间 (Synthetic Traces)

2.4 硬件方面的改进

这部分主要针对嵌入式系统、移动终端等微型计算机,它们的能耗模型[14]和数据中心这类数据密集型有所不同,具体如下所示

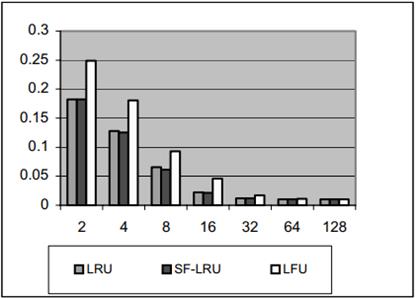

针对这一能耗模型,SF-LRU[15]给出了一个可行的改进思路。SF-LRU 通过引入第二次机会的想法来简化了算法的复杂度并使其易于在硬件上实现,较 LRU 而言,几乎在能耗不变的情况下显著提升了缓存的命中率,图 2.4.1 是 SF-LRU 的一个硬件实现。

图 2.4.1 SF-LRU 算法的一个硬件实现

具体而言,SF-LRU 算法的伪代码如下所示

if (产生访问请求)

if (访问命中)

执行 LRU 算法

更新 RFCV

else

调用失效处理函数

比较 RFCV 的最后两块

if (最后一块 > 倒数第 2 块)

更新 RFCV 的最后一块

交换倒数两块

执行 LRU

SF-LRU 在不同基准程序下的仿真结果如图 2.4.2 ~图 2.4.7 所示

图 2.4.2 32 block size D-cache (CC1)

图 2.4.3 32 block size D-cache for (Pasc)

图 2.4.4 32 block size D-cache for (Spice)

图 2.4.5 8 block size I-cache for (Spice)

图 2.4.6 8 block size I-cache for (CC1)

图 2.4.7 8 block size I-cache for (Pasc)

3. 不同存储介质分别考虑

3.1 闪存

近几十年来缓存替换算法的研究都建立在二级存储由磁盘组成的假设上,但移动终端、嵌入式设备等微型计算机的二级存储主要由闪存构成。多数传统缓存替换算法(LRU 等)是为磁盘存储系统定制的,没有综合考虑到闪存这种材料的特殊性,不利于深度学习的推广落地。

较磁盘而言,闪存在延迟和能耗上有着非对称的读写代价[16](图 3.1.1),在设计替换算法是不仅要考虑命中率,还要考虑“脏”页替换的代价且“脏”页访问时间和能耗均显著高于“干净”页[17]。

图 3.1.1 闪存的读写时间

闪存较磁盘最为特别的一点在于闪存没有寻道时间且数据在被擦除之前不能被覆盖。考虑到闪存的非对称性读写耗费,基于闪存的缓存替换算法应该尽可能减少对闪存的写和擦除操作,同时避免内存缺失导致的大量读操作。

由于闪存不支持就地更新,页被擦除之前不能对同一页进行写入操作。写操作的增加随即会导致擦除操作增加,进而加剧成本不平衡情况。如果考虑闪存写操作伴随的潜在擦除成本,那么写操作的成本可以达到读操作的 8 倍以上。此外,闪存块会在执行指定数量的写/擦除操作后耗尽,因此基于闪存的缓存替换算法还需要精心设计垃圾收集策略来均匀地消耗闪存区域。

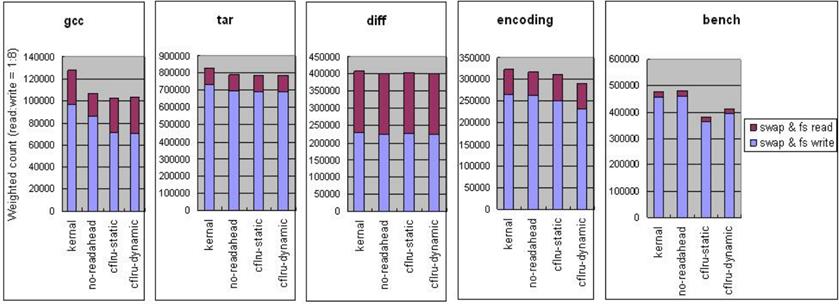

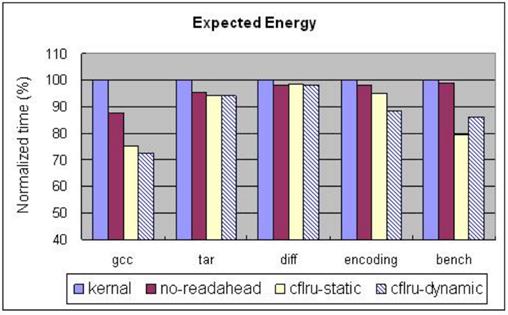

综合考虑这些因素,CFLRU 提出在页面缓存中刻意保留一定数量的“脏”页来减少闪存的写操作次数,同时牺牲部分缓存命中率来提升系统整体性能[17]。具体而言,CFLRU 在传统 LRU 算法的基础上进行改进,首先将 LRU 列表划分为两个区域以寻找一个最小成本点。然后将最近使用的页面组合起来,构成一个工作区域,之后大部分的缓存命中都会发生在这个区域。之后再创建另一个首先清空区域来存放那些可能被驱逐的区域。当发生写操作时,CFLRU 在首先清空区域选择一个“干净”页进行驱逐,从而节省闪存的写开销。如果该区域没有“干净”页,那么就驱逐 LRU 列表末尾的脏页,对应示例如下:

图 3.1.2 CFLRU 算法示例

清除区域(窗口)大小是影响算法实际运行结果的一个重要参数,窗口过大会导致命中率急剧下降。CFLRU 通过大量仿真实验得到了一组适合于各基准程序的参数(图 3.1.3),未来我们可以结合深度学习来降低参数调优的难度。

图 3.1.3 CFLRU 算法窗口大小曲线

CFLRU 在不同基准程序下的实验结果如图 3.1.4 ~ 图 3.1.8 所示

图 3.1.4 CFLRU 在交换系统下的替换成本

图 3.1.5 CFLRU 在文件系统下的替换成本

图 3.1.6 CFLRU 在交换文件系统下的替换成本

图 3.1.7 CFLRU 在各个基准程序下的时间延迟

图 3.1.8 CFLRU 在各个基准程序下的期望能耗

3.2 固态硬盘

随着固态存储技术的飞速发展,基于闪存的固态硬盘在存储系统中所占的比例也在逐年上涨。较传统硬盘而言,固态硬盘性能更高、能耗更低、噪音更小,但由于闪存材料的特殊性,也存在一些缺陷。

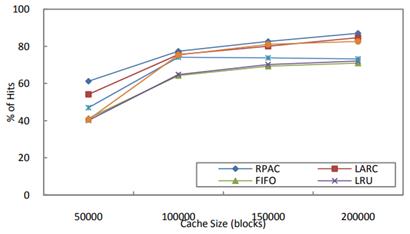

RPAC[18]针对固态硬盘缓存替换算法给出了一个可行的改进思路。现实存储系统存储轨迹[19](图 3.4.1)的分析结果缓存替换算法应该记录由相邻块构成区域的总体受欢迎程度,而不是仅用一个单独的块来考虑是否替换。

图 3.4.1 现实存储系统存储轨迹

基于上述思想,RPAC 提出了一种基于哈希表和二叉树的混合数据结构(图 3.4.2)来维护区域级别的信息。子区域的大小取决于二叉树深度,哈希表用于记录每个统计周期中各区域的访问次数,用于后续区域受欢迎程度的计算。

图 3.4.2 RPAC 用于保持区域信息的数据结构

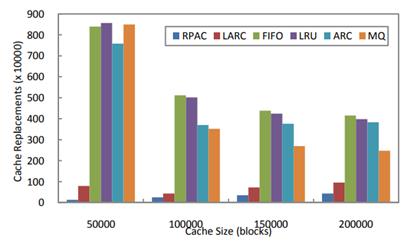

RPAC 算法在不同基准程序上的实验结果如图 3.4.3 ~图 3.4.6 所示:

图 3.4.3 RPAC 在 Mail 上的命中率

图 3.4.4 RPAC 在 Webvm 上的命中率

图 3.4.5 RPAC 在 Mail 上的替换次数

图 3.4.6 RPAC 在 Webvm 上的替换次数

4. 降低算法实现难度

虽然 LRU 类缓存替换算法在性能和能耗方面均有不错的表现,但它需要大量硬件来实时跟踪高速缓存的访问历史。过高的硬件复杂度反过来又会直接影响内存访问时间,进而导致使用 LRU 类算法的高速缓存只能采取相对简单的写策略[1]。

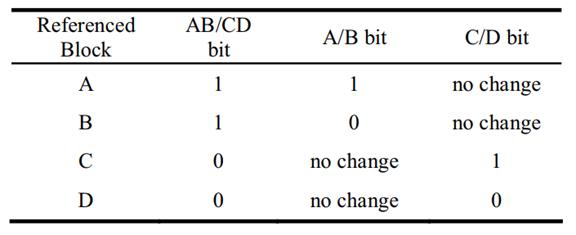

针对这一问题,BPLRU[1]和 MPLRU[1]分别给出了一种降低硬件的可行思路。 BPLRU 使用二叉树(图 4.1)的结构来近似模拟 LRU,访问块 A 或块 B 时, AB/CD 位置为 1;访问块 C 或块 D 时,AB/CD 置为 0。同理,A/B 位用于区分访问对象 A、B 确定访问的对象时块 A 还是块 B。具体替换策略如图 4.2 所示:

图 4.1 BPLRU 使用的二叉树结构

图 4.2 BPLRU 替换策略

然而对 BPLRU 来说,如果待访问的块不在缓存中,那么就会引发失效但历史位并不会改变情况(图 4.3)这意味着 BPLRU 因为缺少足够的迟滞而不能对 LRU 进行很好的模拟,上层二叉树的根节点也忽略了许多下层节点的信息。

图 4.3 BPLRU 的一种性能较差的情况

针对这一问题,MPLRU[1]提出保留节点的前一状态并综合前一状态和当前状态作出替换决定。当发生失效且需要进行替换时,MPLRU 将会使用前面保存的位来作出替换决定。读命中则当前位的值被复制到前一位,当前位则根据当前引用的块进行更新。MPLRU 的运行实例和具体替换策略分别如图 4.4、图 4.5 所示:

图 4.4 MPLRU 运行实例

图 4.5 MPLRU 替换策略

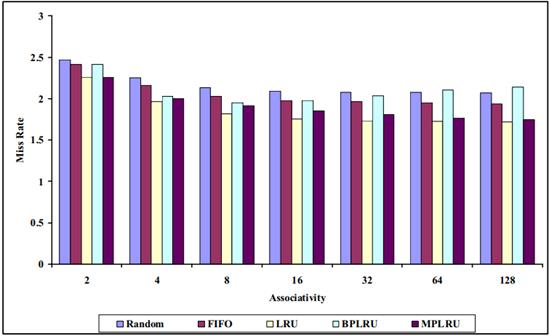

MPLRU 在不同基准程序下的实验结果分别如图 4.6 ~图 4.9 所示:

图 4.6 8KB 下各种算法的失效率对比

图 4.7 16KB 下各种算法的失效率对比

图 4.8 32KB 下各种算法的失效率对比

图 4.9 使用 16 路组相联,不同缓存大小各种算法的失效率对比

考虑 BPLRU 和 MPLRU 用于跟踪访问历史的数据结构过于简单,未来我们可以结合线索二叉树、B+ 树、平衡二叉树、MVCC 等来实现对 LRU 类算法更好的模拟。

5. 综合考虑各级存储

传统缓存替换算法大多建立在一级存储的基础上,没有充分考虑现在的多级缓存情况。现在的高速缓存普遍由 L1 缓存、L2 缓存和 L3 缓存构成,其中 L1 缓存过小,难以体现替换算法的性能优势;L3 缓存较 L2 缓存则过于靠近主存而具有较长延迟中[20],因此考虑多级高速缓存的替换算法应该针对 L2 缓存进行改进。RDP[20]针对 L2 缓存通过引入预测器(图 5.1)和采样器(图 5.2)的硬件部件给出了一种可行的改进思路。

图 5.1 预测器结构

图 5.2 嵌入了采样器的预测器结构示意图

实际部署推广的过程中 RDP 类算法主要会遇到以下 3 点问题:

① 预测器的大小问题。如果考虑 512 个表项,部署对象为 32 位,那么预测器可以仅使用 5 位的桶预测信息和 2 位的饱和计数器,因此预测器的大小为 512*39*(32 + 5 + 2) = 2.5KB。

② 采样问题。按照传统方式,必须通过跟踪许多未验证的预测,等待下一次访问来判断是否匹配才能得到它们的重用距离并将其与 PC 关联起来。这导致我们需要非常大的表来存储地址并需要额外的哈希表来加速预测器的更新操作。对现实存储系统的其他研究表明没有必要收集所有地址的重用距离,随机选择一些地址进行跟踪就有较大规律捕获到可执行程序的内存行为[21,22]。

③ 量化问题。量化方式的好坏会直接影响到最后算法的效果,RDP 在前人[22]的基础上,选择性地选取分区来量化重用距离,这样每个 Cache 行只需要几个额外的位就可以达到较高的量化准确率。

为避免估计访问时间带来的延迟和误差,RDP 综合考虑预测访问时间最大和衰败访问时间最大的两个候选对象,采取完全相同的度量标准来量化访问时间并选择其中最大的进行替换,从而保证了 RDP 算法具有大量关于重用距离的可靠信息,具体实例如图 5.3 所示:

图 5.3 RDP 运行实例示意

RDP 算法在不同基准程序下的实验结果如图 5.4、图 5.5 所示:

图 5.4 RDP 在不同基准程序下降低的失效率

图 5.5 RDP 在不同基准程序下对 IPC 的提升

6. 与机器(深度)学习结合

多数传统缓存替换算法都存在很多问题,FIFO 实现难度低,但当物理内存比较大时就会陷入性能问题;LRU 对于稍大的循环计算会出现严重的性能问题;LFU 和 MFU 等基于频率的算法在内存的不同部分存在不同的频率模式时命中率会急剧下降;LFU 几乎不关注最近访问历史,也不能很好地适应变化的访问模式;MFU 没有考虑最近访问历史,无法区分曾经很热但现在变冷的块和现在很热的块……

在深度学习爆发之前,许多研究已经针对传统缓存替换算法的各种问题做出了相关改进并在特定的情况下取得了不错的结果。LRFU[23]首次综合考虑时近因素和频率实现了 LFU 和 LRU 的结合;ARC[24]结合了 LFU 和 LRU 两者,并在两者间进行动态调整;WRP[25]引入了更多的评价指标来建立基于缓存的页面排名,如出现失效则选择一个排名最低的页面进行替换;LDF[26]在重用距离的基础上,结合范数给出了一种新的评价方式,进而针对缓存替换算法的页面替换进行了改进,降低了页面替换的开销和页面故障率;LRU-K[27]通过监听最近一次使用的比特数来简化硬件实现难度……

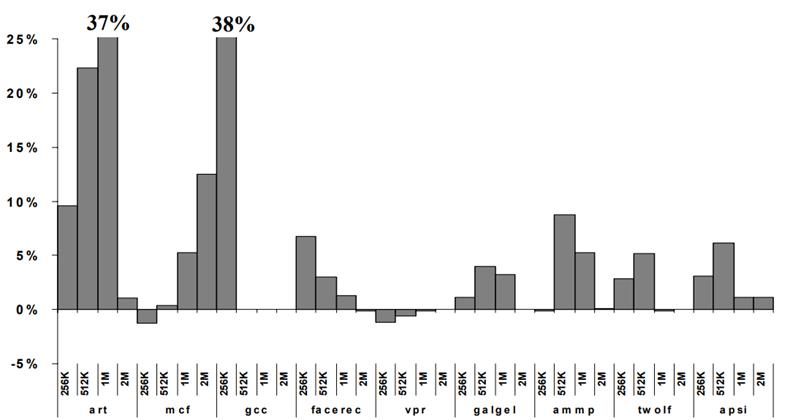

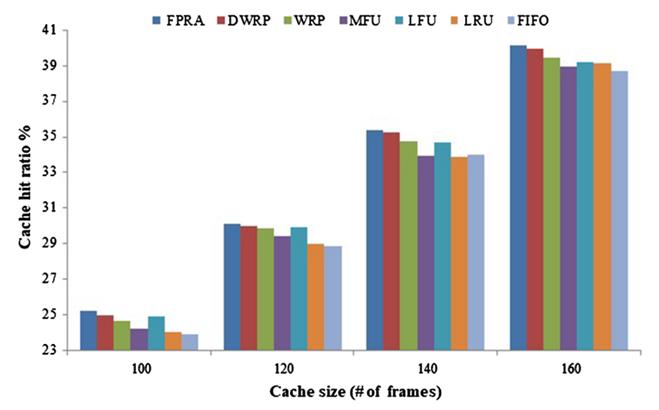

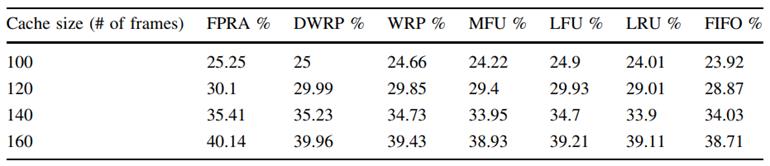

传统缓存替换算法大多的高计算量大多源于参数调优问题,因此考虑和深度学习结合进行改进是一个不错的方向。AWRP[28]首次结合朴素贝叶斯和自适应权重的缓存替换模型,通过动态老化因子与自适应权重排序策略相结合来提高缓存性能,但是并没有取得较传统改进方式让人满意的结果;FPRA[29]通过引入模糊聚类方法中的中心聚类法并结合数据升唯、范数等给出了一种结果较好的改进思路。FRPA 能显著提升内存性能主要源于聚类方法能让同一集合中的页面彼此更加相似,并使得最近、更频繁和更小的引用率页面具有更高的优先级[29],对应实验结果如图 6.1~图 6.4 所示

图 6.1 FRPA 算法命中率对比 (CC1)

图 6.2 FPRA 算法命中率对比 (Spice)

图 6.3 FRPA 算法命中率对比 (CC1)

图 6.4 FPRA 算法命中率对比 (Spice)

7. 结语

在大数据时代下的今天,不只是深度学习,物流、军事、医疗、教育等各行各业都在不断涌现出庞大的计算需求。改进高速缓存替换算法无疑是缓解高计算量问题的有效方式之一。虽然本文针对降低能耗、存储介质材料、降低算法实现难度、综合考虑各级存储、结合机器(深度)学习等很多方面进行了详细的分析探讨并给出了一些可行的思路,但仍然还有很多本文没有考虑到的一些改进方向。

随着总线、体系结构等硬件的发展,应该综合失效率、带宽消耗、命中率等指标来共同评判缓存替换算法的优劣[15];基于闪存的存储器虽然较传统硬盘存储器存在着没有寻道时间、定位时间等诸多优势,但其自身的各种缺陷也导致它只能作为一种过渡阶段的存储介质存在[19];针对特定应用领域改进的缓存替换算法(如 LR-LRU[30]就是一种适用于图像存储和通信的智能缓存替换策略)较通用的缓存替换算法一般能取得更好的应用结果……

8. 参考文献

[1] GHASEMZADEH H, MAZROUEE S, KAKOEE M R. Modified pseudo LRU replacement algorithm[C/OL]//13th Annual IEEE International Symposium and Workshop on Engineering of Computer-Based Systems (ECBS’06). Potsdam, Germany: IEEE, 2006: 6 pp. – 376[2021–10–05]. http://ieeexplore.ieee.org/document/1607387/. DOI:10.1109/ECBS.2006.52.

[2] B M. Taking the data center power and cooling challenge[J]. Energy User News, 2002, 4.

[3] F M. More power needed[J]. Energy User News, 2002.

[4] Power, heat, and sledgehammer[R/OL]. Maximum Institution Inc., 2002. http://www.max-t.com/ downloads/ whitepapers/ SledgehammerPowerHeat20411.pdf.

[5] CHAKRABARTI C. Cache design and exploration for low power embedded systems[C/OL]//Conference Proceedings of the 2001 IEEE International Performance, Computing, and Communications Conference (Cat. No.01CH37210). Phoenix, AZ, USA: IEEE, 2001: 135–139[2021–11–12]. http://ieeexplore.ieee.org/document/918645/. DOI:10.1109/IPCCC.2001.918645.

[6] ZHU Q, SHANKAR A, ZHOU Y. PB-LRU: A Self-Tuning Power Aware Storage Cache Replacement Algorithm for Conserving Disk Energy[C/OL]//Proceedings of the 18th Annual International Conference on Supercomputing - ICS ’04. Malo, France: ACM Press, 2004: 79[2021–10–05]. http://portal.acm.org/citation.cfm?doid=1006209.1006221. DOI:10.1145/1006209.1006221.

[7] GURUMURTHI S, JIANYONG ZHANG, SIVASUBRAMANIAM A, 等. Interplay of energy and performance for disk arrays running transaction processing workloads[C/OL]//2003 IEEE International Symposium on Performance Analysis of Systems and Software. ISPASS 2003. Austin, TX, USA: IEEE, 2003: 123–132[2021–11–13]. http://ieeexplore.ieee.org/document/1190239/. DOI:10.1109/ISPASS.2003.1190239.

[8] PINHEIRO E, BIANCHINI R. Energy Conservation Techniques for Disk Array-Based Servers[C/OL]//Proceedings of the 18th Annual International Conference on Supercomputing - ICS ’04. Malo, France: ACM Press, 2004: 68[2021–11–13]. http://portal.acm.org/citation.cfm?doid=1006209.1006220. DOI:10.1145/1006209.1006220.

[9] GURUMURTHI S, SIVASUBRAMANIAM A, KANDEMIR M, 等. DRPM: Dynamic Speed Control for Power Management in Server Class Disks[C/OL]//Proceedings of the 30th Annual International Symposium on Computer Architecture - ISCA ’03. San Diego, California: ACM Press, 2003: 169[2021–11–13]. http://portal.acm.org/citation.cfm?doid=859618.859638. DOI:10.1145/859618.859638.

[10] CARRERA E V, PINHEIRO E, BIANCHINI R. Conserving Disk Energy in Network Servers[C/OL]//Proceedings of the 17th Annual International Conference on Supercomputing - ICS ’03. San Francisco, CA, USA: ACM Press, 2003: 86[2021–11–13]. http://portal.acm.org/citation.cfm?doid=782814.782829. DOI:10.1145/782814.782829.

[11] QINGBO ZHU, DAVID F M, DEVARAJ C F, 等. Reducing Energy Consumption of Disk Storage Using Power-Aware Cache Management[C/OL]//10th International Symposium on High Performance Computer Architecture (HPCA’04). Madrid, Spain: IEEE, 2004: 118–118[2021–11–13]. http://ieeexplore.ieee.org/document/1410070/. DOI:10.1109/HPCA.2004.10022.

[12] PATTERSON R H, GIBSON G A, GINTING E, 等. Informed Prefetching and Caching[C/OL]//Proceedings of the Fifteenth ACM Symposium on Operating Systems Principles - SOSP ’95. Copper Mountain, Colorado, United States: ACM Press, 1995: 79–95[2021–11–13]. http://portal.acm.org/citation.cfm?doid=224056.224064. DOI:10.1145/224056.224064.

[13] MATTSON R L, GECSEI J, SLUTZ D R, 等. Evaluation techniques for storage hierarchies[J]. IBM Systems Journal, 1970, 9(2): 78–117. DOI:10.1147/sj.92.0078.

[14] SHIUE W-T, CHAKRABARTI C. Memory Exploration for Low Power, Embedded Systems[C/OL]//Proceedings of the 36th ACM/IEEE Conference on Design Automation Conference - DAC ’99. New Orleans, Louisiana, United States: ACM Press, 1999: 140–145[2021–11–12]. http://portal.acm.org/citation.cfm?doid=309847.309902. DOI:10.1145/309847.309902.

[15] ALGHAZO J, AKAABOUNE A, BOTROS N. SF-LRU cache replacement algorithm[C/OL]//Records of the 2004 International Workshop on Memory Technology, Design and Testing, 2004. San Jose, CA, USA: IEEE, 2004: 19–24[2021–10–05]. http://ieeexplore.ieee.org/document/1327979/. DOI:10.1109/MTDT.2004.1327979.

[16] LEE H G, CHANG N. Low-Energy Heterogeneous Non-Volatile Memory Systems for Mobile Systems[J]. Journal of Low Power Electronics, 2005, 1(1): 52–62. DOI:10.1166/jolpe.2005.001.

[17] PARK S, JUNG D, KANG J, 等. CFLRU: A Replacement Algorithm for Flash Memory[C/OL]//Proceedings of the 2006 International Conference on Compilers, Architecture and Synthesis for Embedded Systems - CASES ’06. Seoul, Korea: ACM Press, 2006: 234[2021–10–05]. http://portal.acm.org/citation.cfm?doid=1176760.1176789. DOI:10.1145/1176760.1176789.

[18] FENG YE, CHEN J, XUEJIAO FANG, 等. A Regional Popularity-Aware Cache replacement algorithm to improve the performance and lifetime of SSD-based disk cache[C/OL]//2015 IEEE International Conference on Networking, Architecture and Storage (NAS). Boston, MA, USA: IEEE, 2015: 45–53[2021–10–05]. http://ieeexplore.ieee.org/document/7255203/. DOI:10.1109/NAS.2015.7255203.

[19] HUANG S, WEI Q, CHEN J, 等. Improving flash-based disk cache with Lazy Adaptive Replacement[C/OL]//2013 IEEE 29th Symposium on Mass Storage Systems and Technologies (MSST). Long Beach, CA, USA: IEEE, 2013: 1–10[2021–11–13]. http://ieeexplore.ieee.org/document/6558447/. DOI:10.1109/MSST.2013.6558447.

[20] KERAMIDAS G, PETOUMENOS P, KAXIRAS S. Cache replacement based on reuse-distance prediction[C/OL]//2007 25th International Conference on Computer Design. Lake Tahoe, CA, USA: IEEE, 2007: 245–250[2021–10–05]. http://ieeexplore.ieee.org/document/4601909/. DOI:10.1109/ICCD.2007.4601909.

[21] BERG E, HAGERSTEN E. Fast Data-Locality Profiling of Native Execution[C/OL]//Proceedings of the 2005 ACM SIGMETRICS International Conference on Measurement and Modeling of Computer Systems - SIGMETRICS ’05. Banff, Alberta, Canada: ACM Press, 2005: 169[2021–11–13]. http://portal.acm.org/citation.cfm?doid=1064212.1064232. DOI:10.1145/1064212.1064232.

[22] PETOUMENOS P, KERAMIDAS G, ZEFFER H, 等. Modeling Cache Sharing on Chip Multiprocessor Architectures[C/OL]//2006 IEEE International Symposium on Workload Characterization. San Jose, CA, USA: IEEE, 2006: 160–171[2021–11–13]. http://ieeexplore.ieee.org/document/4086144/. DOI:10.1109/IISWC.2006.302740.

[23] CHO S, MOAKAR L A. AUGMENTED FIFO CACHE REPLACEMENT POLICIES FOR LOW-POWER EMBEDDED PROCESSORS[J]. Journal of Circuits, Systems and Computers, 2009, 18(06): 1081–1092. DOI:10.1142/S0218126609005551.

[24] WEI-CHE TSENG, CHUN JASON XUE, QINGFENG ZHUGE, 等. PRR: A low-overhead cache replacement algorithm for embedded processors[C/OL]//17th Asia and South Pacific Design Automation Conference. Sydney, Australia: IEEE, 2012: 35–40[2021–11–13]. http://ieeexplore.ieee.org/document/6164972/. DOI:10.1109/ASPDAC.2012.6164972.

[25] MA T, HAO Y, SHEN W, 等. An Improved Web Cache Replacement Algorithm Based on Weighting and Cost[J]. IEEE Access, 2018, 6: 27010–27017. DOI:10.1109/ACCESS.2018.2829142.

[26] KUMAR G, DEPARTMENT OF INFORMATION TECHNOLOGY, RAJ KUMAR GOEL INSTITUTE OF TECHNOLOGY AND MANAGEMENT, GHAZIABAD – 201001, UTTAR PRADESH, INDIA, TOMAR P, 等. A Novel Longest Distance First Page Replacement Algorithm[J]. Indian Journal of Science and Technology, 2017, 10(30): 1–6. DOI:10.17485/ijst/2017/v10i30/115500.

[27] O’NEIL E J, O’NEIL P E, WEIKUM G. An Optimality Proof of the LRU- K Page Replacement Algorithm[J]. Journal of the ACM, 1999, 46(1): 92–112. DOI:10.1145/300515.300518.

[28] FUNKE OLANREWAJU R, MAHMOUD MOHAMMAD AL-QUDAH D, WONG AZMAN A, 等. Intelligent Web Proxy Cache Replacement Algorithm Based on Adaptive Weight Ranking Policy via Dynamic Aging[J/OL]. Indian Journal of Science and Technology, 2016, 9(36)[2021–11–13]. https://indjst.org/articles/intelligent-web-proxy-cache-replacement-algorithm-based-on-adaptive-weight-ranking-policy-via-dynamic-aging. DOI:10.17485/ijst/2016/v9i36/102159.

[29] AKBARI BENGAR D, EBRAHIMNEJAD A, MOTAMENI H, 等. A Page Replacement Algorithm Based on a Fuzzy Approach to Improve Cache Memory Performance[J]. Soft Computing, 2020, 24(2): 955–963. DOI:10.1007/s00500-019-04624-w.

[30] WANG Y, YANG Y, HAN C, 等. LR-LRU: A PACS-Oriented Intelligent Cache Replacement Policy[J]. IEEE Access, 2019, 7: 58073–58084. DOI:10.1109/ACCESS.2019.2913961.

以上是关于面向深度学习的缓存替换算法的主要内容,如果未能解决你的问题,请参考以下文章