Cadence Allegro铺铜及内电层设计图文及视频演示

Posted fydar

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Cadence Allegro铺铜及内电层设计图文及视频演示相关的知识,希望对你有一定的参考价值。

视频演示:

Allegro内电层设计

内电层是往往是一个完整的地或者电源层,具有很好的屏蔽作用;在高速PCB中,内电层可以有效的隔离各个走线层,以减小各走线层间的串扰。(本文推荐在布局完成后进行内电层的设计)本文简单介绍内电层的设计方法。

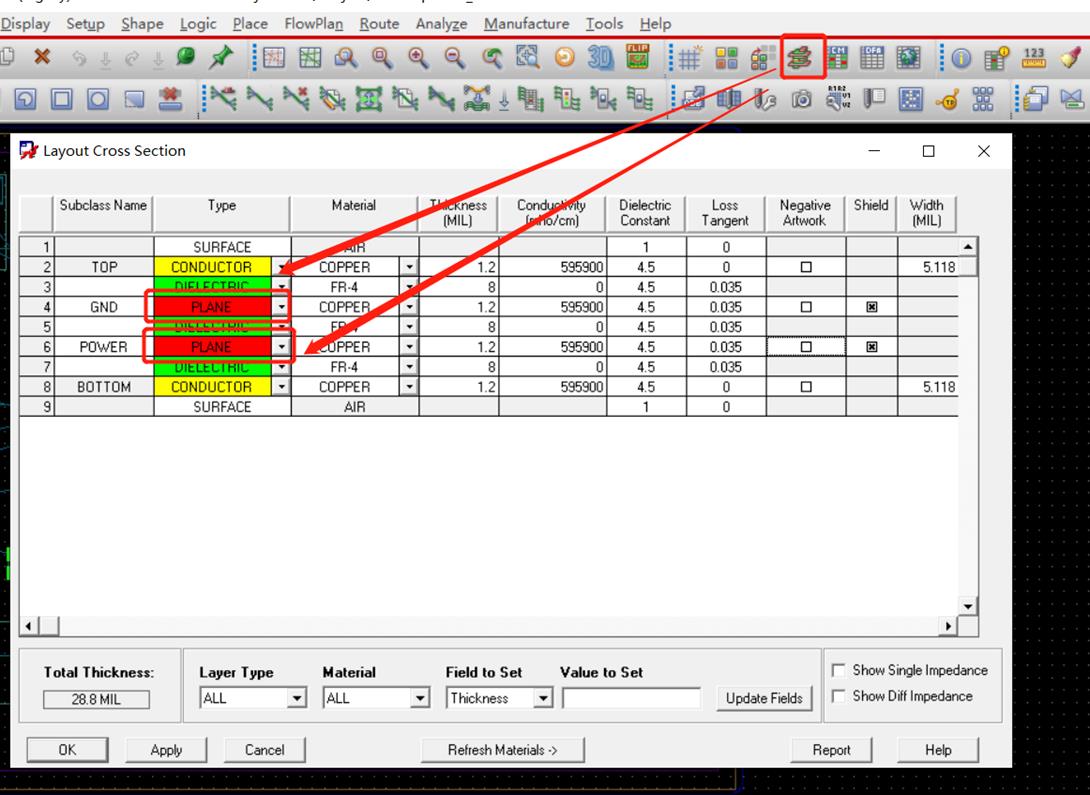

第1步:设置内电层

单击“Xsection”进入“Layout Cross section”窗口,将需要设置为内电层的层的“type”设置成“plane”

第2步:内电层铺铜

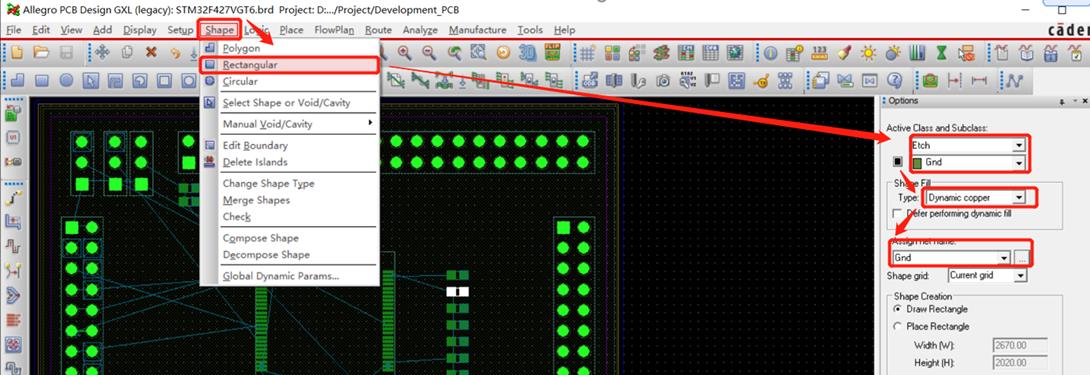

铺铜方法1:铺GND层

执行“shape→Rectangular”然后配置铺“Etch”的“Gnd层”,类型为“Dynamic copper”,Assign net name设置为“gnd”

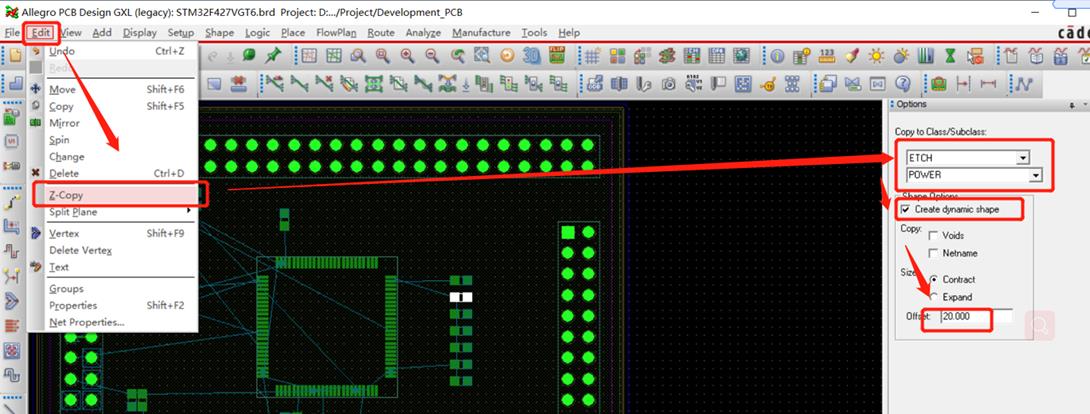

铺铜方法2:铺POWER层

执行“Edit→Z-Copy” 然后配置铺“Etch”的“Gnd层”,类型为“Dynamic copper”,Offset为10mil。然后点击“Route keep in”的边界完成铺铜(实际为将Route keep in 复制成了 POWER层的铜皮,铜皮比Route keep in 小10mil)

第3步:内电层分割

铺铜完成后,如果设计中,存在不止一个电压,往往还需要分割内电层。本文涉及的设计样例中POWER层,存在

5V和3.3V两个电压(存在更多的电压的内电层分割方法也是类似的)。具体分割方法如下

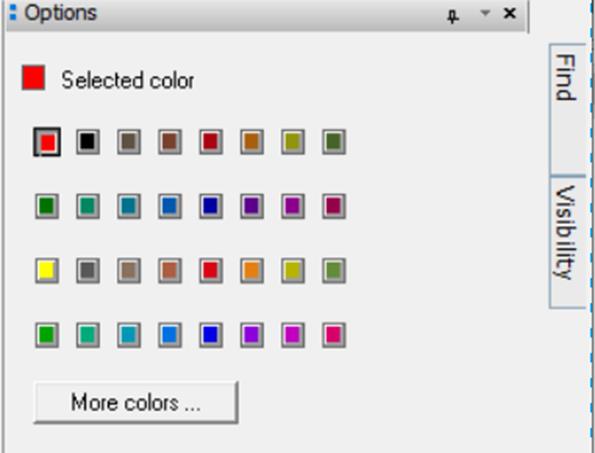

首先将5V的网络高亮为红色

执行“highlight”

执行“Assign color”

执行“Assign color”

Color配置为红色

选择“5V”的网络

然后将3.3V的网络高亮为黄色

Color配置为黄色

选择“3.3V”的网络

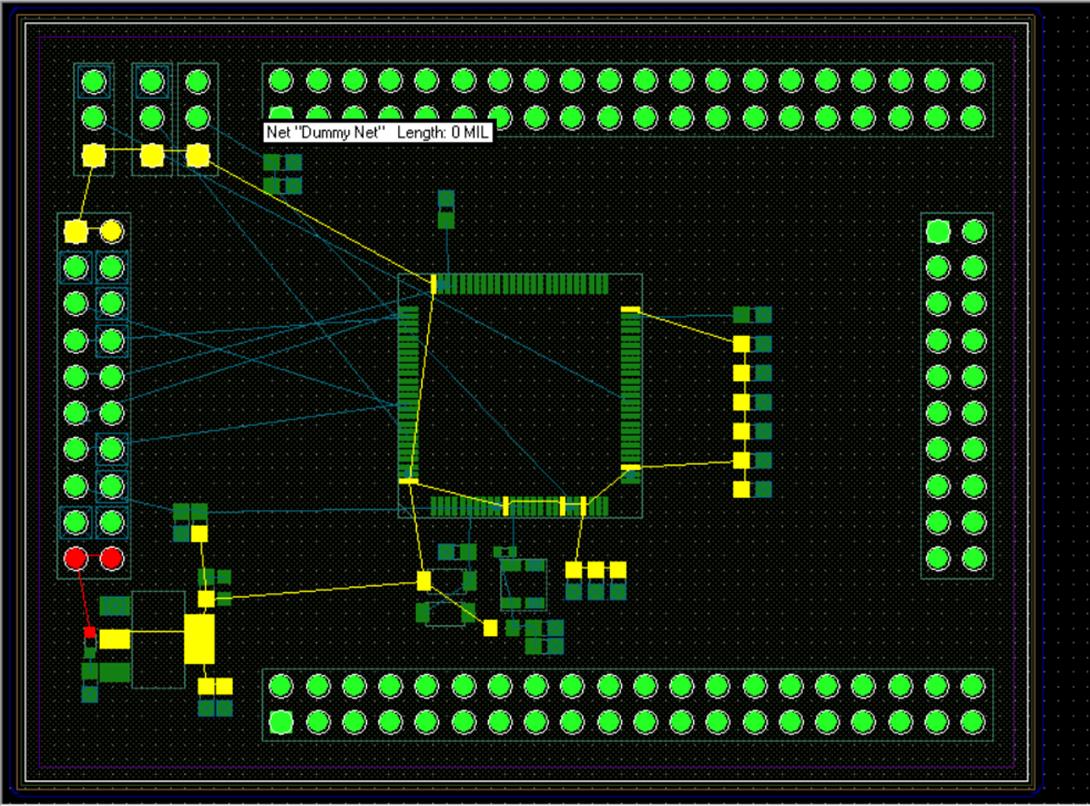

高亮后的效果如下,5V网络被高亮成了红色,3.3V网络被高亮成了蓝色

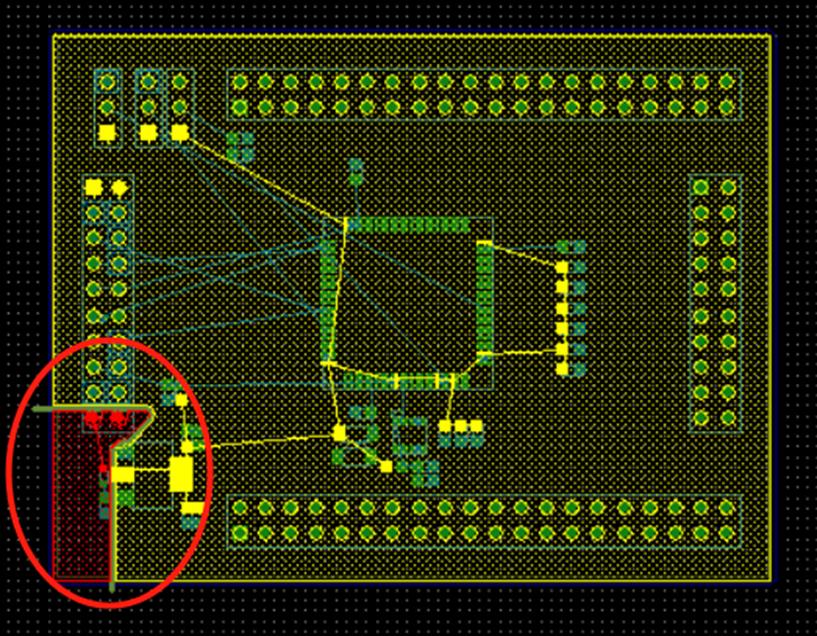

最后根据5V和3.3V所在的位置分割电源层平面

执行“add →line”设置使用“Anti Etch”分割“Power”层,仅有3.3V和5V的电压,使用25mil的线宽即可。(如有更高的电压建议使用50mile)

划线将3.3V高亮区域和5V高亮区域分开

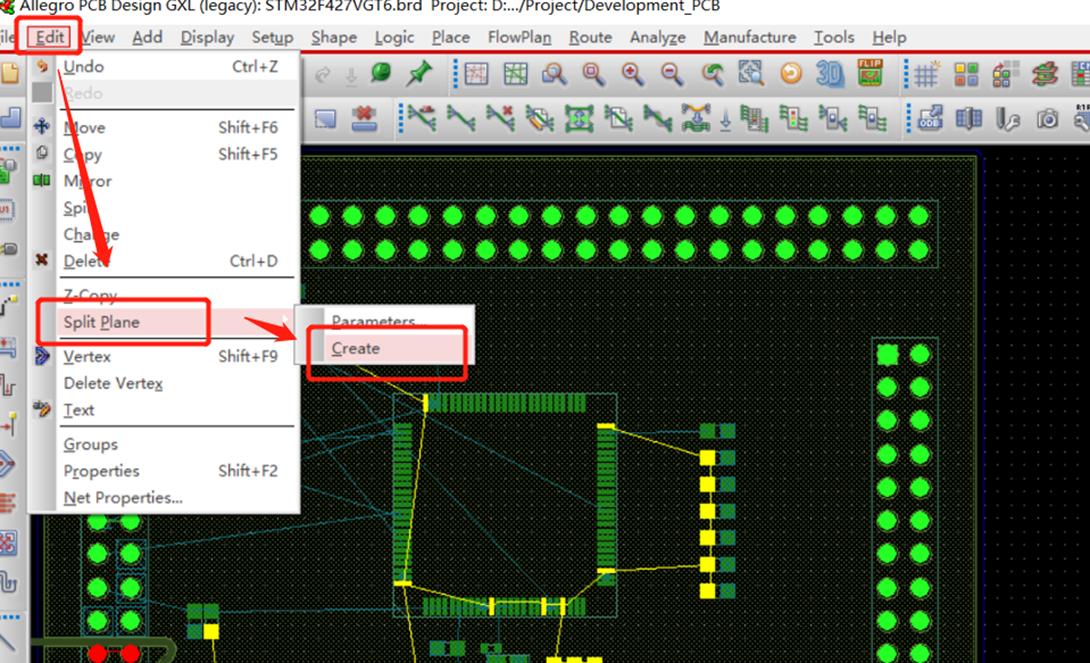

执行“Edit→Split→Split Plane→Create”

选择分割平面为“Power”铜皮类型为“Dynamic”然后点击“create”

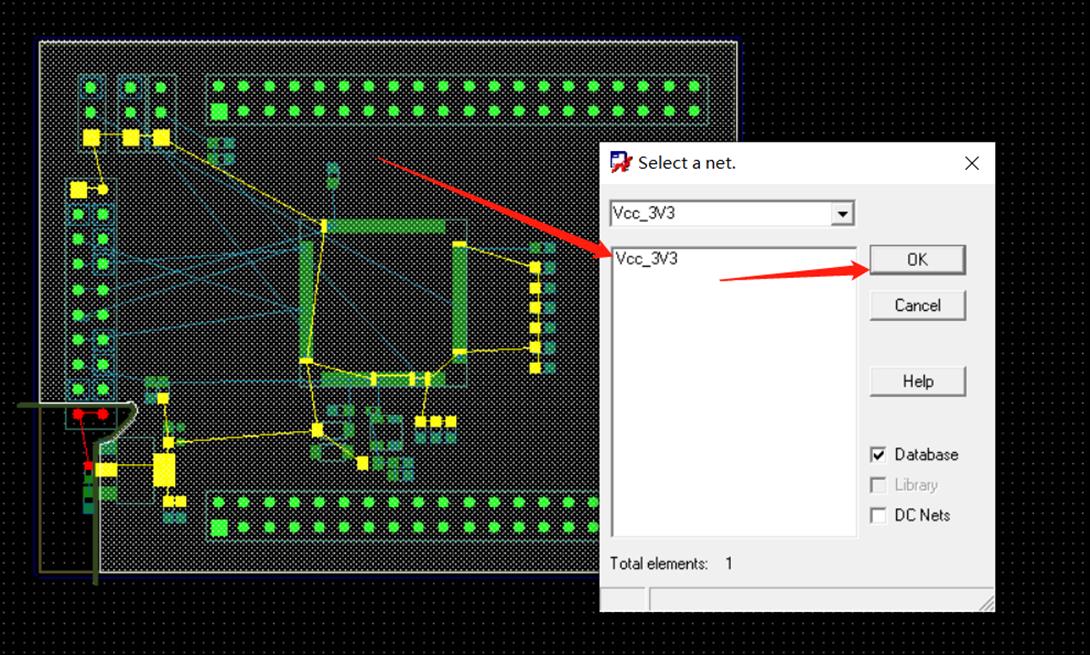

为3.3V的铜皮分配网络

为5V的铜皮分配网络

完成分割后的效果

以上是关于Cadence Allegro铺铜及内电层设计图文及视频演示的主要内容,如果未能解决你的问题,请参考以下文章

Cadence Allegro 如何关闭铺铜(覆铜)shape的显示和设置shape显示模式–allegro小技巧

Cadence Allegro巧用自动布线工具图文教程及视频演示

Cadence Allegro过电阻电容的XNET等长图文视频演示