Verilog HDL实现的74HC595的进阶版本

Posted hhh江月

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Verilog HDL实现的74HC595的进阶版本相关的知识,希望对你有一定的参考价值。

Verilog HDL实现的74HC595的进阶版本

一、简介

74HC595是一个8位串行输入、并行输出的位移缓存器:并行输出为三态输出。在SCK 的上升沿,串行数据由SDL输入到内部的8位位移缓存器,并由Q7’输出,而并行输出则是在LCK的上升沿将在8位位移缓存器的数据存入到8位并行输出缓存器。当串行数据输入端OE的控制信号为低使能时,并行输出端的输出值等于并行输出缓存器所存储的值。

二、代码实现

主文件:

module hc595(

input sclr_n, si, sck, rck, g_n,rst,clk,

output qh, qg, qf, qe, qd, qc, qb, qa, qh_qout

);

reg [7:0] shift_dffs;

initial

begin

shift_dffs <= 8'b11111111;

storge_dffs<= 8'b11111111;

end

//debounce (clk,rst,sclr_n,sclr_n0);

//debounce (clk,rst,si,si0);

debounce (clk,rst,sck,sck0);

debounce (clk,rst,rck,rck0);

//debounce (clk,rst,g_n,g_n0);

always @(posedge sck0 or negedge sclr_n)

begin

if(~sclr_n)

// sclr_n 也是一个使能端。

begin

shift_dffs [7:0] <= 8'b11111111;

end

else

begin

// si 是由一个拨码开关来决定具体的数值的。

shift_dffs [7:0] <= shift_dffs [6:0], si;

// 对数据进行移位寄存的操作。

end

end

reg [7:0] storge_dffs;

always @(posedge rck0)

begin

storge_dffs[7:0] <= shift_dffs[7:0];

end

// 将数据存储并进行显示。

assign qh_qout = shift_dffs[7];

assign qh, qg, qf, qe, qd, qc, qb, qa = g_n ? 8'bzzzzzzzz : storge_dffs[7:0];

// g_n 为使能端。

endmodule

主文件里面用到的一个按键消抖模块:

module debounce (clk,rst,key,key_pulse);

parameter N = 1; //要消除的按键的数量

input clk;

input rst;

input [N-1:0] key; //输入的按键

output [N-1:0] key_pulse; //按键动作产生的脉冲

reg [N-1:0] key_rst_pre; //定义一个寄存器型变量存储上一个触发时的按键值

reg [N-1:0] key_rst; //定义一个寄存器变量储存储当前时刻触发的按键值

wire [N-1:0] key_edge; //检测到按键由高到低变化是产生一个高脉冲

//利用非阻塞赋值特点,将两个时钟触发时按键状态存储在两个寄存器变量中

always @(posedge clk or negedge rst)

begin

if (!rst) begin

key_rst <= N1'b1; //初始化时给key_rst赋值全为1,中表示N个1

key_rst_pre <= N1'b1;

end

else begin

key_rst <= key; //第一个时钟上升沿触发之后key的值赋给key_rst,同时key_rst的值赋给key_rst_pre

key_rst_pre <= key_rst; //非阻塞赋值。相当于经过两个时钟触发,key_rst存储的是当前时刻key的值,key_rst_pre存储的是前一个时钟的key的值

end

end

assign key_edge = key_rst_pre & (~key_rst);//脉冲边沿检测。当key检测到下降沿时,key_edge产生一个时钟周期的高电平

reg [17:0] cnt; //产生延时所用的计数器,系统时钟12MHz,要延时20ms左右时间,至少需要18位计数器

//产生20ms延时,当检测到key_edge有效是计数器清零开始计数

always @(posedge clk or negedge rst)

begin

if(!rst)

cnt <= 18'h0;

else if(key_edge)

cnt <= 18'h0;

else

cnt <= cnt + 1'h1;

end

reg [N-1:0] key_sec_pre; //延时后检测电平寄存器变量

reg [N-1:0] key_sec;

//延时后检测key,如果按键状态变低产生一个时钟的高脉冲。如果按键状态是高的话说明按键无效

always @(posedge clk or negedge rst)

begin

if (!rst)

key_sec <= N1'b1;

else if (cnt==18'h3ffff)

key_sec <= key;

end

always @(posedge clk or negedge rst)

begin

if (!rst)

key_sec_pre <= N1'b1;

else

key_sec_pre <= key_sec;

end

assign key_pulse = key_sec_pre & (~key_sec);

endmodule

然后进行引脚的分配:

之后进行编译:

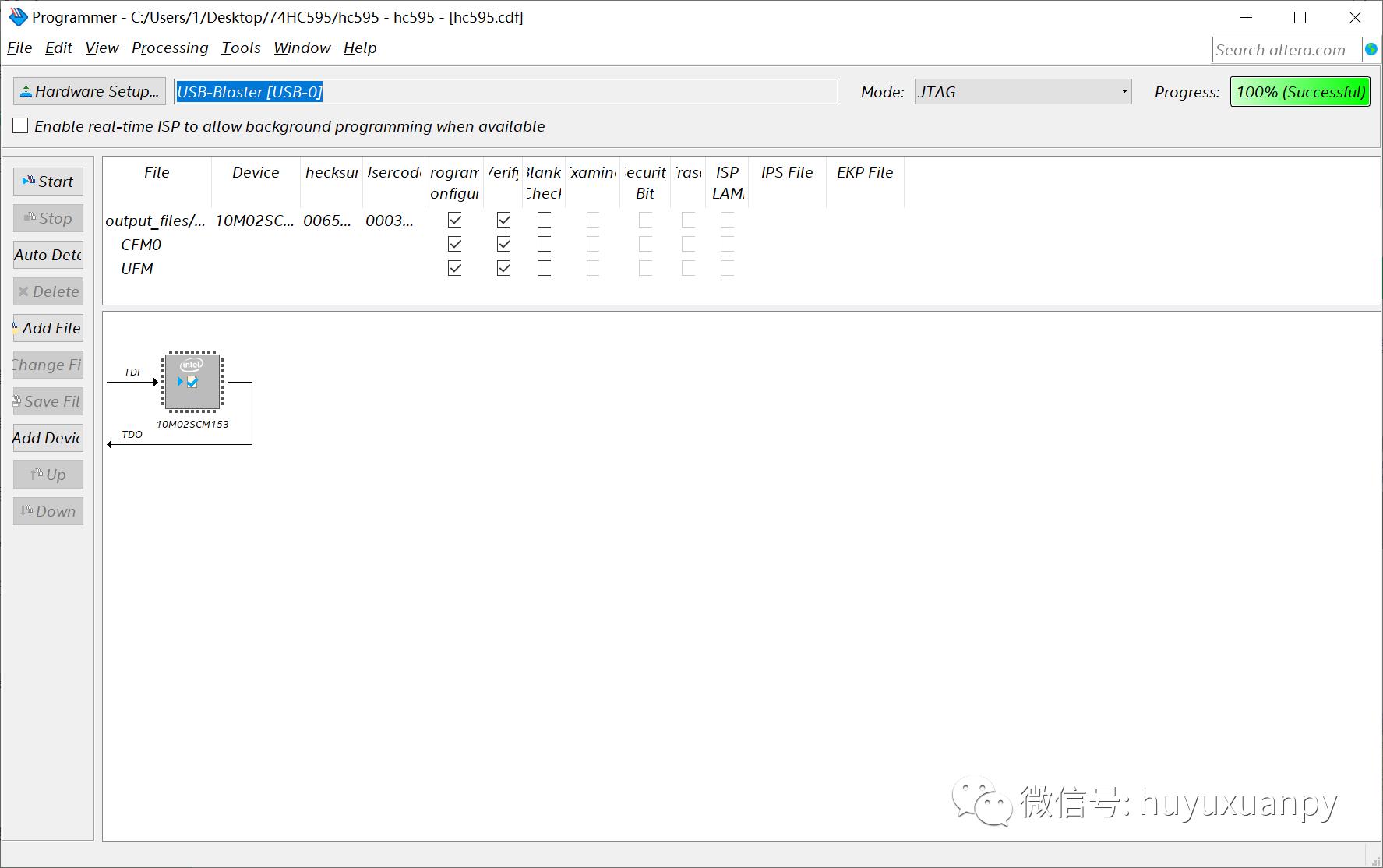

最后进行烧录:

然后就完成了具体的所有的操作了啦。

三、效果展示

我们采用视频的形式来展示效果,如果喜欢的话可以去点个赞:

https://www.bilibili.com/video/BV1Zh411s745?spm_id_from=333.999.0.0

Verilog HDL实现的74HC595的进阶版本

以上是关于Verilog HDL实现的74HC595的进阶版本的主要内容,如果未能解决你的问题,请参考以下文章