Verilog HDL 模拟 汽车尾灯自动控制系统

Posted hhh江月

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Verilog HDL 模拟 汽车尾灯自动控制系统相关的知识,希望对你有一定的参考价值。

Verilog HDL 模拟 汽车尾灯自动控制系统

一、要求介绍:

设计一个汽车尾灯自动控制系统

要求:根据汽车行驶状态自动控制汽车尾灯

直行:尾灯不亮

右转:右侧尾灯亮而且按秒闪烁,左侧尾灯不亮

左转:左侧尾灯亮而且按秒闪烁,右侧尾灯不亮

临时停车或故障:两侧尾灯同时闪烁

倒车显示(可选)

注:用三色 LED 代表左右汽车尾灯,用拨码开关控制汽车行驶状态,还可以考虑用七段数码管和单色 LED 显示汽车状态

二、代码实现

1、主模块的代码

module car(rst, clk, start, left, right, error, back,

led11, led12, led13, led21, led22, led23);

input rst;

// reset.

input clk;

// clock.

input start;

// strat the car.

input left;

// go left.

input right;

// go right.

input error;

// if error.

input back;

// go back.

output reg led11;

output reg led12;

output reg led13;

output reg led21;

output reg led22;

output reg led23;

// lights.

wire clkout1;

wire clkout2;

time_split #(.N(6000000),

.WIDTH(23)) t1 (

.clk(clk),

.rst_n(rst),

.clkout(clkout1));

// time_split 1.

// 2 Hz.

time_split #(.N(3000000),

.WIDTH(23)) t2 (

.clk(clk),

.rst_n(rst),

.clkout(clkout2));

// time_split 2.

// 4 Hz.

always@(posedge clk)

begin

if(start)

// the car has started.

begin

if(~left && ~right && ~error && back)

// no other operators.

begin

led11 <= 1;

led12 <= 1;

led13 <= 1;

led21 <= 1;

led22 <= 1;

led23 <= 1;

// all the lights are closed.

end

// four situations.

else

begin

if(left)

// turn left.

begin

led11 <= 1;

led12 <= clkout1;// turn left.

// 2 Hz.

led13 <= 1;

led21 <= 1;

led22 <= 1;

led23 <= 1;

end

if(right)

// turn right.

begin

led11 <= 1;

led12 <= 1;

led13 <= 1;

led21 <= 1;

led22 <= clkout1;// turn right.

// 2 Hz.

led23 <= 1;

end

if(error)

// if there is an error or stop the car.

begin

led11 <= clkout2;

// if there is an error or stop the car.

// 4 Hz.

led12 <= 1;

led13 <= 1;

led21 <= clkout2;

// if there is an error or stop the car.

// 4 Hz.

led22 <= 1;

led23 <= 1;

end

if(~back)

// if go back

begin

led11 <= 1;

led12 <= 1;

led13 <= clkout1;// if go back

// 2 Hz.

led21 <= 1;

led22 <= 1;

led23 <= clkout1;// if go back

// 2 Hz.

end

end

end

else

// do not start.

begin

led11 <= 1;

led12 <= 1;

led13 <= 1;

led21 <= 1;

led22 <= 1;

led23 <= 1;

// all the lights are closed.

end

end

endmodule

2、时钟分频模块

// ********************************************************************

// >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<<

// ********************************************************************

// File name : divide.v

// Module name : divide

// Author : STEP

// Description : clock divider

// Web : www.stepfpga.com

//

// --------------------------------------------------------------------

// Code Revision History :

// --------------------------------------------------------------------

// Version: |Mod. Date: |Changes Made:

// V1.0 |2017/03/02 |Initial ver

// --------------------------------------------------------------------

// Module Function:任意整数时钟分频

module time_split ( clk,rst_n,clkout);

input clk,rst_n; //输入信号,其中clk连接到FPGA的C1脚,频率为12MHz

output clkout; //输出信号,可以连接到LED观察分频的时钟

//parameter是verilog里常数语句

// parameter WIDTH = 3; //计数器的位数,计数的最大值为 2**WIDTH-1

// parameter N = 5; //分频系数,请确保 N < 2**WIDTH-1,否则计数会溢出

//

parameter N=12000000;

parameter WIDTH=24;

reg [WIDTH-1:0] cnt_p,cnt_n; //cnt_p为上升沿触发时的计数器,cnt_n为下降沿触发时的计数器

reg clk_p,clk_n; //clk_p为上升沿触发时分频时钟,clk_n为下降沿触发时分频时钟

//上升沿触发时计数器的控制

always @ (posedge clk or negedge rst_n ) //posedge和negedge是verilog表示信号上升沿和下降沿

//当clk上升沿来临或者rst_n变低的时候执行一次always里的语句

begin

if(!rst_n)

cnt_p<=0;

else if (cnt_p==(N-1))

cnt_p<=0;

else cnt_p<=cnt_p+1; //计数器一直计数,当计数到N-1的时候清零,这是一个模N的计数器

end

//上升沿触发的分频时钟输出,如果N为奇数得到的时钟占空比不是50%;如果N为偶数得到的时钟占空比为50%

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

clk_p<=0;

else if (cnt_p<(N>>1)) //N>>1表示右移一位,相当于除以2去掉余数

clk_p<=0;

else

clk_p<=1; //得到的分频时钟正周期比负周期多一个clk时钟

end

//下降沿触发时计数器的控制

always @ (negedge clk or negedge rst_n)

begin

if(!rst_n)

cnt_n<=0;

else if (cnt_n==(N-1))

cnt_n<=0;

else cnt_n<=cnt_n+1;

end

//下降沿触发的分频时钟输出,和clk_p相差半个时钟

always @ (negedge clk)

begin

if(!rst_n)

clk_n<=0;

else if (cnt_n<(N>>1))

clk_n<=0;

else

clk_n<=1; //得到的分频时钟正周期比负周期多一个clk时钟

end

assign clkout = (N==1)?clk:(N[0])?(clk_p&clk_n):clk_p; //条件判断表达式

//当N=1时,直接输出clk

//当N为偶数也就是N的最低位为0,N(0)=0,输出clk_p

//当N为奇数也就是N最低位为1,N(0)=1,输出clk_p&clk_n。正周期多所以是相与

endmodule

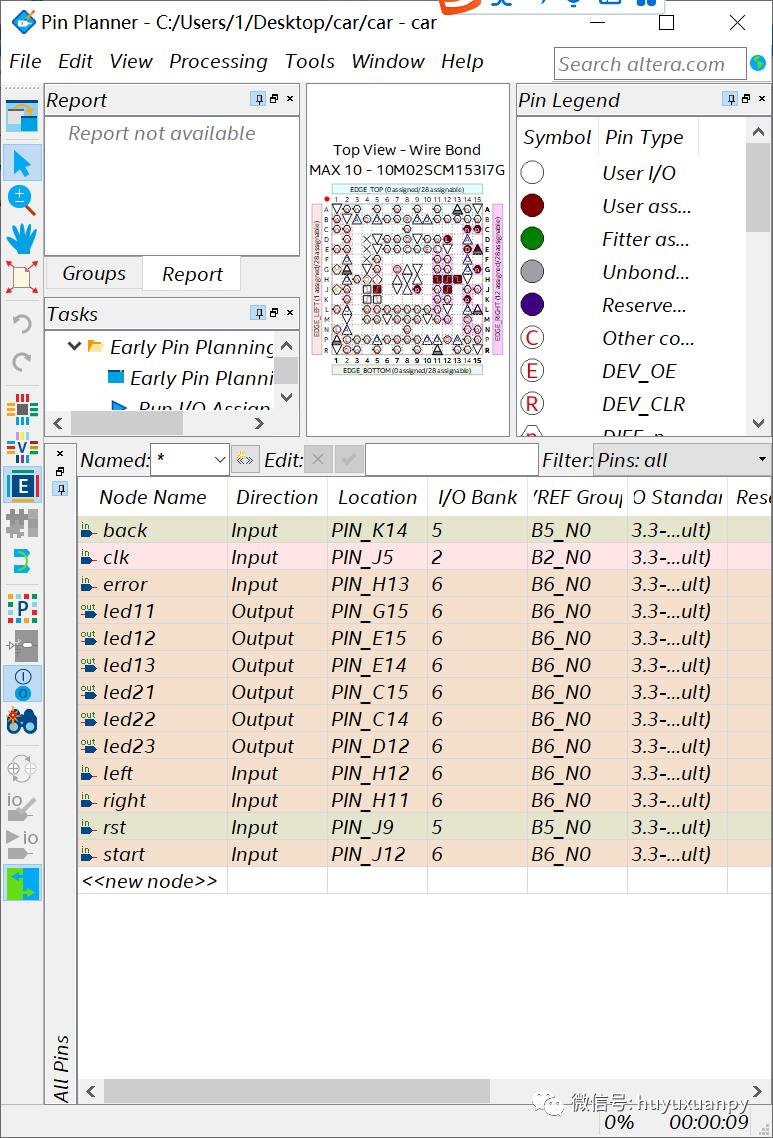

然后,我们进行管脚的分配:

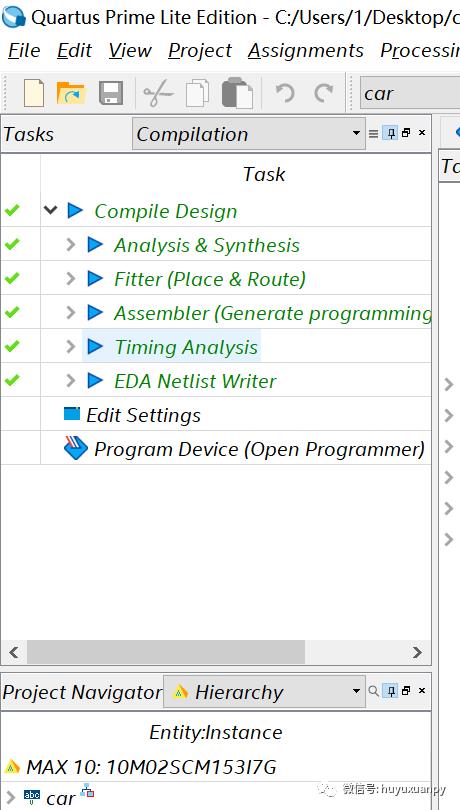

接下来就是进行编译:

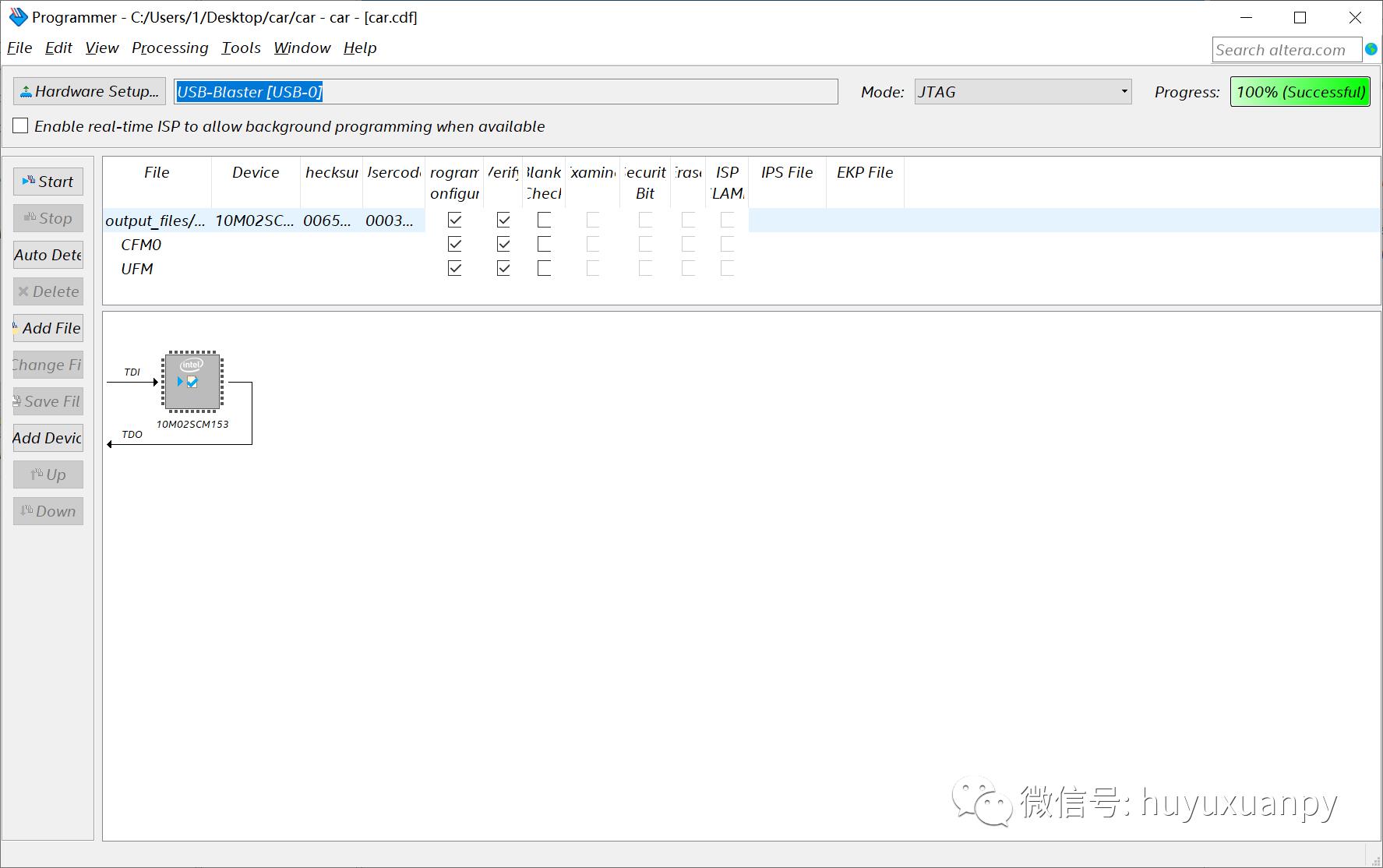

最后进行烧录:

三、效果展示

我们还是采用视频的方法来进行效果的展示与呈现:

(如果你喜欢的话就去点个赞吧)

https://www.bilibili.com/video/BV1JL411778U?spm_id_from=333.999.0.0

Verilog HDL 模拟 汽车尾灯自动控制系统

最后,谢谢大家的支持了啦。

喜欢的话就点个赞吧。

以上是关于Verilog HDL 模拟 汽车尾灯自动控制系统的主要内容,如果未能解决你的问题,请参考以下文章