第1期硬件篇:硬件平台介绍2_AC620开发板使用

Posted aa1319594154

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了第1期硬件篇:硬件平台介绍2_AC620开发板使用相关的知识,希望对你有一定的参考价值。

文章目录

简介

介绍AC620开发板的使用。

目标

了解EP4CE10F17C的重点电路设计。

阅读基础

熟悉计算机。

快速阅读

了解的部分跳过。

环境说明

windows10

参考资料

小梅哥教程:

02A【学习教材】FPGA系统设计与验证实战指南V3.002B【学习教材】小梅哥FPGA逻辑设计进阶教程2020版V1.0

正点原子开拓者教程:

- 开拓者

FPGA开发指南V1.5

野火征途教程:

- 征途

Pro《FPGAVerilog开发实战指南——基于Altera EP4CE10》(上下)

开发板烧写配置

AC620开发板提供了一个串行配置设备用来对 Cyclone IV E FPGA芯片进行配置,上电以后配置数据可以自动从配置设备加载到 FPGA,使用 Quartus软件,我们也可以在任何时候重新配置FPGA,当然也可以改变串行非易失存储设备中存储的内容,下面将描述这两种类型的配置。

JTAG 配置

这种编程方法将 FPGA 配置比特流直接下载到了开发板上的 Cyclone IV E

FPGA芯片中,在上电状态下,FPGA将保留此配置,逻辑功能可以正常运行,但断电以后,

配置信息将会丢失,需要上电以后重新进行配置。

JIC 配置

Altera允许我们在 JTAG下载模式下配置 EPCS器件,通过 Quartus软件自带的转换工具,我们可以将编译生成的.sof 文件转换为.jic 文件,然后通过 JTAG口下载到EPCS器件,这样就可以做到配置数据掉电不丢失,器件在上电时根据设置从 EPCS器件中读取配置数据并完成 FPGA的配置和初始化工作。

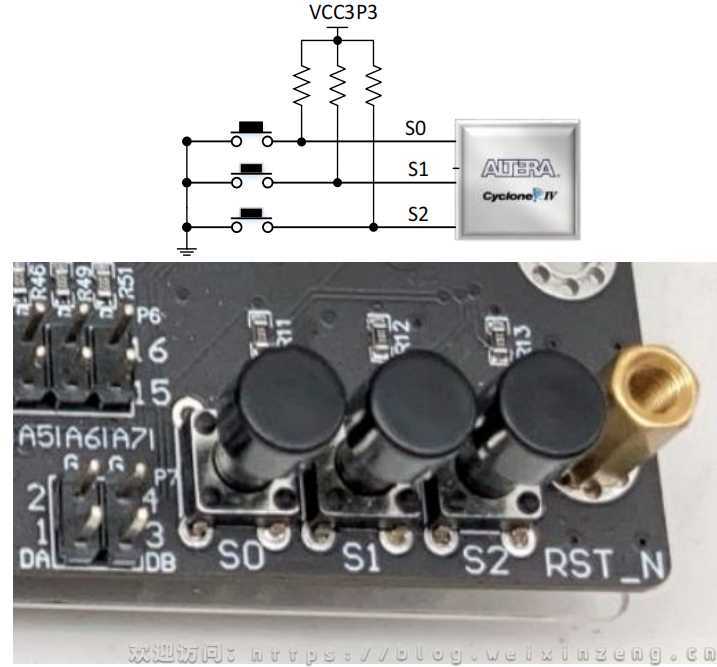

轻触按键

如图所示,AC620开发板提供了三个轻触按键,三个按键分别被称为 S0、S1、S2。此三个引脚直接与 FPGA管脚相连,并接上了上拉电阻。

在没有按键按下的时候,每个按键端输出的都是高电平,当按键按下的时候,被按下的按键端会输出低电平。轻触按键作为最简单的输入设备,适合在需要给系统输入控制信号的场合使用。

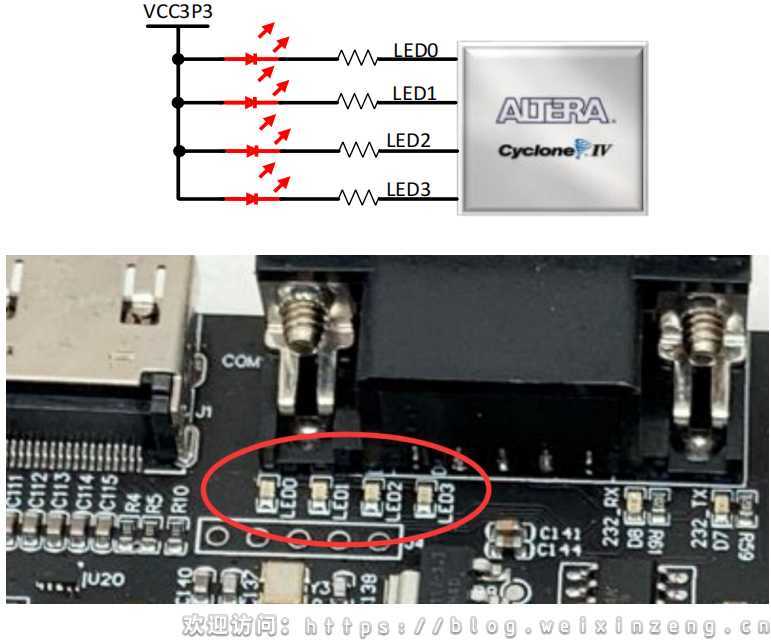

用户 LED

芯路恒开发板提供了四个红色的 LED调试灯, 所有的 LED灯都是通过Cyclone IV E FPGA 直接驱动。

当 FPGA输出低电平时,LED点亮,当 LED输出高电平时,LED灯熄灭。

下图展示了 LED和 FPGA 的连接关系。

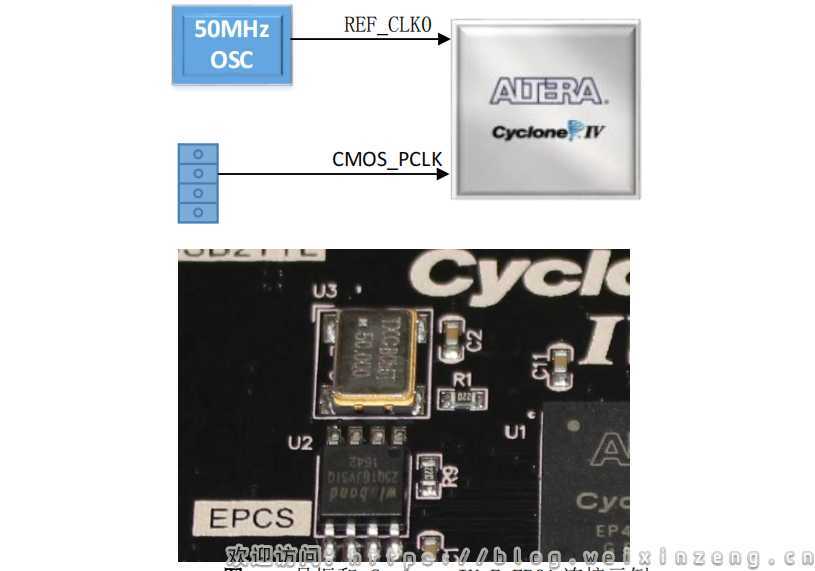

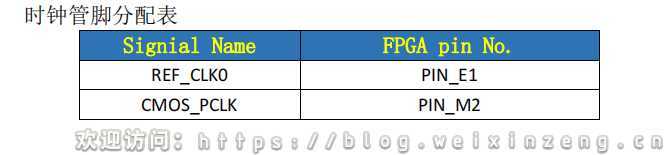

时钟输入

AC620V2开发板设计了 2 路时钟源,第一路由板载 50MHz有源晶振提供,另外第二路集成在 CMOS摄像头接口中(一般用于输入 CMOS摄像头时钟像素时 钟)。

2 路时钟均通过 Cyclone IV E 专用的时钟引脚进行输入,保证了最好的时钟质量,并保证可以配置到对应的全局时钟链路上。

下图展示了时钟和FPGA 的连接关系

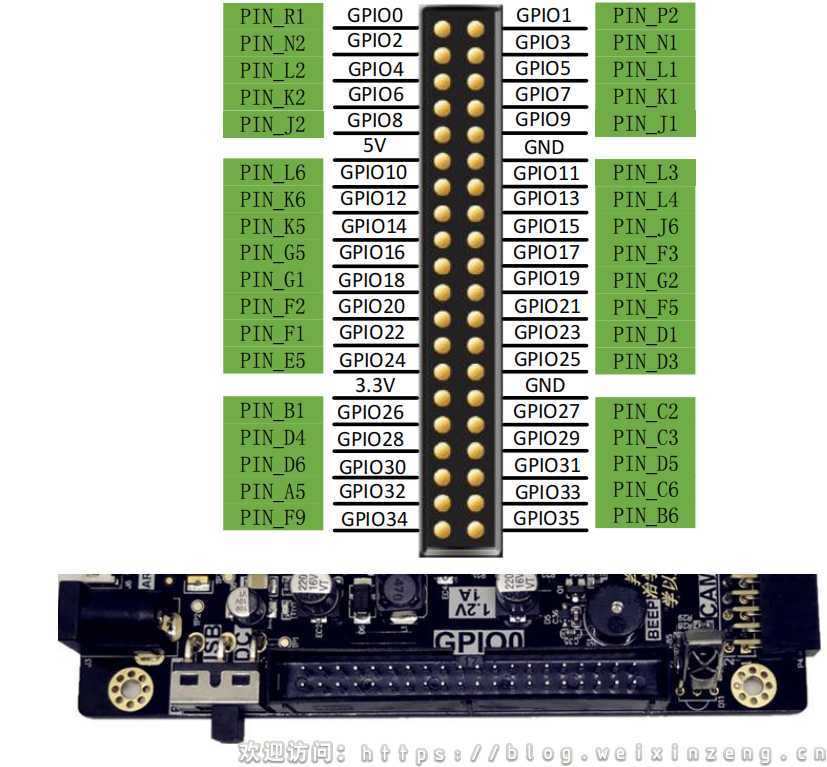

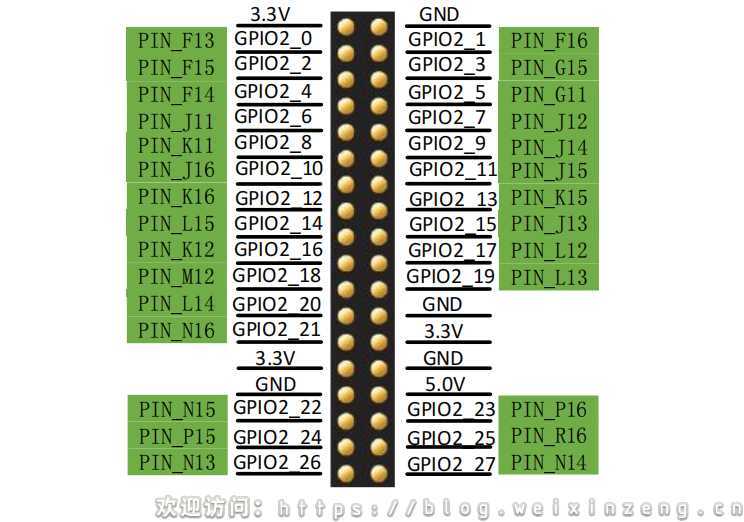

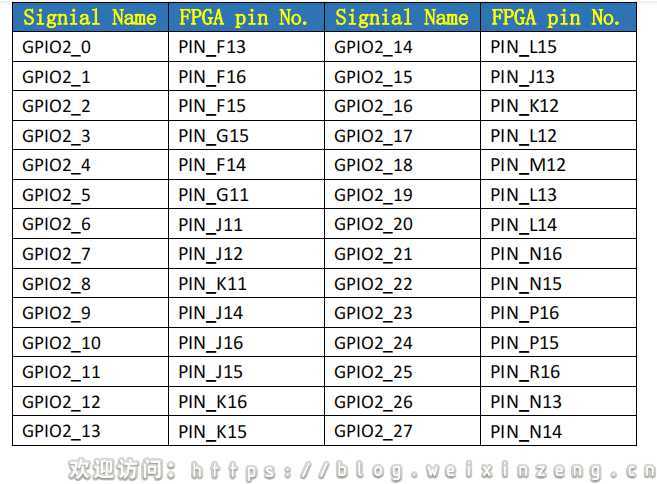

GPIO 接口

芯路恒 AC620V2开发板提供了 1 个 40Pin的与友晶科技 DE2开发板兼容的GPIO接口, 端口使用标准的 IDC3-40 接口。

该端口除了有 36 个引脚直接连到了 Cyclone IV E FPGA以外, 还输出了 DC +5V (VCC5), DC +3.3V (VCC3P3), 和两个接地的引脚。端口名为GPIO0。

下图展示了 GPIO0的端子 FPGA 管脚连接关系。

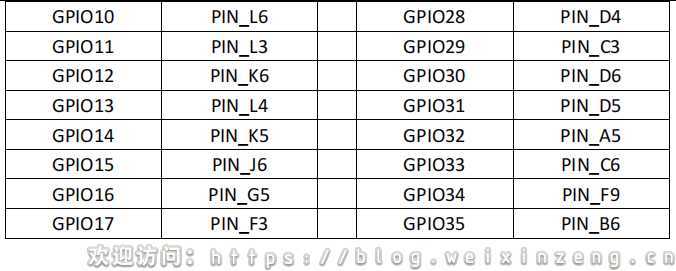

红外接收

芯路恒 AC620V2开发板包含一个红外接收模块 IR。

下图展示了 IR 和FPGA 的电路连接关系。

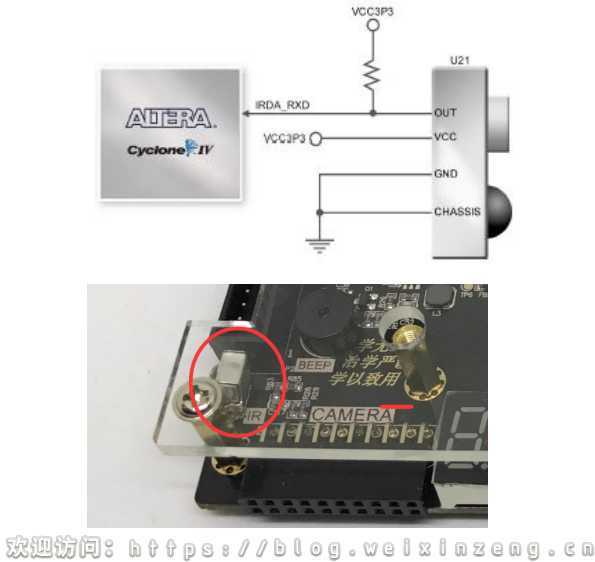

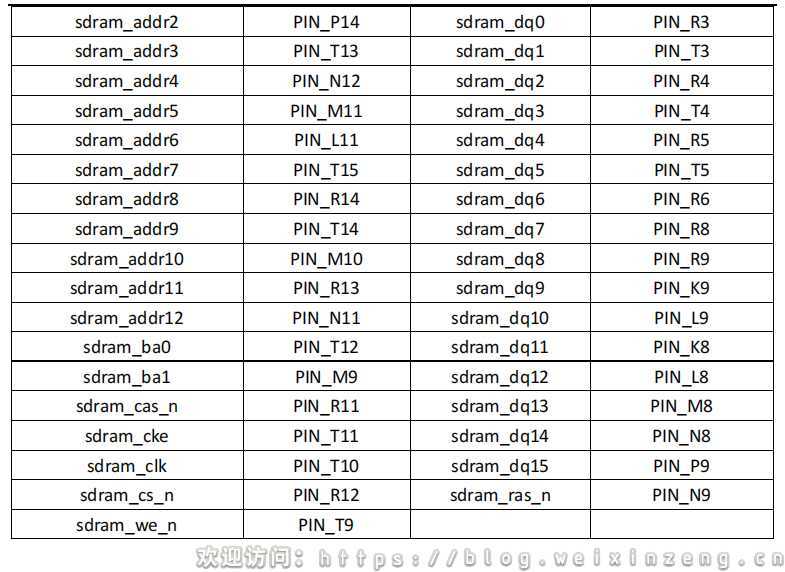

SDRAM

AC620V2开发板设计了一片存储容量高达 256Mb的 SDRAM存储器,该芯片与FPGA相连的数据总线位宽为16 bit,采用3.3V供电,最高运行频率可达166MHz。

下图展示了 SDRAM和 FPGA 之间的连接关系。

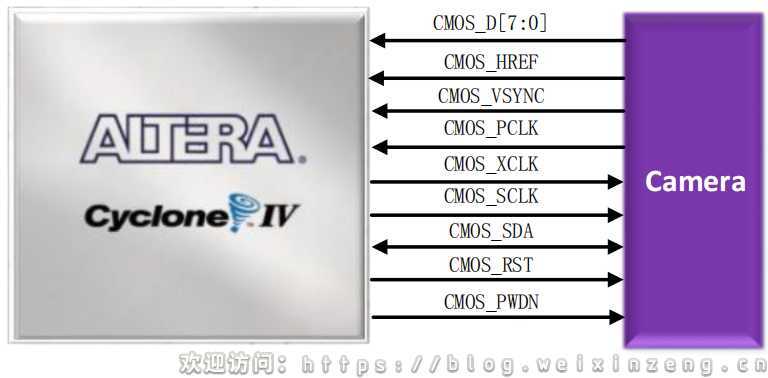

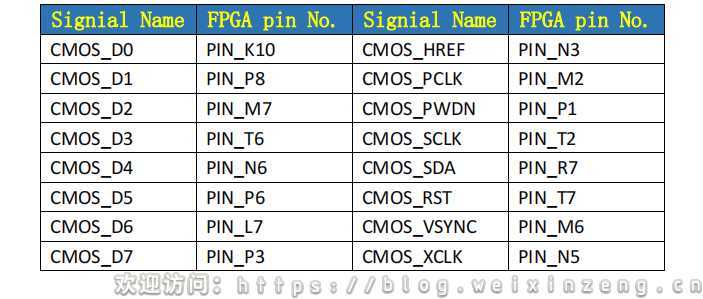

摄像头接口

芯路恒 AC620V2开发板支持视频图像项目的开发,板载的 CMOS接口可以用来连接 OV7670(30W)、OV7725(30W)、OV2640(200W)、OV5640(500W)等常用图像采集摄像头(见图 )。配合芯路恒板载的片外 SDRAM 数据存储器,用户可以进行数字图像的采集处理,也可以很方便地验证图像领域的各种算法。

下图给出了 CMOS端子和 FPGA 连接关系。

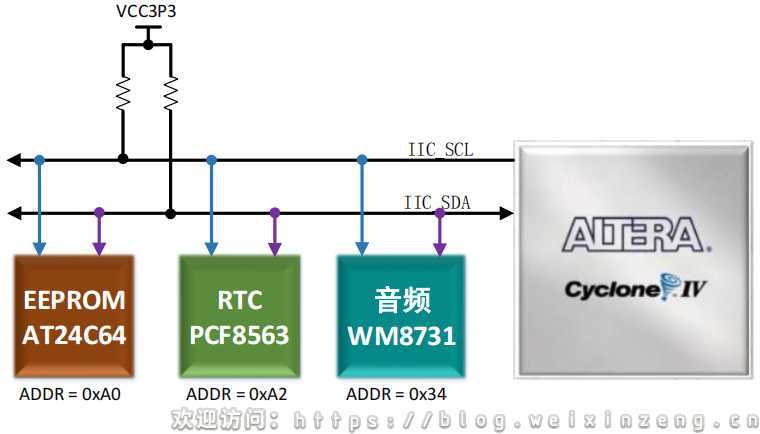

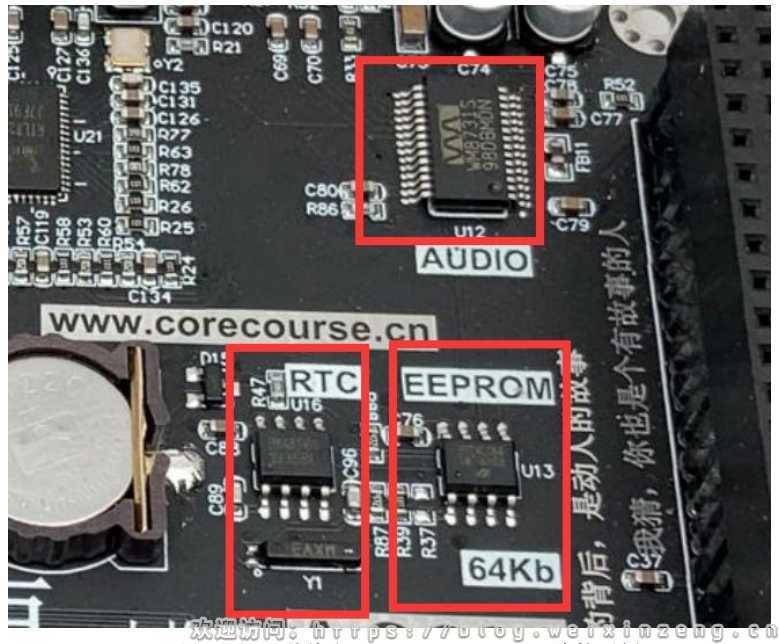

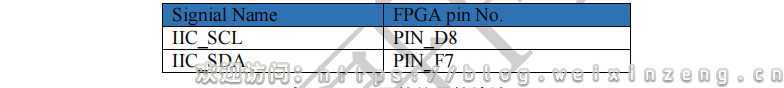

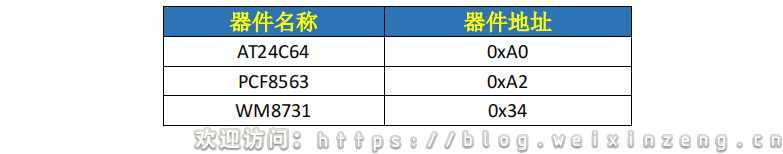

IIC 总线(EEPROM+RTC+WM8731)

芯路恒 AC620V2开发板有 4 个设备使用 IIC总线,分别为 AT24C64的 EEPROM存储器、PCF8563型实时时钟芯片、WM8731控制接口以及 CMOS摄像头接口,

其中,CMOS摄像头接口上的 IIC配置总线单独与 FPGA连接,不与其他 IIC器件共享总线,EEPROM存储器、PCF8563型实时时钟芯片、WM8731控制接口共享同一个 IIC总线。

下图给出了 EEPROM+RTC+WM8731 与 FPGA 的连接关系。

通用显示扩展接口

AC620V2开发板上提供了一个兼容性强大的 2*18 通用显示扩展接口,该接 口可连接我们推出的 5 寸 800*480 RGB 接口的显示屏(代替 VGA显示器),或者连接“数码管+8 位 VGA+PS2”三合一模块,还可连接我们推出的 24 位高性能 VGA输出模块。

当然,用户也可以使用该接口作为通用扩展接口连接用户自己的设备。例如,该接口能够直接连接知名 STM32开发板正点原子推出的 2.8 寸、3.5 寸 MCU接口的液晶屏。

总结

介绍了 AC620开发板的资源使用。

其它

相关资源下载

FPGA开发学习参考教程.rar-嵌入式文档类资源-CSDN文库

常见问题

最近更新

小有收获

有收获记得三连哦😄

欢迎关注微信公众号

所有文章同步更新。

以上是关于第1期硬件篇:硬件平台介绍2_AC620开发板使用的主要内容,如果未能解决你的问题,请参考以下文章