Xilinx FPGA平台GTX简易使用教程GTX IP核配置教程

Posted FPGA大叔

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Xilinx FPGA平台GTX简易使用教程GTX IP核配置教程相关的知识,希望对你有一定的参考价值。

干货来了,GTX核配置,搬砖全靠它~~

汇总篇:

目录

前言

作为一名初学者,也曾被GTX一堆信号搞得头晕脑胀,在学习了各位大佬的文章后,结合自己的理解和实践,整理这一系列快速上手的GTX使用教程。

为了快速上手,本文使用了“丐版”配置 = =||

一、GTX IP核配置界面

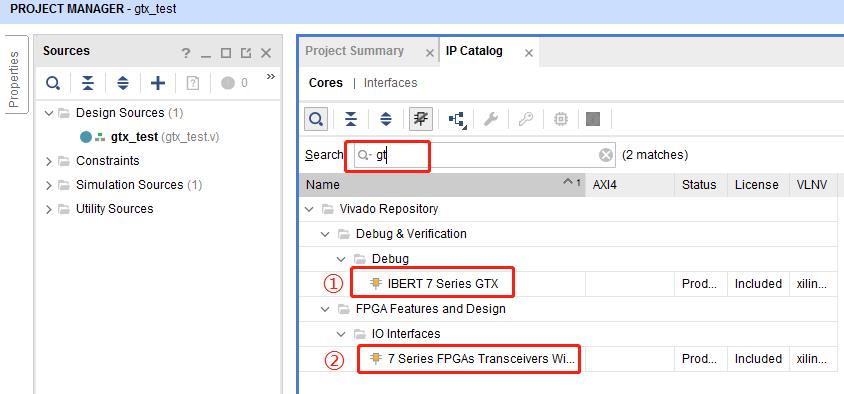

首先,在IP Catalog中输入“gt”,进入GTX的IP核配置界面。

①ibert :基础知识部分曾介绍过,是用于测试通道通信质量的辅助IP。

②GT,是它是它就是它~ GTP/GTX/GTH 都是它~

1.1第一页配置

①自定义名称

②GT类型:A7只能选GTP;K7是GTX;V7既有GTX也有GTH

③共享逻辑选项:一般选择放在example design中,这样设计更灵活。

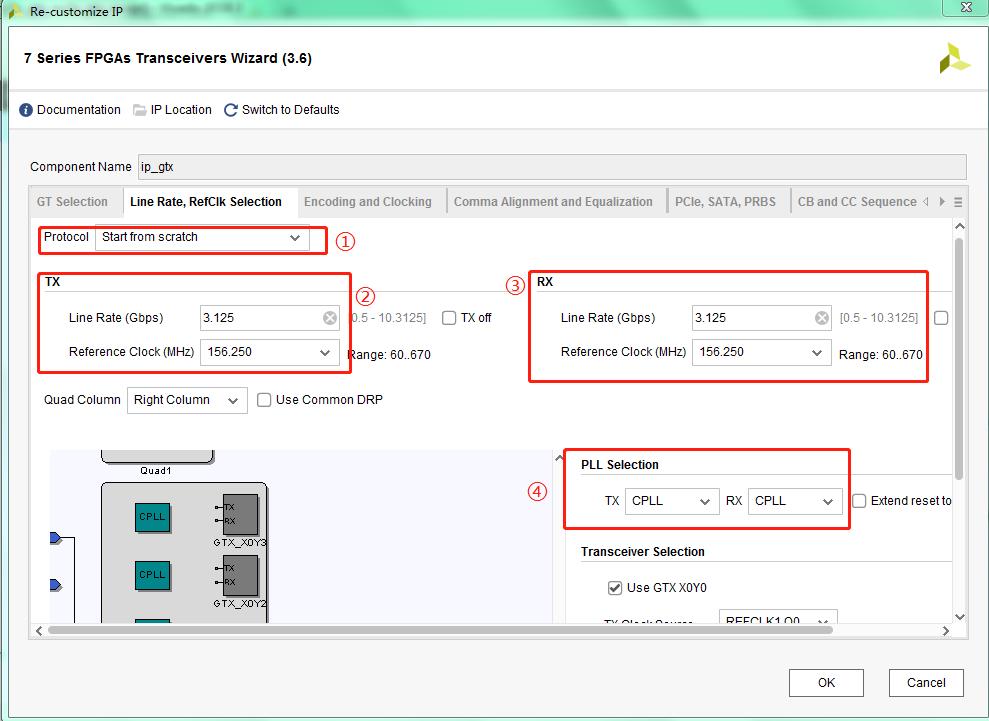

1.2第二页配置

①协议:支持sata,aurora,hdmi等等;“丐版”配置,我们默认Start from scratch“白手起家”~

②发送端TX:Line Rate:根据需要选择,但是必须在器件支持的范围内;参考时钟:根据硬件板子决定;

③接收端RX:同发送端,但是可以配置成不一样,GTX是全双工的,甚至可以关闭发送 □TX off 或者关闭接收□RX off;

④选择CPLL还是QPLL,注意CPLL最高只支持6.xGbps,超过了就必须使用QPLL(软件会默认强制使用)

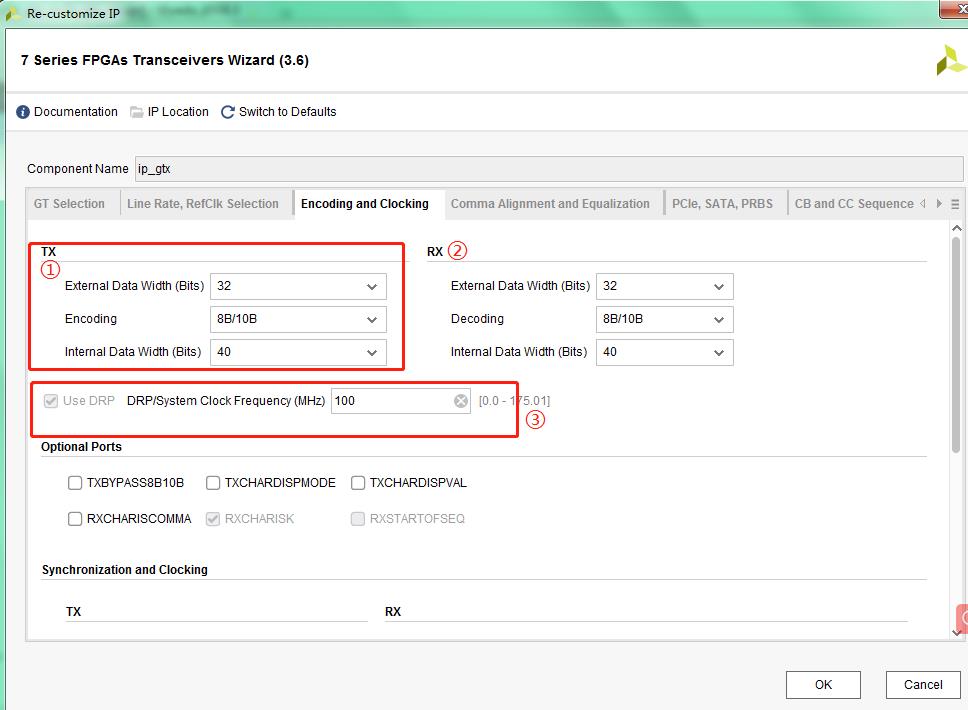

1.3第三页配置

①TX端:

外部数据位宽:就是我们逻辑并行数据的位宽,对于核来讲就是外部数据,我们这里选32。

编码方式:一般选择8B/10B编码

内部数据位宽:核内部的数据位宽,这个设置会影响TXUSRCLK和TXUSRCLK2的比率关系。我们这里选40。

②RX端: 一般与TX端保持一致,GTX是全双工,支持不一样的配置。

③系统时钟(DRP时钟):根据实际选择

其他:“丐版”通通不配置,但是我们还是介绍一下选项:

| 选项 | 方向 | 描述 |

| TXPCSRESET | 输入 | TX PCS部分复位信号,高有效 |

| TXBUFSTATUS | 输出 | TX buffer的状态输出,TX buffer被旁路时不可用。 |

| TXRATE | 输入 | 传输速率改变端口. |

| RXPCSRESET | 输入 | RX PCS复位信号,高有效 |

| RXBUFSTATUS | 输出 | RX buffer的状态输出,RX buffer被旁路时不可用。 |

| RXBUFRESET | 输入 | RX 弹性buffer的复位信号,RX buffer被旁路时不可用。 |

| RXRATE | 输入 | 接收改变速率的端口 |

| QPLLPD | 输入 | QPLL的下电端口。只针对GTX/GTH |

| CPLLPD | 输入 | CPLL的下电端口。只针对GTX/GTH |

| PLL0PD | 输入 | GTP的PLL0的下电端口。 |

| 大部分都是复位与初始化里面介绍的信号,推荐看系列文章(3)GTX复位与初始化 | ||

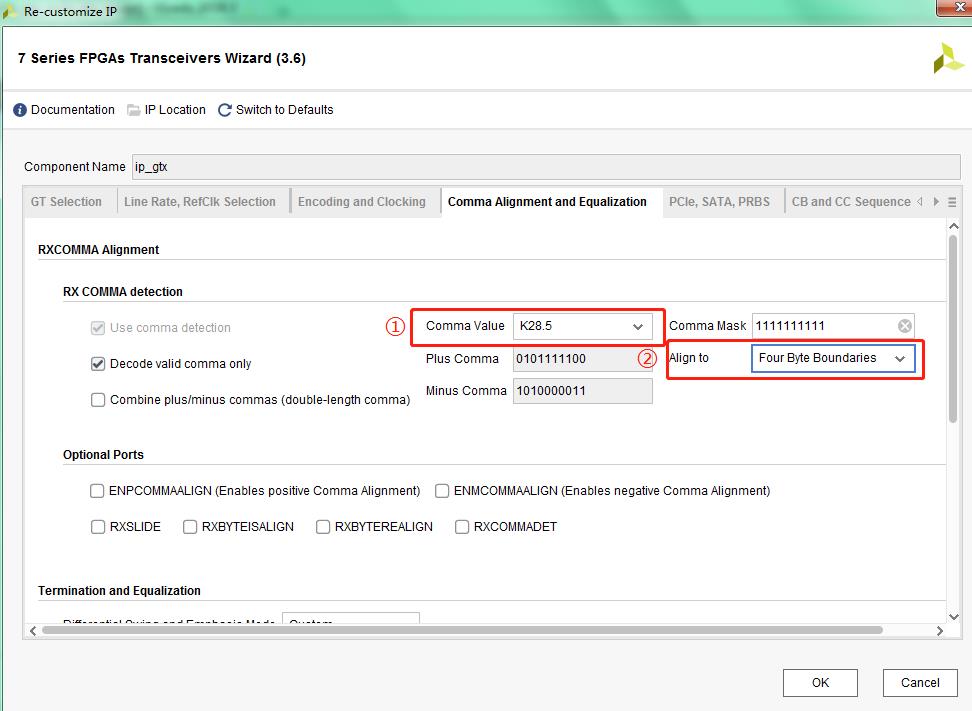

1.4第四页配置

①: 一般选用K28.5,对应过来就是0xBC。

②: 对齐方式,因为我们选择的数据位宽是32bit,所有这里选择4字节对齐。

其他的都不用选,毕竟“丐版”~

1.5第五页配置

PCIe,我们用不上,不选择,不使能。

1.6第六页配置

通道绑定,我们也不使用。不选择。

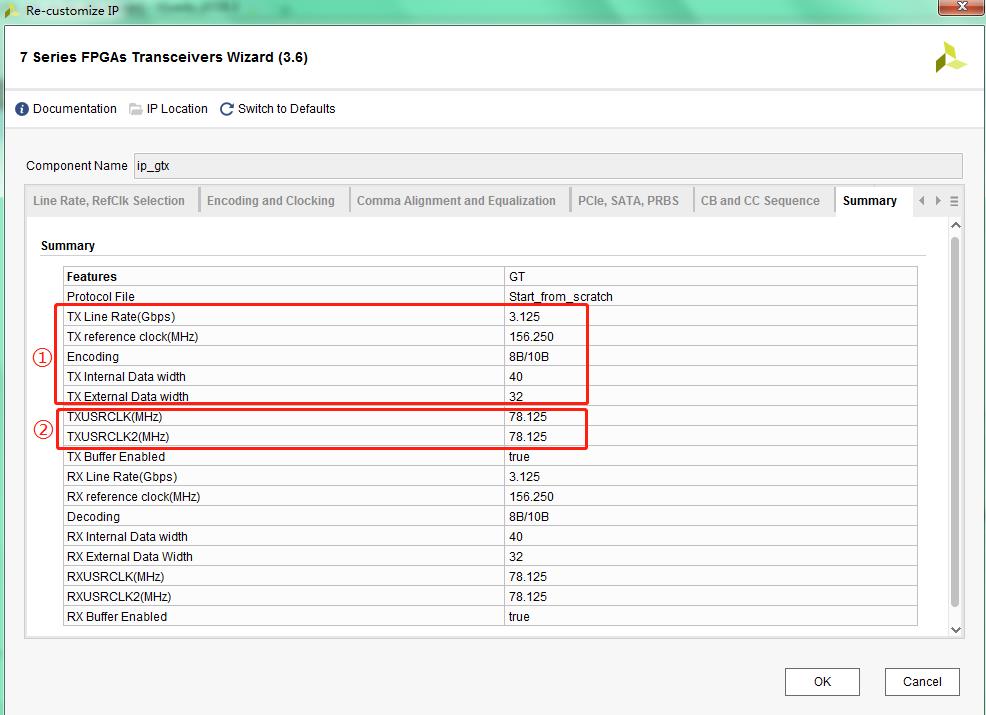

1.7第七页总结

①:是我们刚刚配置选择的信息:线速、参考时钟、编码方式,位宽等;

②:注意两个时钟TXUSRCLK 、 TXUSRCLK2,怎么来的呢?

TXUSRCLK = 78.125Mhz怎么计算来的呢?

TXUSRCLK 与 TXUSRCLK2有一定的比率关系,具体内容请看系列文章(2)GTX时钟篇

检查没有问题,就点击OK,生成GTX。

二、GTX 接口信号介绍

2.1 TX端口

| 端口名称 | 方向 | 时钟域 | 描述 |

| TXCHARDIPMODE | 输入 | TXUSRCLK2 | 当8B/10B没有使用时,用来扩展DATA的位宽。 |

| TXCHARDIPVAL | 输入 | TXUSRCLK2 | 当8B/10B没有使用时,用来扩展DATA的位宽。 |

| TXDATA | 输入 | TXUSRCLK2 | 发送数据位宽,由TX_DATA_WIDTH决定 |

| TXUSRCLK | 输入 | Clock | 驱动内部PCS数据路径的时钟 |

| TXUSRCLK2 | 输入 | Clock | 同步逻辑数据和发送端的时钟。与TXUSRCLK上升沿对齐。 |

TX端口属性:

| 属性 | 类型 | 描述 |

| TX_DATA_WIDTH | 整数型 | 决定TXDATA的位宽。当使用8B/10B编码时,位宽必须为20,40,80; 有效设置为:16,20,32,40,64,80 |

| TX_INT_DATAWIDTH | 整数型 | 控制内部数据的位宽: 0:2-byte 内部数据路径模式 1:4-byte模式;当线速超过6.6Gb/s时,必须设为1. |

2.2 RX端口

| 端口 | 方向 | 时钟域 | 描述 |

| RXDISPERR | 输出 | RXUSRCLK2 | 当8B/10B不用时,用来扩展数据位宽。 |

| RXCHARISK | 输出 | RXUSRCLK2 | 表示接收的数据是K码; 当8B/10B不用时,用来扩展数据位宽。 |

| RXDATA | 输出 | RXUSRCLK2 | 接收到的数据。 |

| RXUSRCLK | 输入 | Clock | 给到RX PCS的内部时钟。 |

| RXUSRCLK2 | 输入 | Clock | FPGA逻辑与RX接口的同步时钟。 |

RX端口属性:

| 属性 | 类型 | 描述 |

| RX_DATA_WIDTH | 整型 | 决定RXDATA的位宽,概念基本同TX |

| RX_INT_DATAWIDTH | 整型 | 控制内部数据路径的位宽: 0: 2-byte 1: 4byte,当线速超过6.6Gb/s时,必须设为1. |

后记

是不是还是挺简单的,下一篇我们将用最简单的姿势将GTX用起来~

以上是关于Xilinx FPGA平台GTX简易使用教程GTX IP核配置教程的主要内容,如果未能解决你的问题,请参考以下文章