chap4组合逻辑电路

Posted 临风而眠

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了chap4组合逻辑电路相关的知识,希望对你有一定的参考价值。

chap4 组合逻辑电路

文章目录

§4.1概述

什么样的输入决定什么样的输出

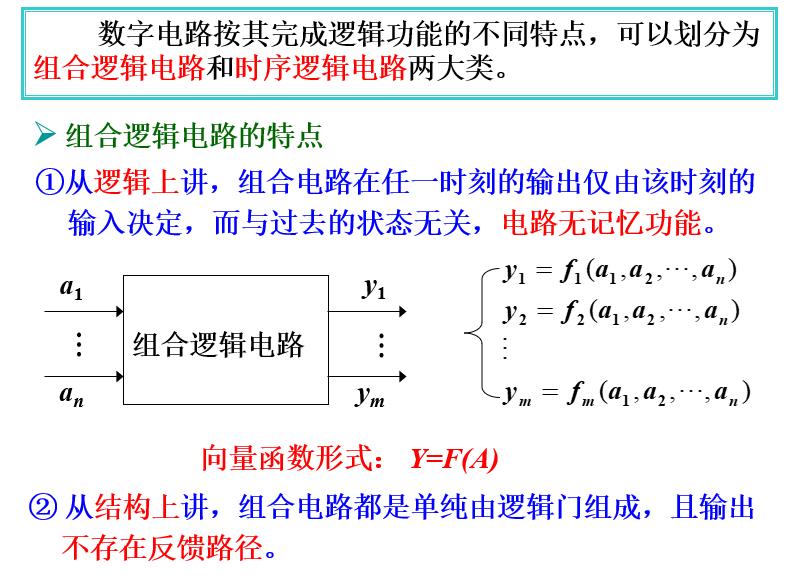

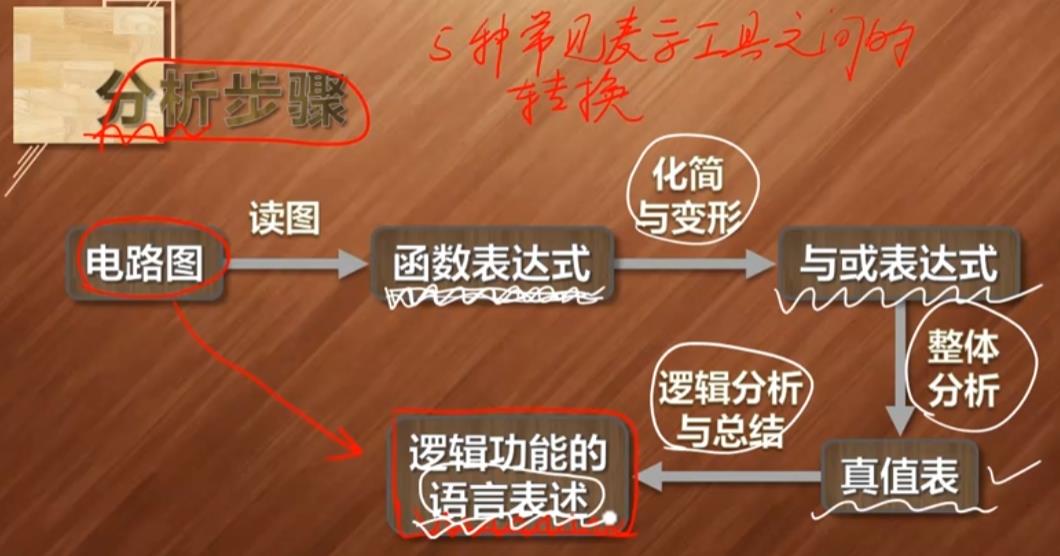

§4.2 组合逻辑电路分析设计方法

-

分析步骤

-

设计步骤

-

设计与分析

§4.3 常用的组合逻辑电路

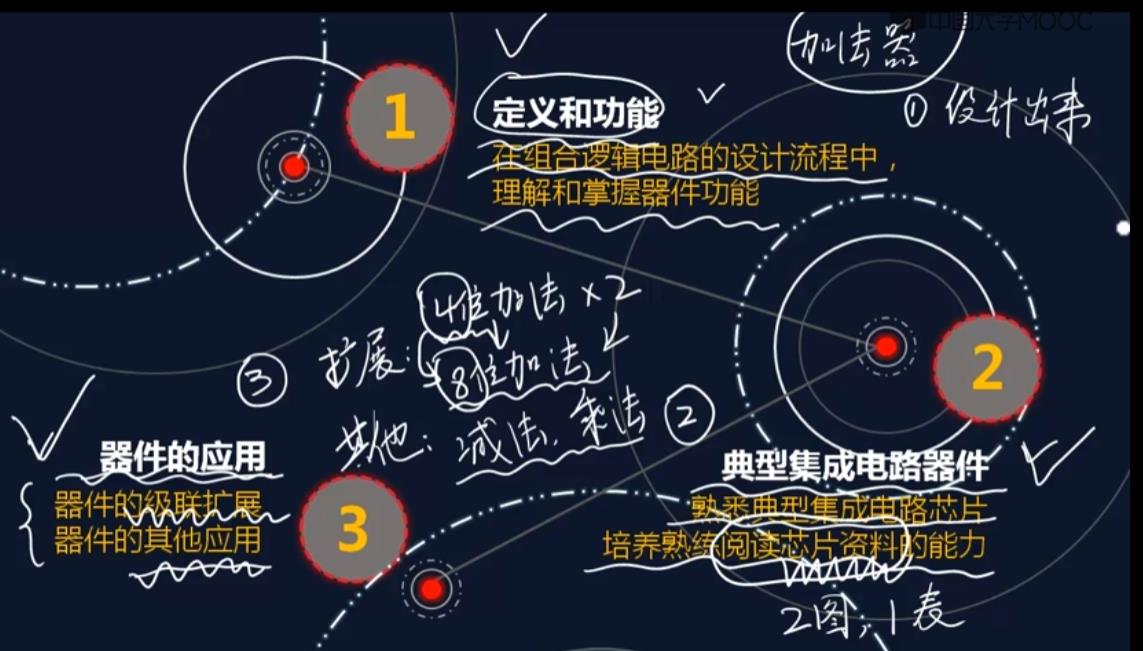

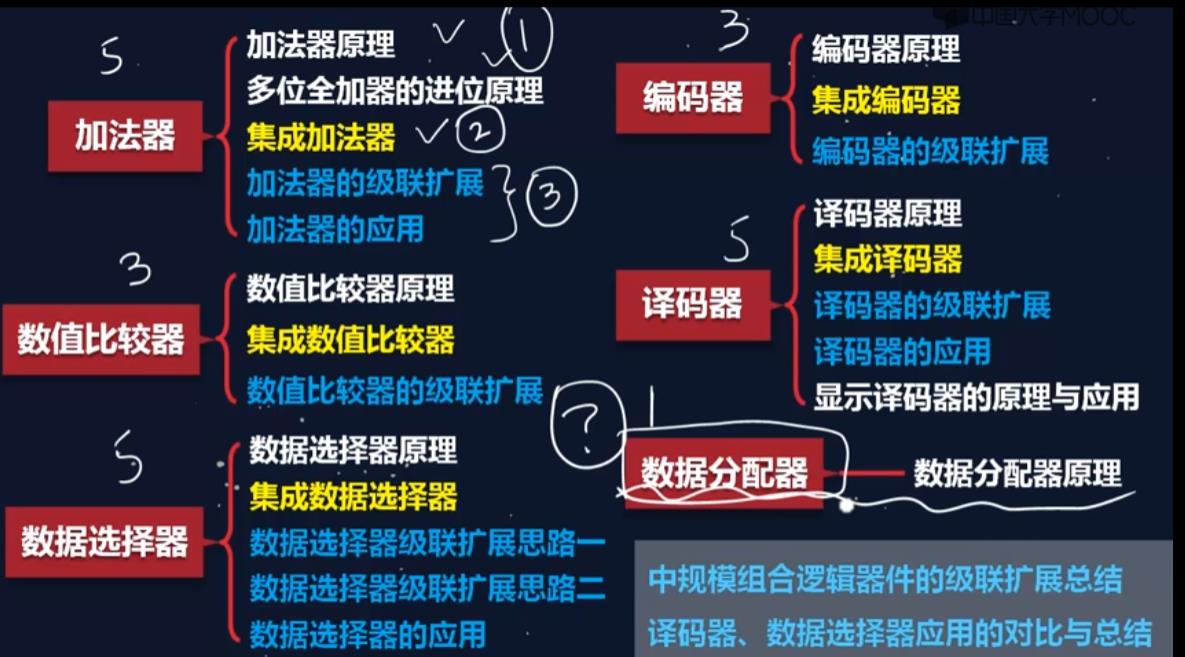

知识结构

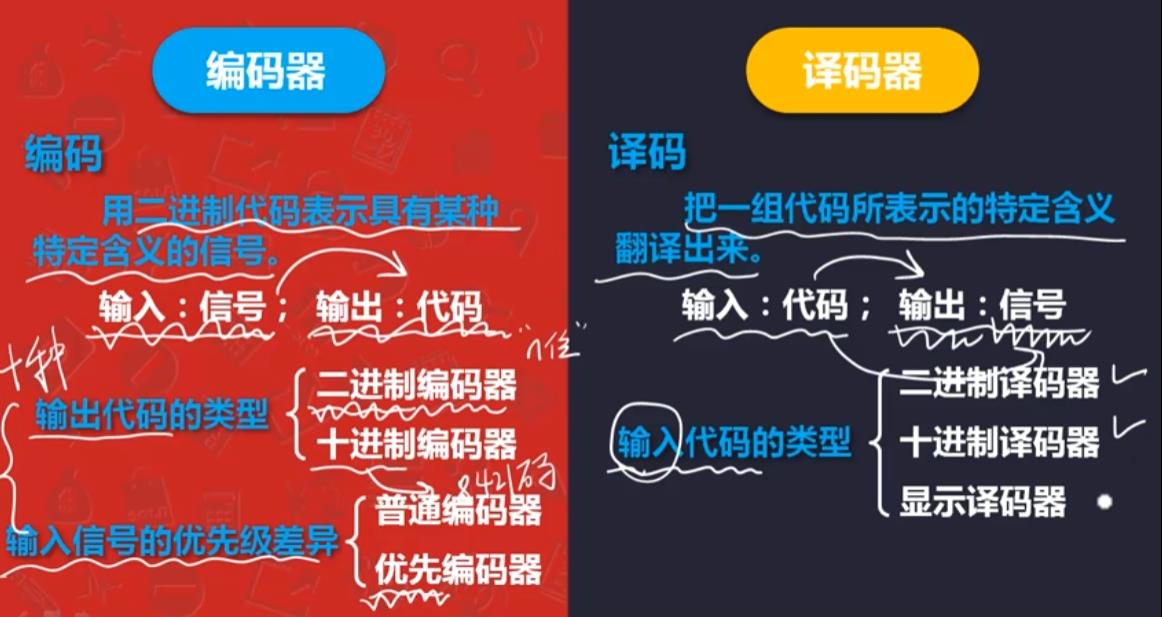

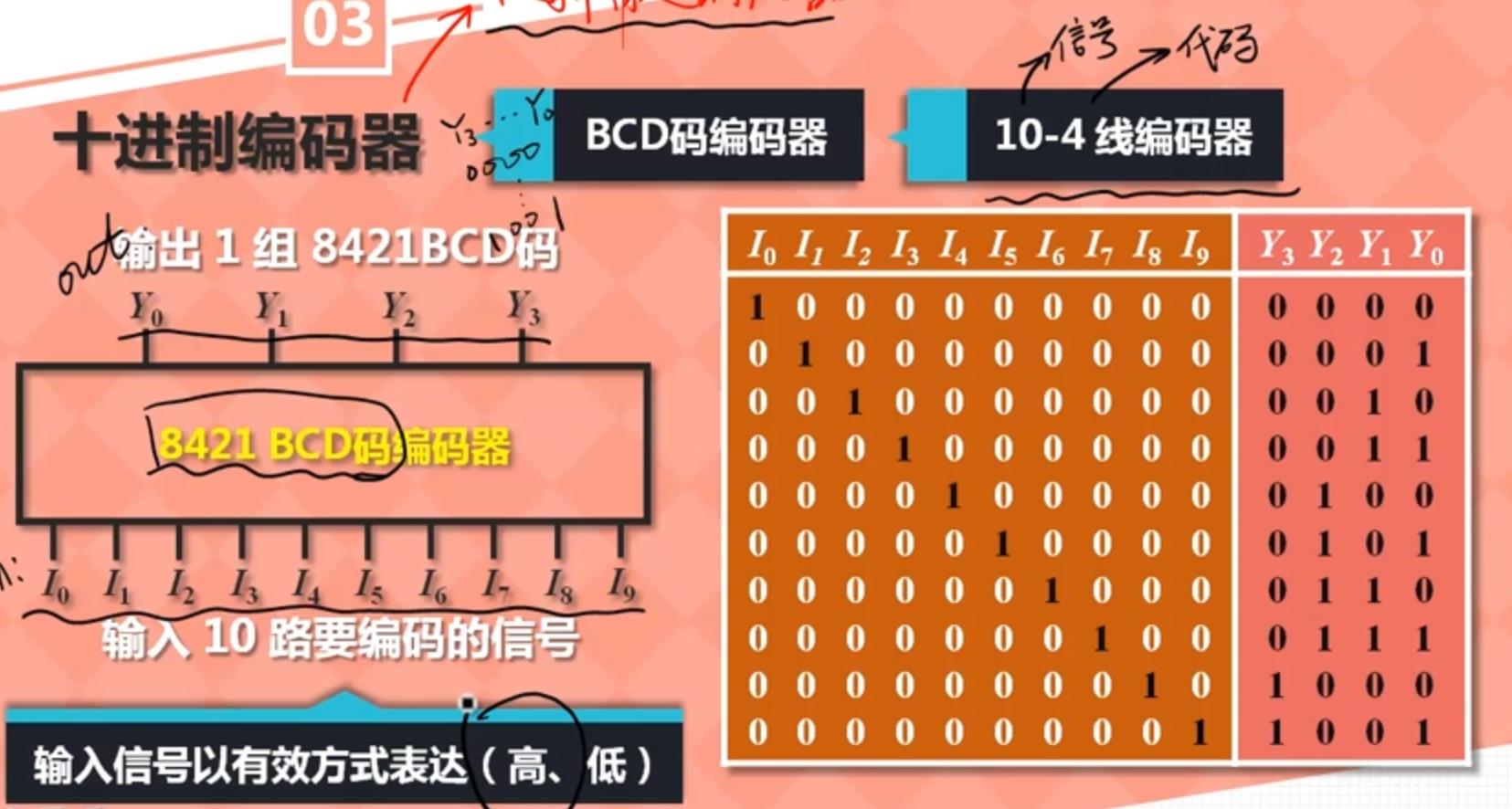

一.编码器

-

编码

- 用二进制代码表示具有某种特定含义的信号

- 输入:信号

- 输出:代码

- 编码器原理

- 信号入,代码出

- 用二进制代码表示具有某种特定含义的信号

-

译码

- 把一组代码所表示的特定含义翻译出来

- 输入:代码

- 输出:信号

- 把一组代码所表示的特定含义翻译出来

-

编码器分类

- 按输出代码的类型分

- 二进制编码器

- 十进制编码器

- 按输入信号的优先级差异分

- 普通编码器

- 优先编码器

- 按输出代码的类型分

-

实现编码操作的电路就是编码器

1.普通编码器

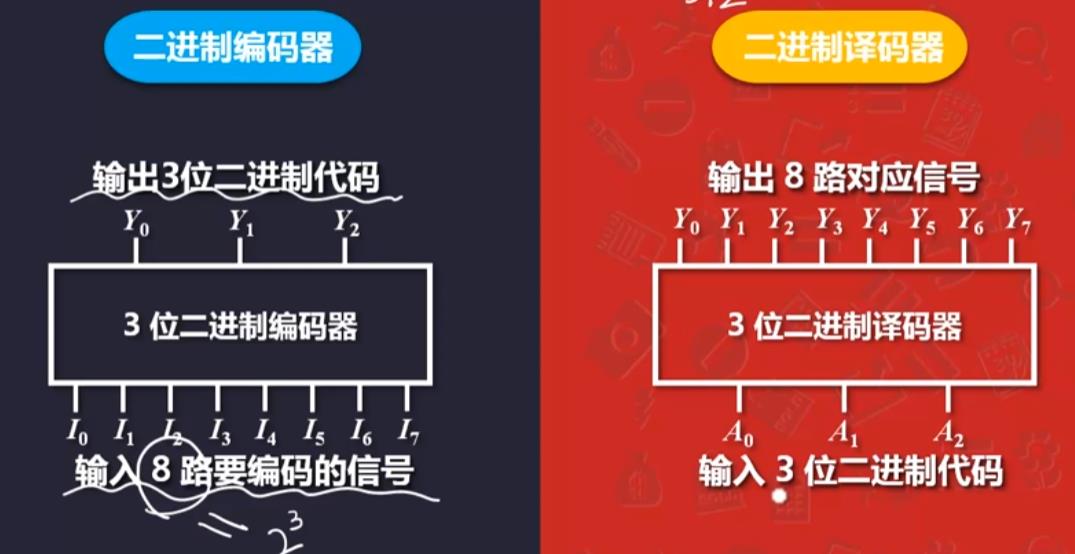

二进制普通编码器

-

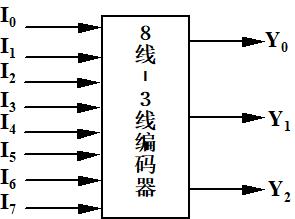

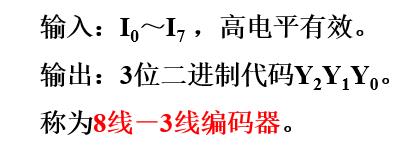

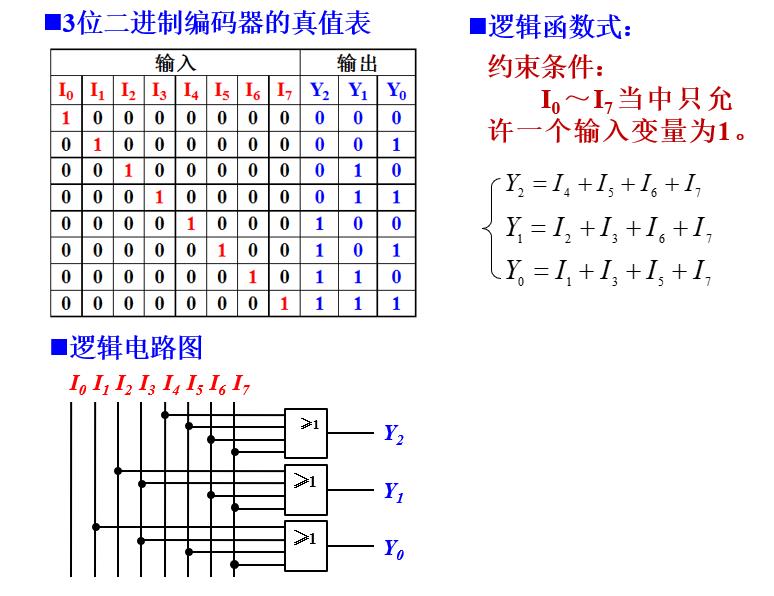

例:三位二进制普通编码器(又称为8-3线编码器)

-

如上图编码表所示, 输入信号是以高有效方式表达的,且输入信号相互排斥

-

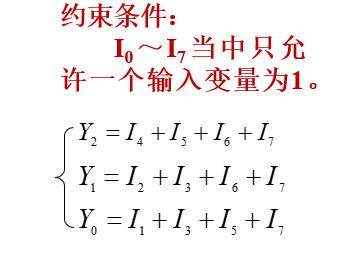

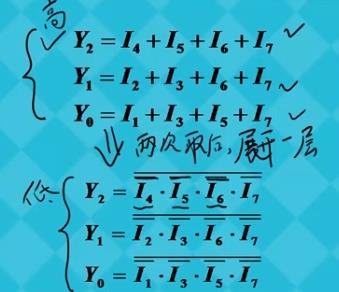

逻辑函数式

若要将输入信号以低有效方式表达,可以把逻辑表达式转换一下:

-

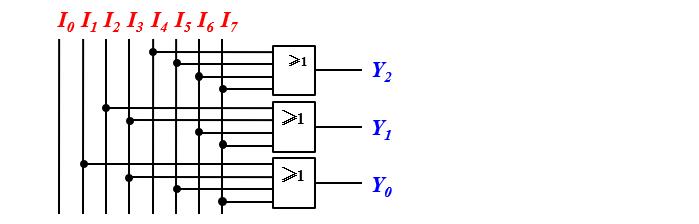

逻辑电路图

-

因为只允许一个有效的,所以多于一个的时候会出问题,解决办法就是👇

十进制普通编码器

2.优先编码器

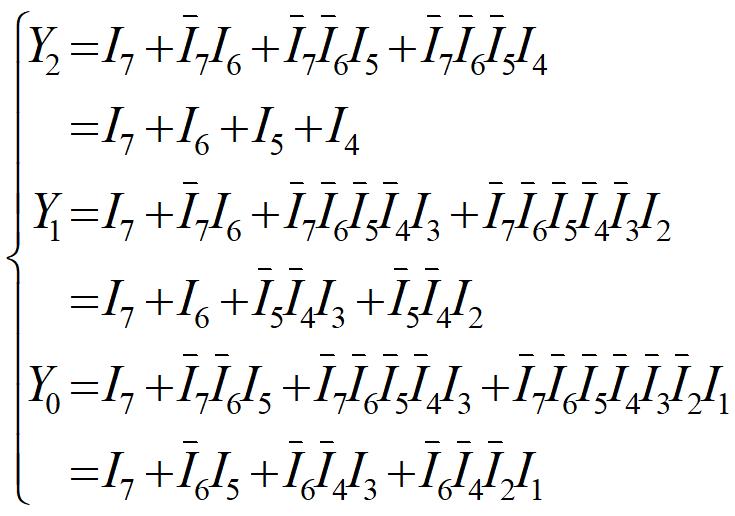

二进制优先编码器

- 逻辑函数式

十进制优先编码器

3.常用的集成编码器

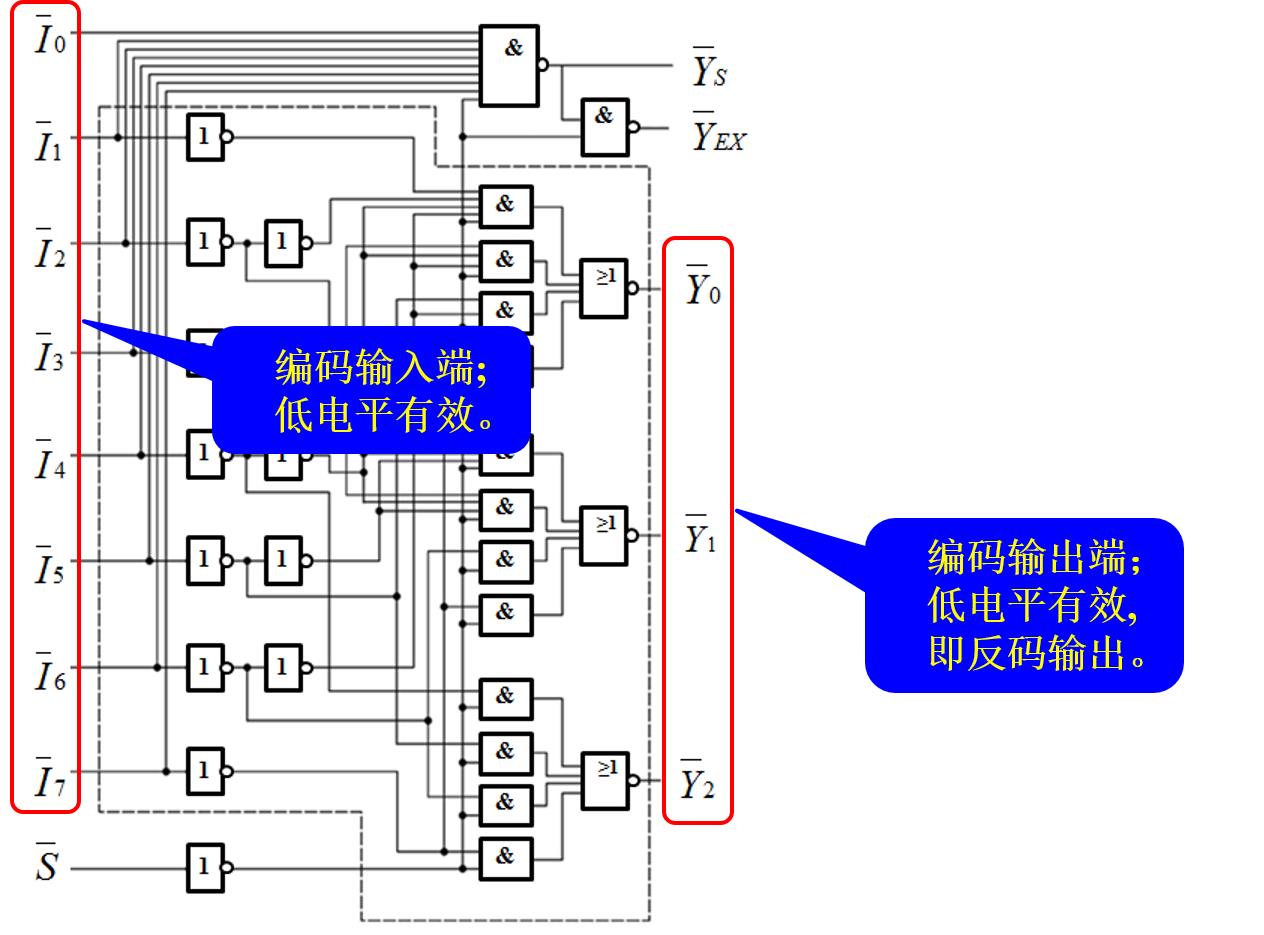

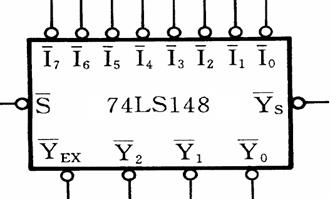

集成8线-3线优先编码器74LS148

-

逻辑电路图

-

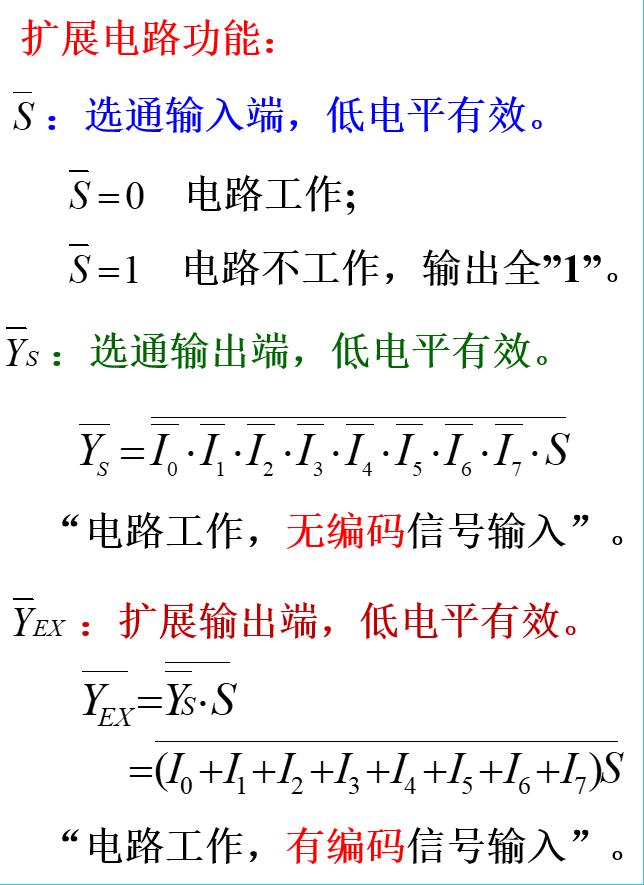

扩展电路功能

-

-

芯片封装图

-

功能示意图

-

功能表

S ‾ \\overline{S} S是低有效选通控制端,输入为1时, 不满足低有效

-

编码功能

-

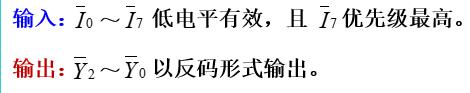

扩展输出的状态及含义

-

-

集成电路资料的阅读

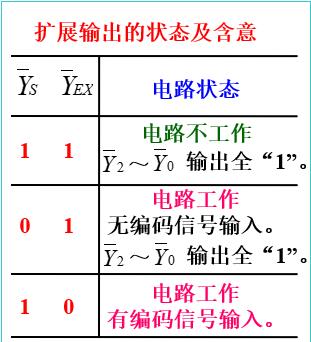

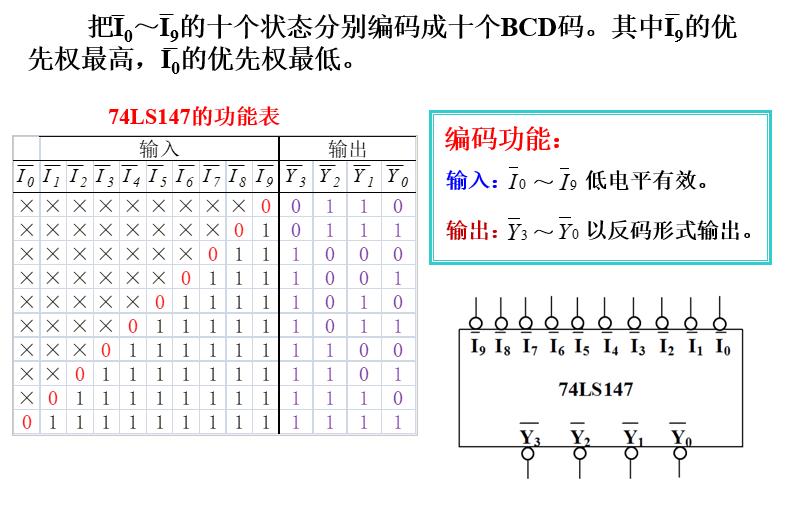

二-十进制(BCD)优先编码器74LS147

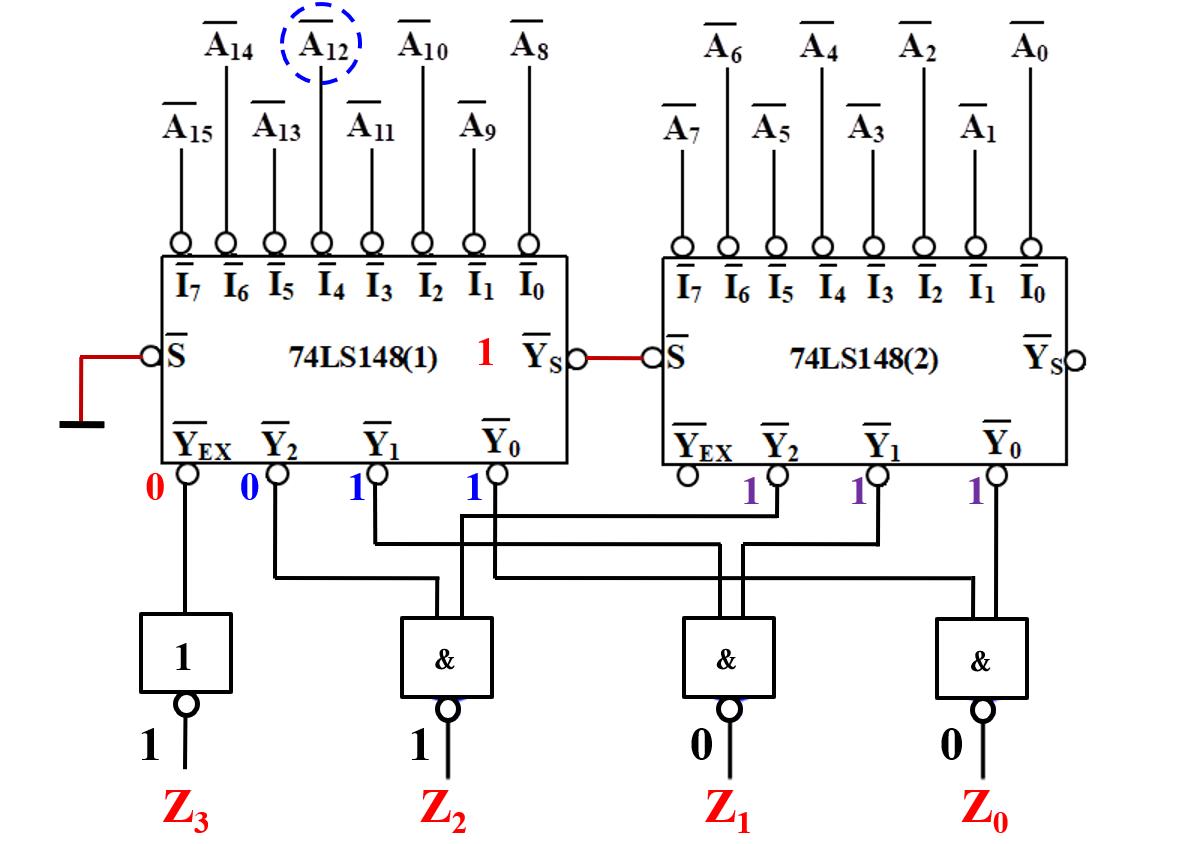

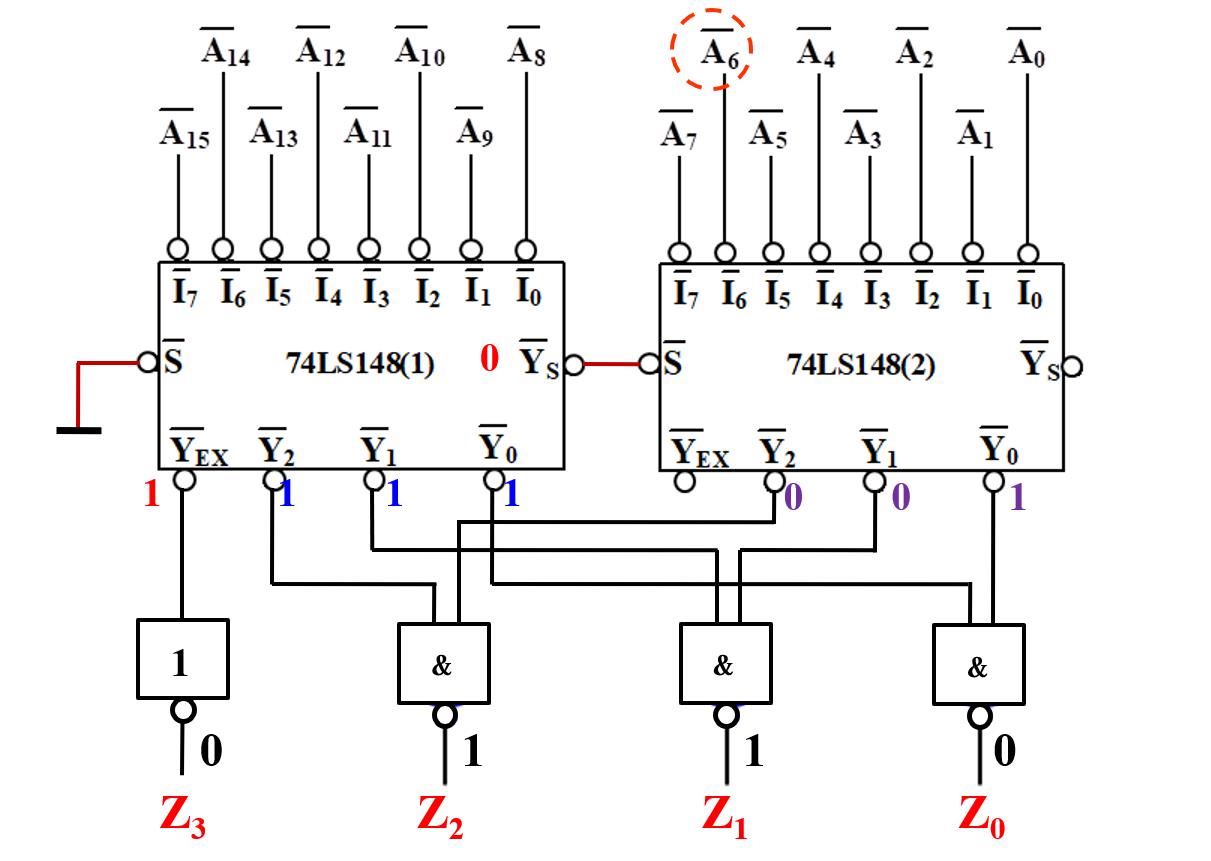

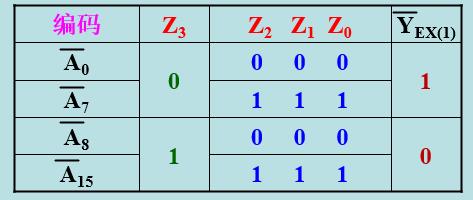

4.编码器级联扩展

-

例

使用74LS148组成16-4线优先编码器

-

-

74LS148(1)无编码信号输入时,74LS148(2)才选通

-

二.译码器

译码器 :输入代码 输出信号

1.二进制译码器

设二进制译码器的输入端为n个,则输出端为 2 n 2^n 2n个,且对应于输入代码的每一种状态, 2 n 2^n 2n个输出中只有一个有效(为1或为0),其余全无效(为0或为1)

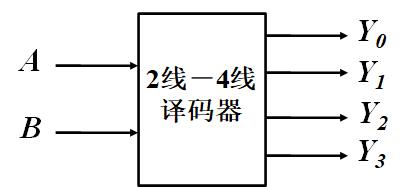

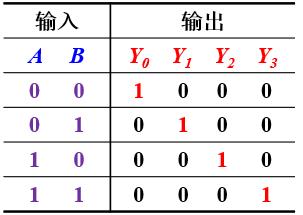

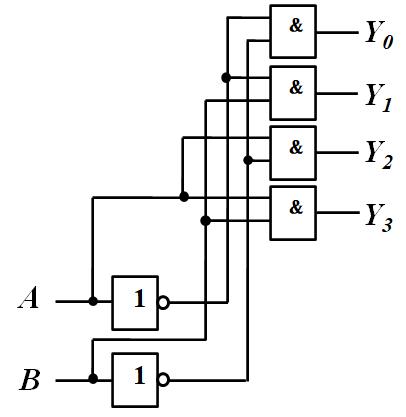

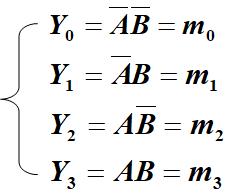

2线-4线译码器

-

真值表

-

逻辑图

-

逻辑函数式

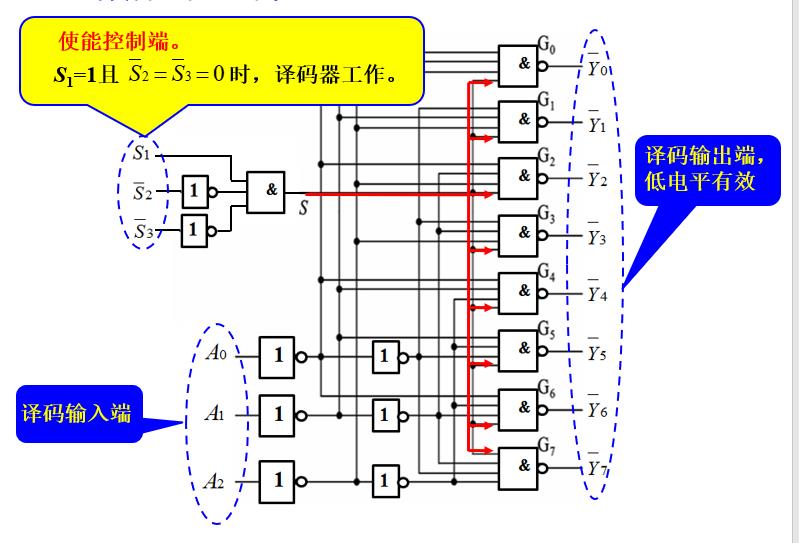

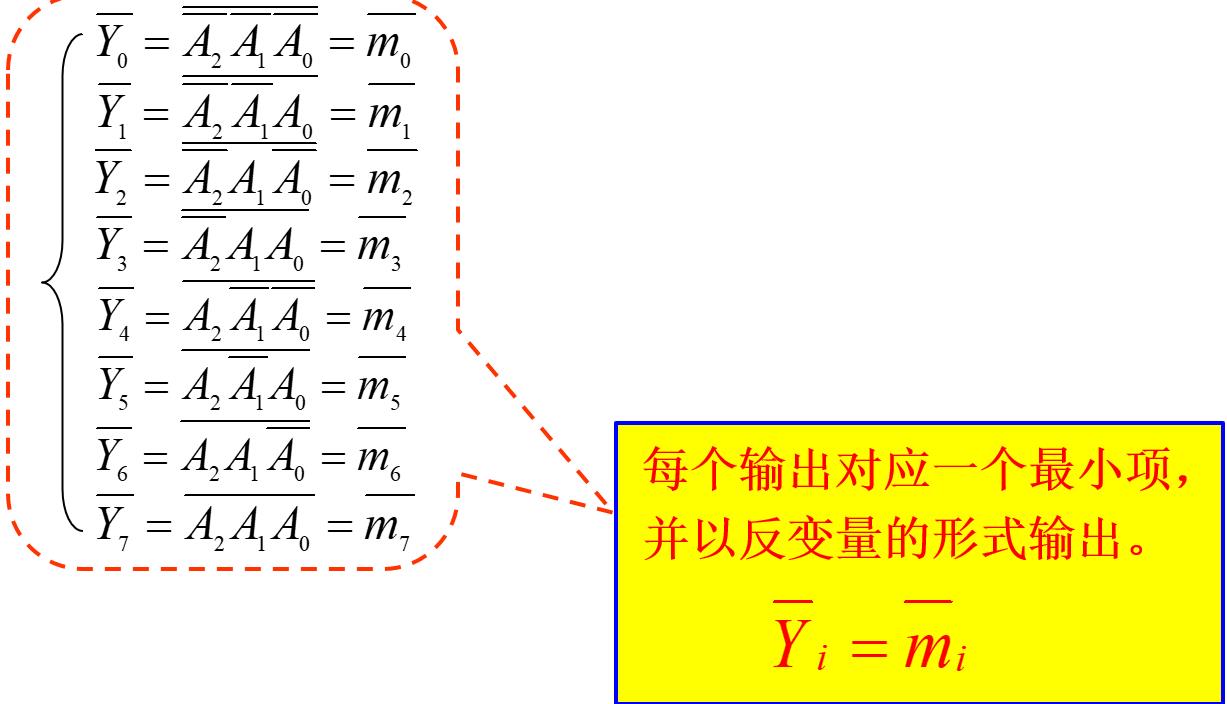

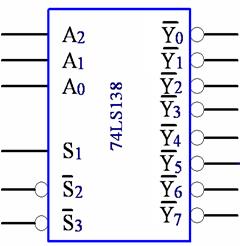

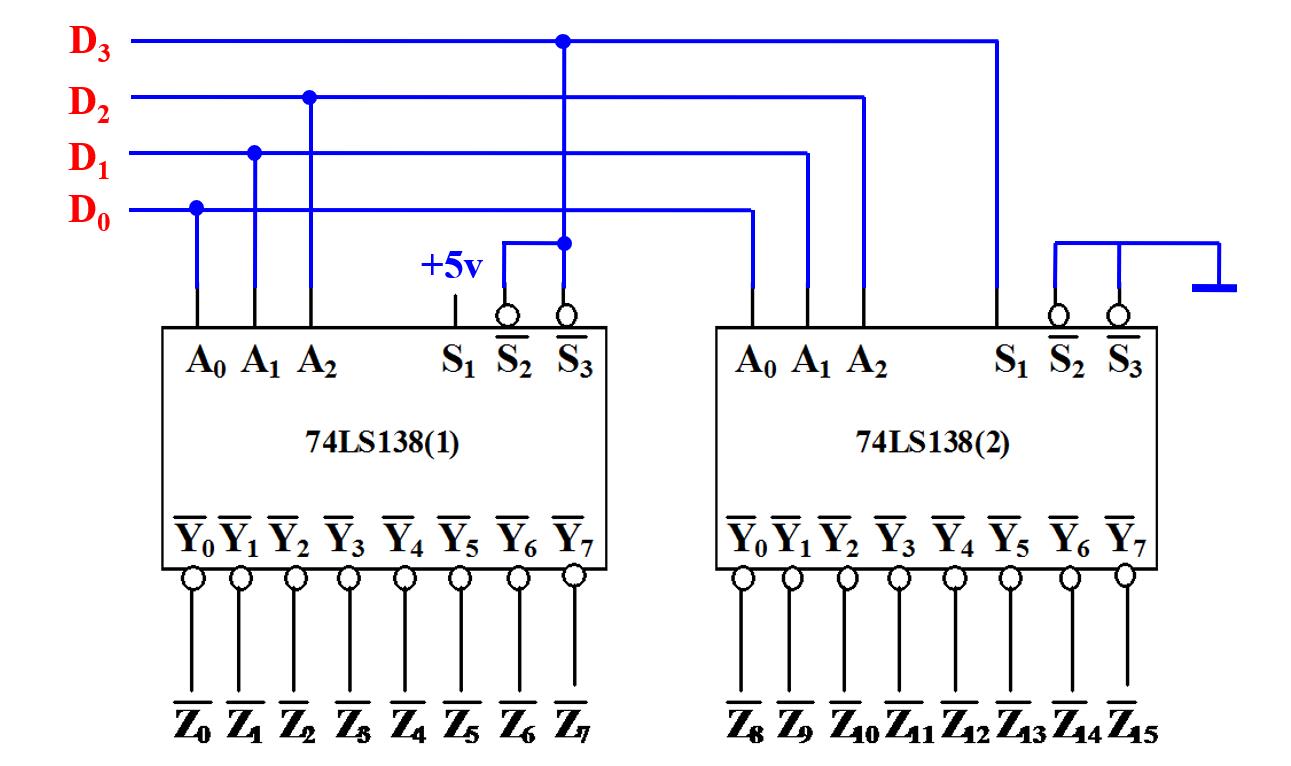

集成3线-8线译码器74LS138

-

功能表

-

输出逻辑表达式

-

功能示意图

-

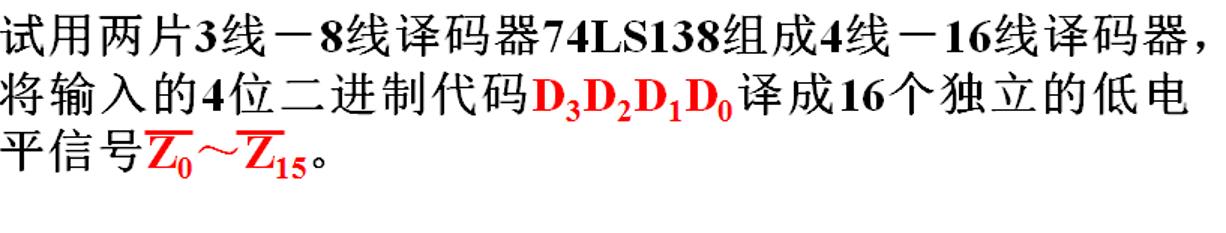

例

思考:5线-32线

D 4 D 3 D_4D_3 D4D3 的00、01、10、11四种组合分别使四片使能

思考:8片 74LS138构成6线-64线译码器

D 5 D 4 D 3 D_5D_4D_3 D5D4D3 的8种组合分别使8片使能

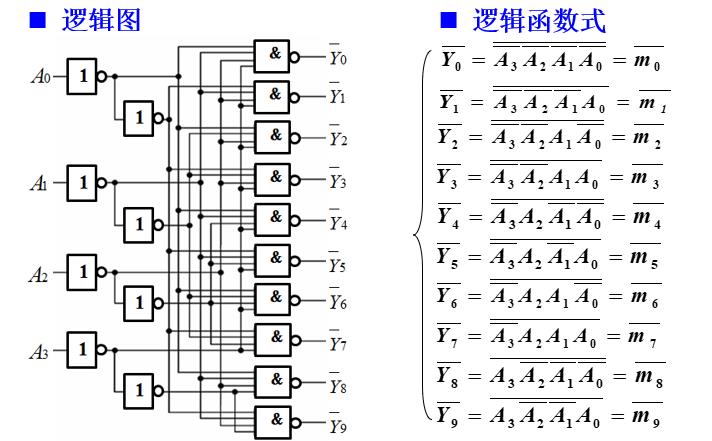

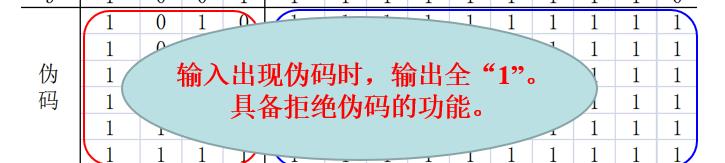

2.二-十进制译码器

-

二-十进制译码器也称为BCD译码器

-

功能是将输入的4位BCD码译成10个高、低电平输出信号,因此也叫4线-10线译码器

-

逻辑图和逻辑函数式

-

-

真值表

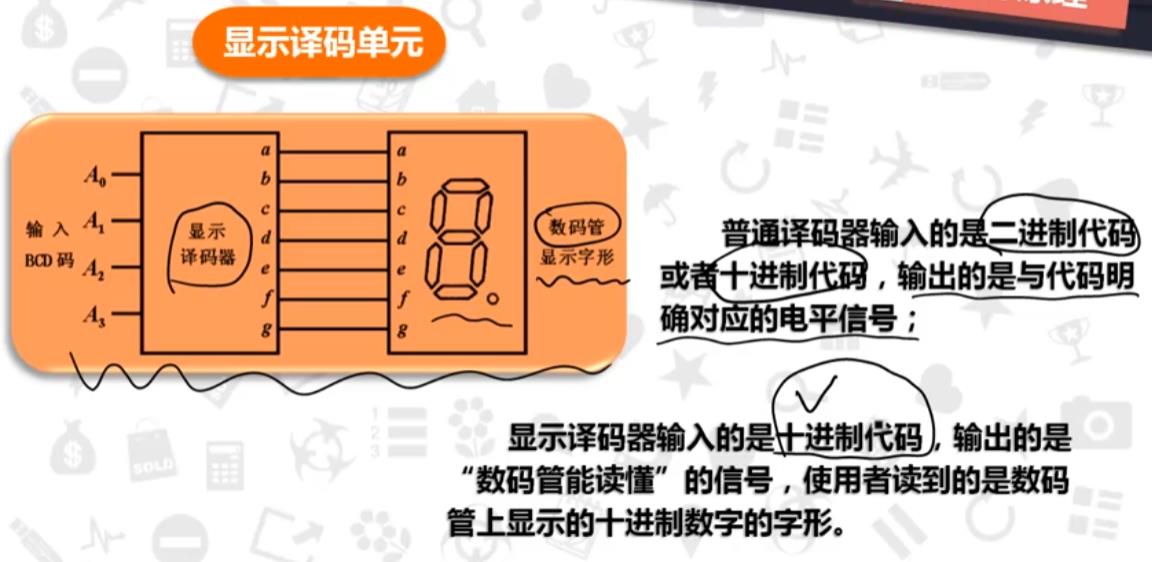

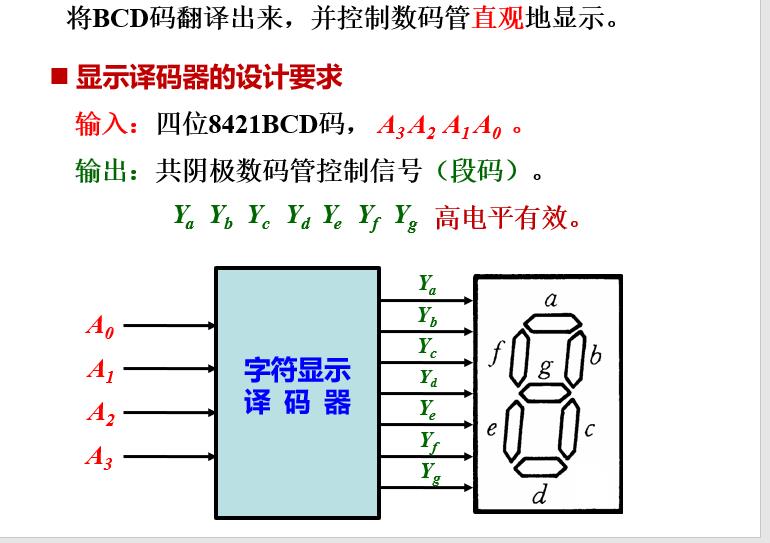

3.显示译码器

- 用二进制代码翻译成人们习惯的形式,并直观地显示出来地电路,称为显示译码器

-

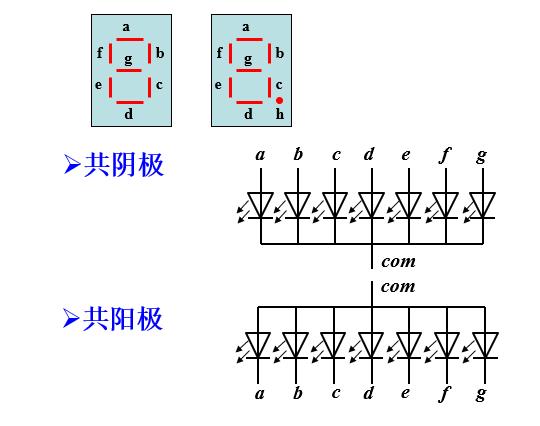

LED显示器-数码管

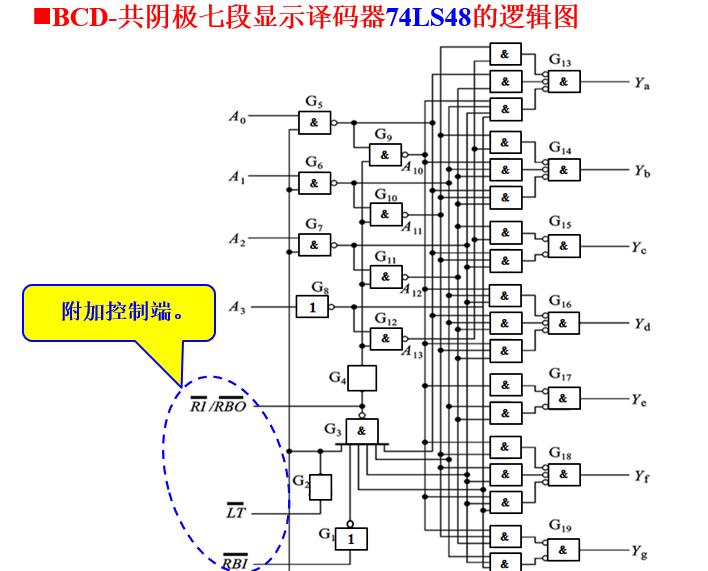

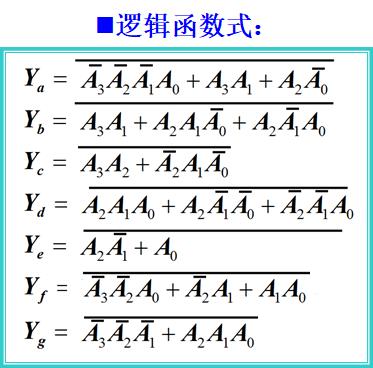

BCD-共阴极七段字符显示译码器

-

设计要求

-

真值表

-

逻辑图

-

逻辑函数式

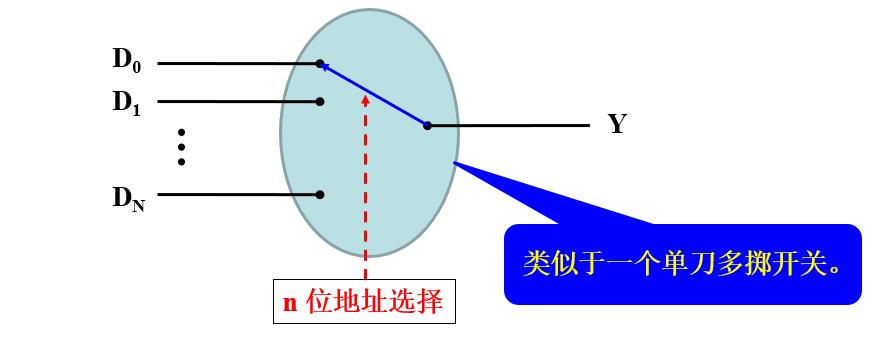

三.数据选择器 (多路选择器,多路开关)

寻址、传输两步走

-

数据选择器又称多路选择器

- 多路输入、一路输出

- 每次在地址输入的控制下,从多路输入数据中选择一路输出

-

先寻址,再输出

- 输入数据的路数N与地址位数n之间满足: N = 2 n N=2^n N=2n

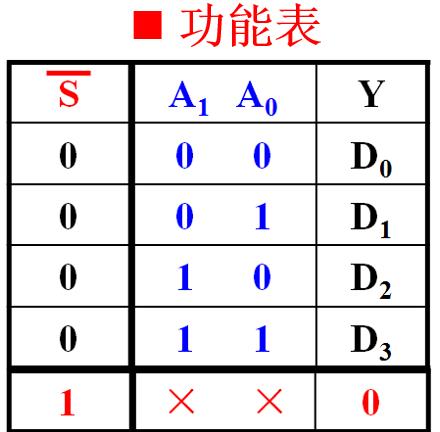

1.集成双4选1数据选择器74HC153

-

工作原理

-

功能表

-

逻辑函数式

-

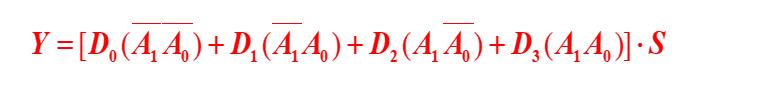

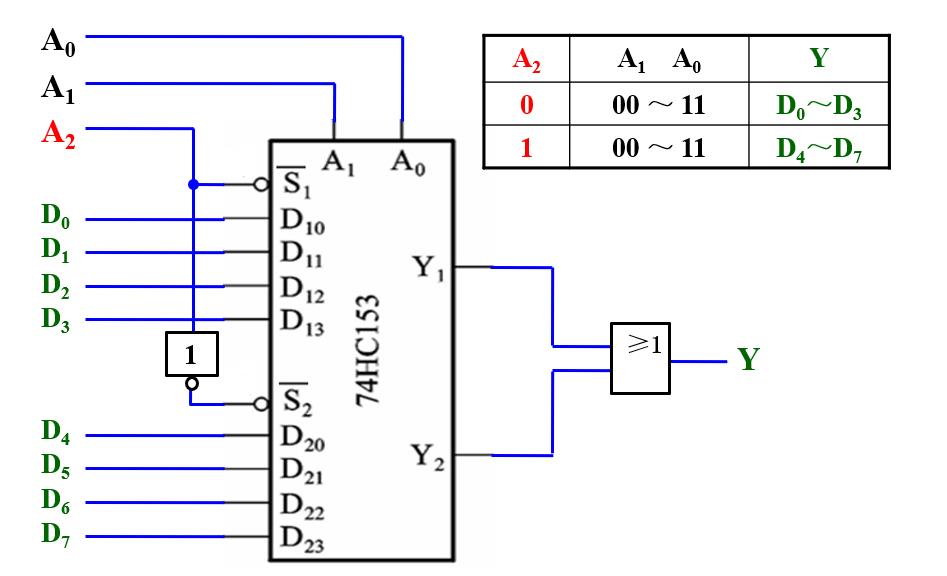

例

用一片双4选1数据选择器74HC153组成一个8选1数据选择器

- 思路

- 先片选,再片内选

- 低两位输入地址共用

- 控制端反向共接,生成最高位地址作为片选信号,区分两片4选1的工作区

- 思路

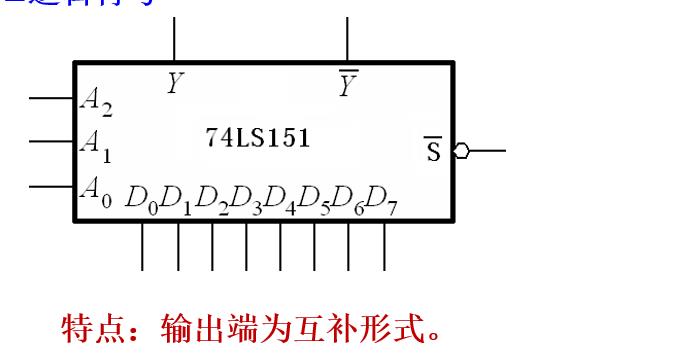

2. 集成8选1数据选择器74LS151

-

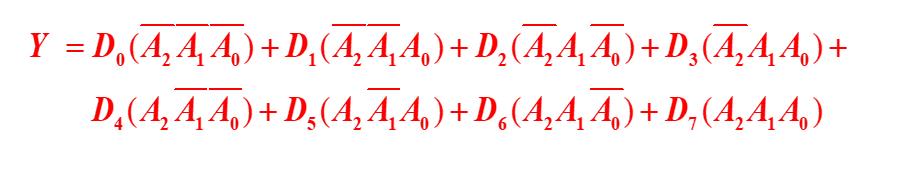

逻辑函数式

-

逻辑符号

四.加法器

1.一位加法器

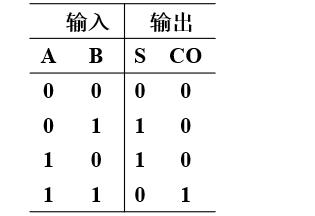

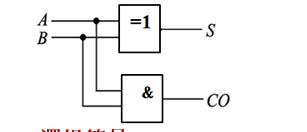

半加器

不考虑低位向本位的进位的加法。

但是,要考虑本位相加后,给高位的进位。

-

是二输入二输出

- 输入变量:A、B

- 输出变量:

- S: 相加后本位的结果

- CO: 本位向高位的进位

-

半加器真值表

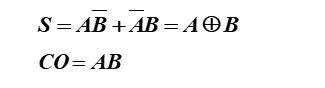

-

逻辑函数式

-

逻辑图

-

逻辑符号

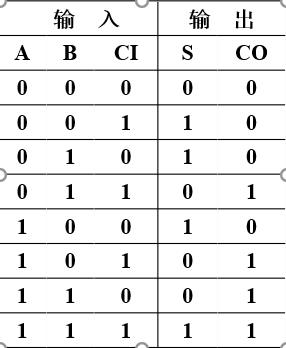

全加器

要考虑低位向本位的进位的加法,也同样要考虑到本位相加后,向高位的进位

-

是三输入两输出

- 输入

- 相加的两个1位二进制数 A、B

- CI : 低位的进位

- 输出

- S: 相加后本位的结果

- CO: 本位向高位的进位

- 输入

-

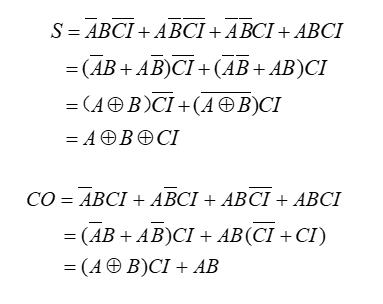

全加器真值表

-

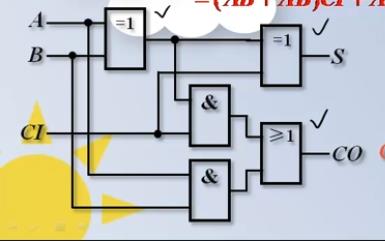

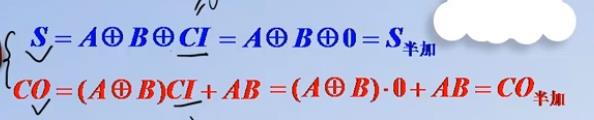

逻辑函数式

-

逻辑图

-

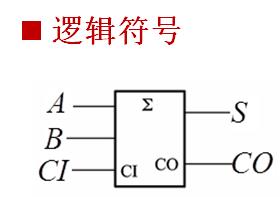

逻辑符号

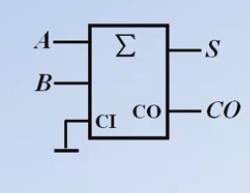

用全加器实现半加器

-

-

接地

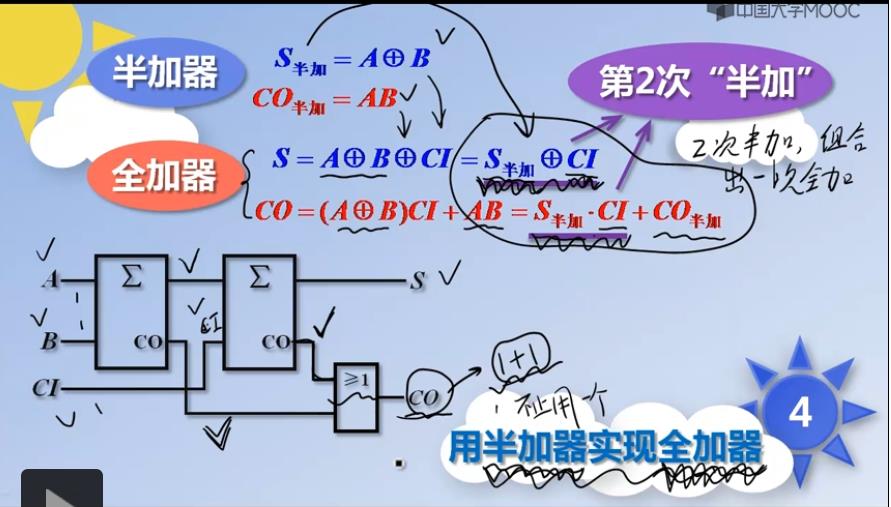

用半加器实现全加器

-

两次半加

2.多位加法器

串行进位加法器

由低到高,一位一位加

-

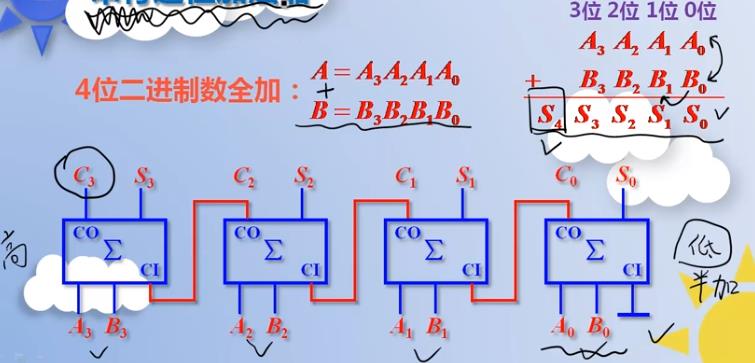

4以位串行进位加法器为例

-

特点

进位信号由低到高逐级传递,每一位的相加结果都要等到低位进位产生以后才能建立,传输延迟时间长

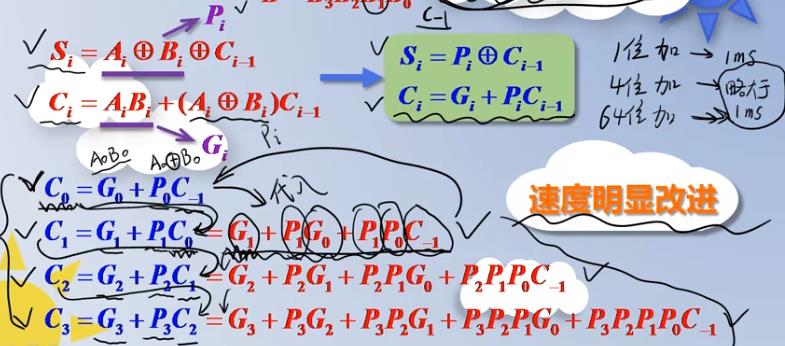

超前进位加法器

-

基本思想

本位两个加数相加的同时也已获得低位的进位 C O i − 1 CO_{i-1} COi−1,则一次就可以完成多位加法运算

其实就是数学上代入

-

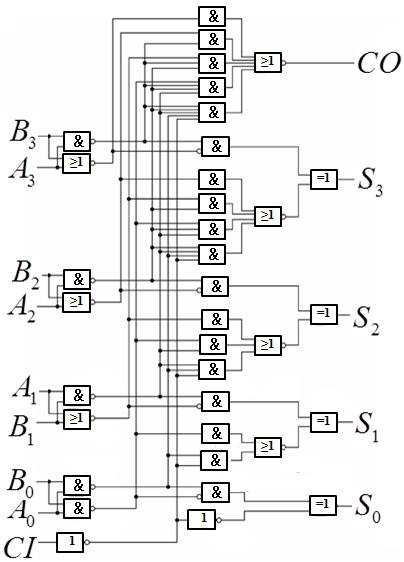

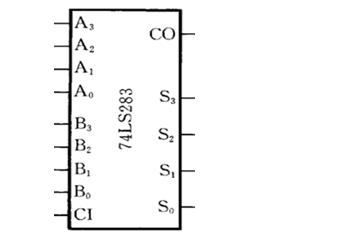

4位超前进位加法器74LS283

- 逻辑图

-

优点

工作速度快,每位的和及最后的进位基本同时产生

-

缺点

电路复杂

-

逻辑符号

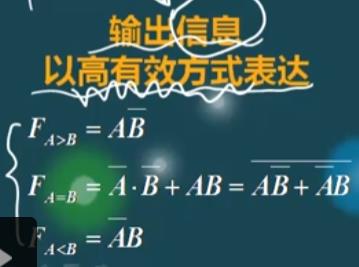

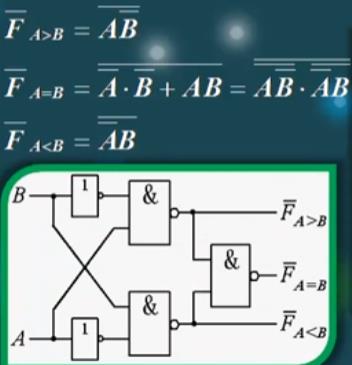

五.数值比较器

- 用来将两个同样位数的二进制数A、B进行比较,并能判别其大小关系的逻辑器件,叫做数值比较器

- 两个数相比,一个结果,三种可能

- A>B ,A=B ,A<B

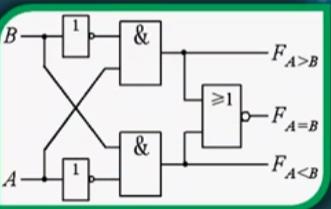

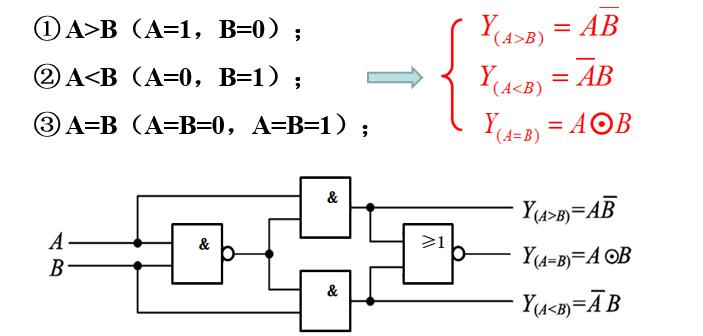

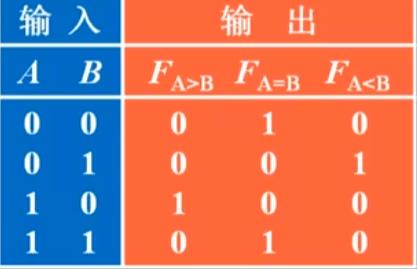

1.一位数值比较器

上表是输出信息以高有效方式表达(为1表示该端出现,为0表示该端不出现)

输出信息也可以低有效方式表达,加上非号

2.多位数值比较器

-

比较两个多位数A和B,需从高向低逐位比较

-

以4位二进制数比较器为例

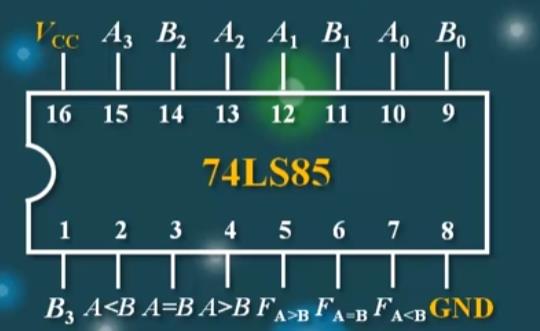

集成4位数值比较器74LS85

-

芯片封装图

-

功能示意图

-

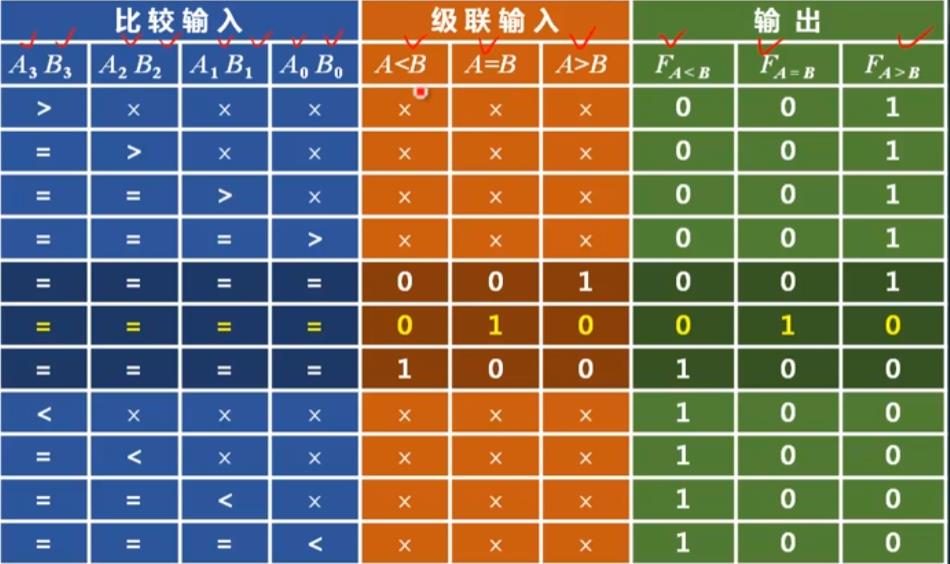

功能表

输出信息由高有效方式表达

输入端打×的地方表示输入端取值任意

两个四位二进制数,由高到低对位比较,4位比较结果均相等时,输出结果由级联输入端决定

-

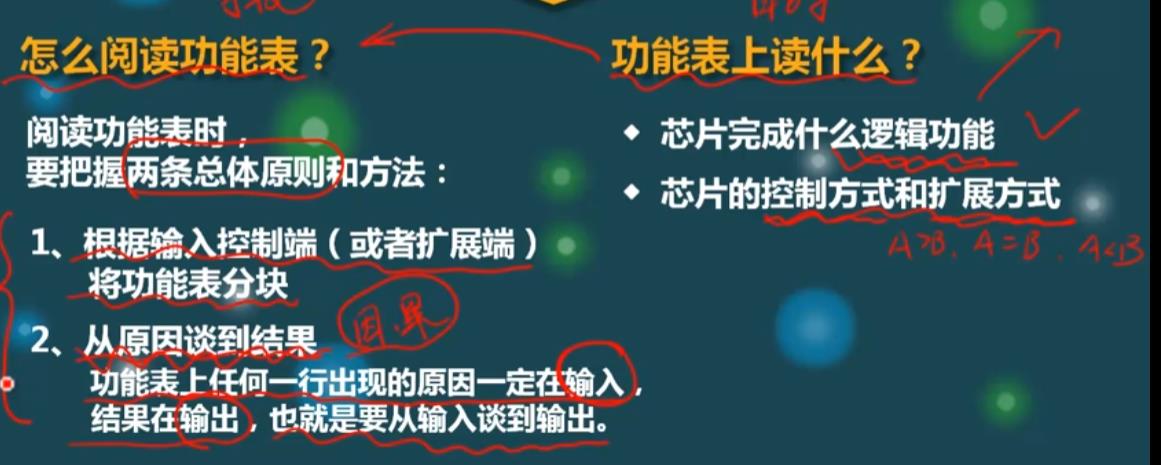

如何阅读功能表

-

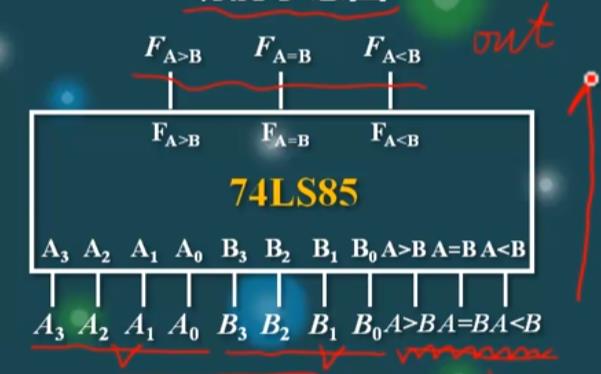

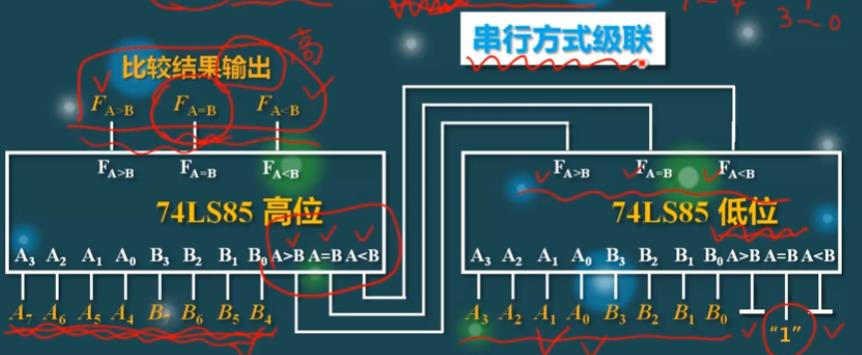

数值比较器的级联扩展

-

例:用两片74LS85组成8位数值比较器

-

注意点

§4.5 组合逻辑电路的竞争和冒险

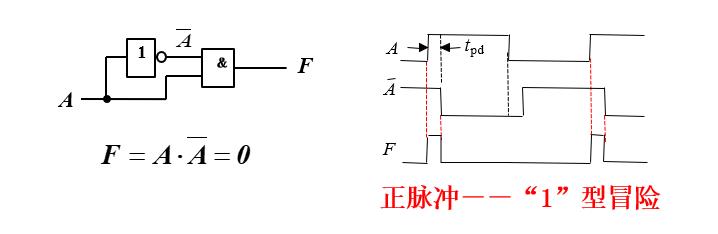

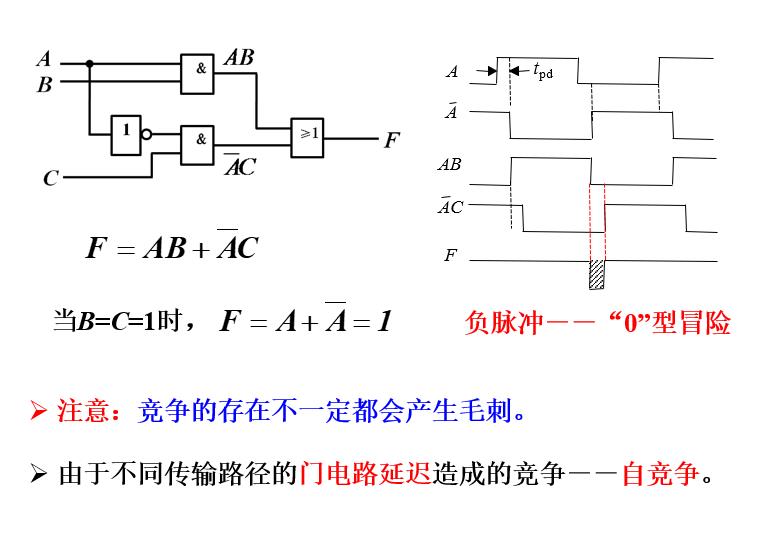

一.竞争与冒险现象

-

在组合电路中,某一输入变量经不同途径传输后,由于门电路的传输延迟时间不同,则到达电路中某一会和点的时间会有先后,此现象称为竞争

-

如

因为经过反相器有延迟 A A A和 A ‾ \\overline{A} A可能出现同时为1的情况,

冒着可能产生尖脉冲的风险

-

如

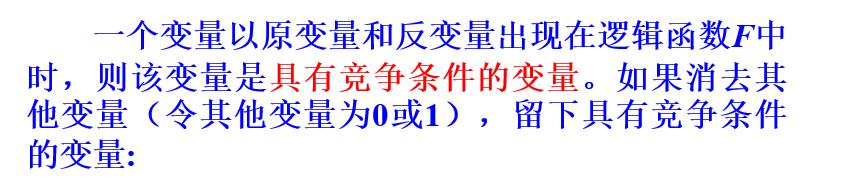

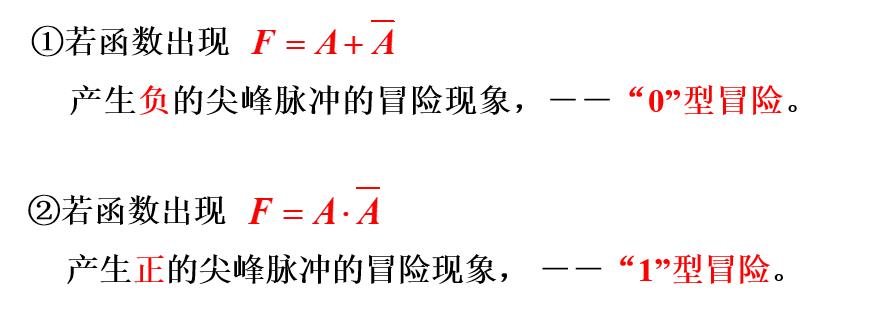

二.竞争-冒险现象的检查方法

1.代数识别法

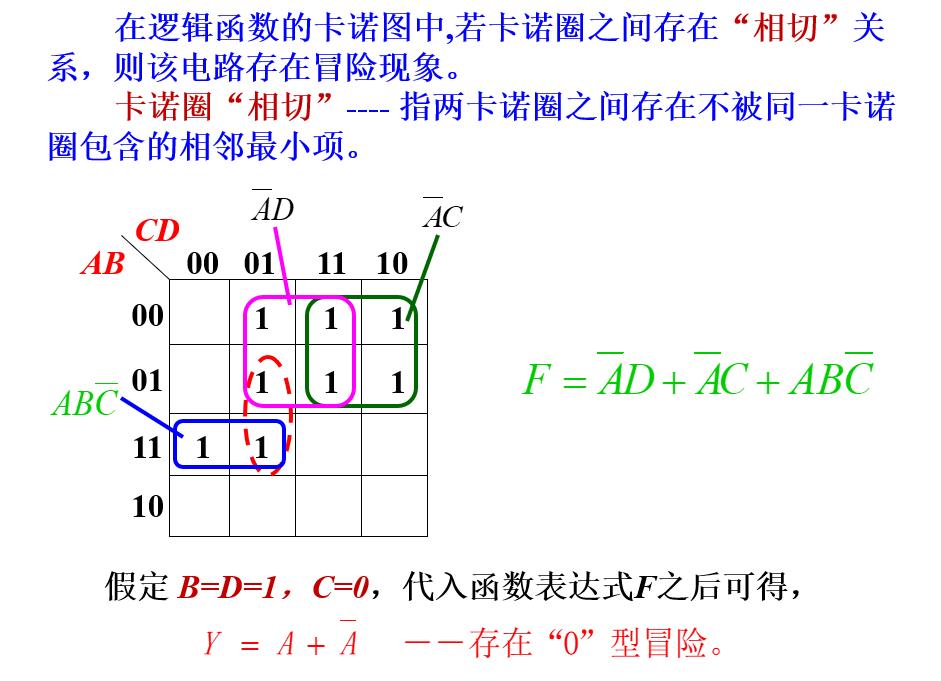

2.卡诺图识别法

三.竞争-冒险现象的消除方法

- 增加选通控制信号

- 输出端接入滤波电容

- 利用电容滤波作用,削去尖峰脉冲

- 修改逻辑设计,增加冗余项

以上是关于chap4组合逻辑电路的主要内容,如果未能解决你的问题,请参考以下文章