电子电路学习笔记(16)——晶振电路的电容

Posted Leung_ManWah

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了电子电路学习笔记(16)——晶振电路的电容相关的知识,希望对你有一定的参考价值。

一、简介

1.1 匹配电容

无源晶振电路中不只是有一个晶振,为了满足谐振条件让晶振起振正常工作,通常还有两个电容,两个电容一般称为“匹配电容”或者“谐振电容”。一般外接的这两个电容是为了使晶振两端的等效电容等于或接近于负载电容 (晶振的负载电容是已知的,在出厂时已经定下来了,一般是几十pF)。

要求高的场合还要考虑IC输入端的对地电容。一般晶振两端所接电容是所要求的负载电容的两倍。这样并联起来就接近负载电容了。

电容值的大小影响谐振频率(也就是会发生频偏),一般情况下,增大电容会使震荡频率下降,减小电容会使震荡频率升高。

1.2 负载电容

晶振有一个重要的参数,即负载电容CL(Load capacitance),它是电路中跨接晶体两端的总的有效电容 (不是晶振外接的匹配电容),主要影响负载谐振频率和等效负载谐振电阻,与晶体一起决定振荡器电路的工作频率,通过调整负载电容,就可以将振荡器的工作频率微调到标称值。

二、负载电容计算

2.1 电容三点式电路

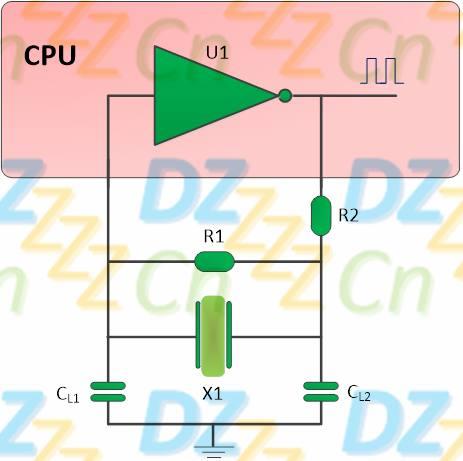

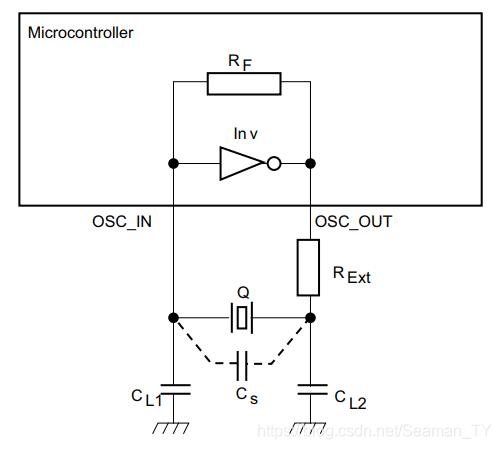

一般单片机都会有这样的电路。晶振的两个引脚与芯片(如单片机)内部的反相放大器相连接,再结合外部的匹配电容CL1、CL2、R1、R2,组成一个皮尔斯振荡器(Pierce oscillator)。

- U1: 增益很大的反相放大器。

- X1: 晶体。相当于电容三点式电路里面的电感。

- CL1、CL2: 匹配电容。是电容三点式电路的分压电容,接地点就是分压点。以接地点即分压点为参考点,输入和输出是反相的,但从并联谐振回路即石英晶体两端来看,形成一个正反馈以保证电路持续振荡,它们会稍微影响振荡频率,主要用与微调频率和波形,并影响幅度。

- R1: 反馈电阻(一般≥1MΩ)它使反相器在振荡初始时处于线性工作区。

- R2: 限流电阻,与匹配电容组成网络,提供180度相移,同时起到限制振荡幅度,防止反向器输出对晶振过驱动将其损坏。

2.2 负载电容计算公式

负载电容的公式如下所示:

C

L

=

C

L

1

×

C

L

2

C

L

1

+

C

L

2

+

C

i

c

+

△

C

C_L = \\frac{C_{L1}×C_{L2}}{C_{L1}+C_{L2}} + C_{ic}+△C

CL=CL1+CL2CL1×CL2+Cic+△C

等于

C

L

=

C

L

1

×

C

L

2

C

L

1

+

C

L

2

+

C

s

t

r

a

y

C_L = \\frac{C_{L1}×C_{L2}}{C_{L1}+C_{L2}} + C_{stray}

CL=CL1+CL2CL1×CL2+Cstray

其中,

- C i c C_{ic} Cic :为集成电路内部电容。

- △ C △C △C :为PCB走线电容 C P C B C_{PCB} CPCB。

- C s t r a y C_{stray} Cstray :为电路板杂散电容 C i c + △ C C_{ic}+△C Cic+△C。

Cic + △C 一般为 3 - 5 pF

三、匹配电容计算

3.1 匹配电容计算公式

为了保持晶体的负载平衡,在实际应用中,一般要求

C

L

1

C_{L1}

CL1=

C

L

2

C_{L2}

CL2,所以进一步可以得到下式:

C

L

1

=

C

L

2

=

2

×

(

C

L

−

C

i

c

−

△

C

)

C_{L1} = C_{L2} = 2 × (C_L - C_{ic} -△C)

CL1=CL2=2×(CL−Cic−△C)

Cic + △C 一般为 3 - 5 pF

3.2 计算示例

C L C_L CL负载电容(load capacitance),常用的标准值有12.5 pF,16 pF,20 pF,30pF,负载电容和谐振频率之间的关系不是线性的,负载电容变小时,频率偏差量变大;负载电容提高时,频率偏差减小。

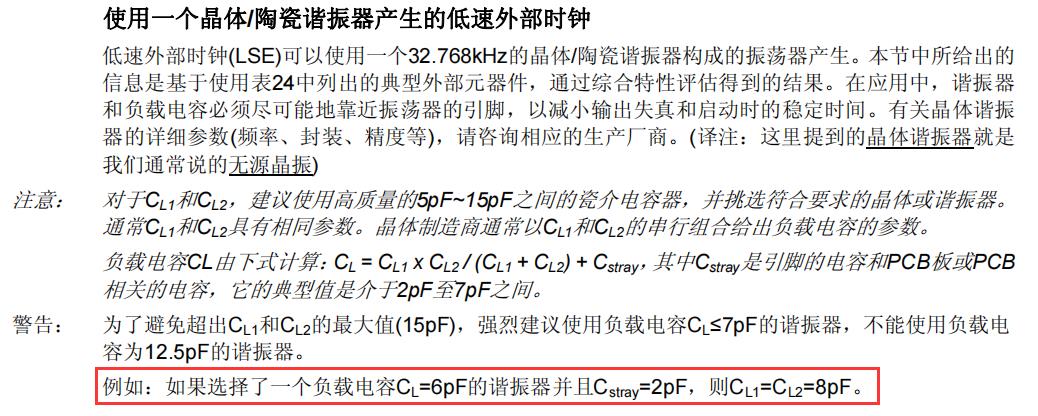

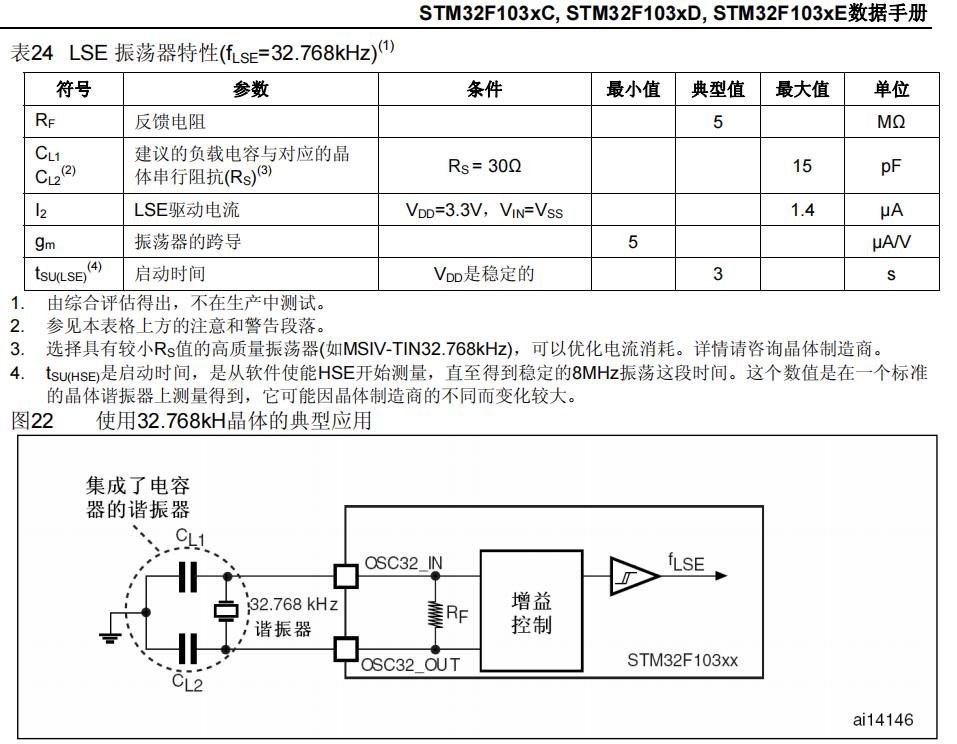

STM32F103系列芯片使用32.768kHz晶振典型应用,负载电容

C

L

C_L

CL取6pF时,当

C

s

t

r

a

y

C_{stray}

Cstray取2pF,则

C

L

1

=

C

L

2

=

2

×

(

6

−

2

)

p

F

=

8

p

F

C_{L1} = C_{L2} = 2 × (6 - 2) pF = 8pF

CL1=CL2=2×(6−2)pF=8pF

四、选取原则

- 选择NPO/COG高频材质的贴片陶瓷电容(外观看起来是白色的)。

- 尽量选择小封装的电容(封装小的器件寄生参数小)。

- 因为每一种晶振都有各自的特性,所以最好按制造厂商所提供的数值选择外部元器件。

- 在许可范围内,C1,C2值越低越好。C值偏大虽有利于振荡器的稳定,但将会增加起振时间。

- 最好C2值大于C1值,这样可使上电时,加快晶振起振。

• 由 Leung 写于 2021 年 11 月 10 日

• 参考:晶振负载电容外匹配电容计算与晶振振荡电路设计经验总结

晶体(crystal、无源晶振)两端电容取值计算

STM32 外部晶振电路设计和匹配

晶振外匹配电容应该怎样选取

以上是关于电子电路学习笔记(16)——晶振电路的电容的主要内容,如果未能解决你的问题,请参考以下文章