数字电路逻辑设计笔记:集成逻辑门电路

Posted 临风而眠

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了数字电路逻辑设计笔记:集成逻辑门电路相关的知识,希望对你有一定的参考价值。

数字电路逻辑设计笔记(3):集成逻辑门电路

§3.1 概述

一.门电路及其分类

逻辑门电路是用于实现各种基本逻辑运算、常用符合逻辑运算的电子电路,简称门电路

-

门电路是用以实现逻辑关系的电子电路,逻辑门

-

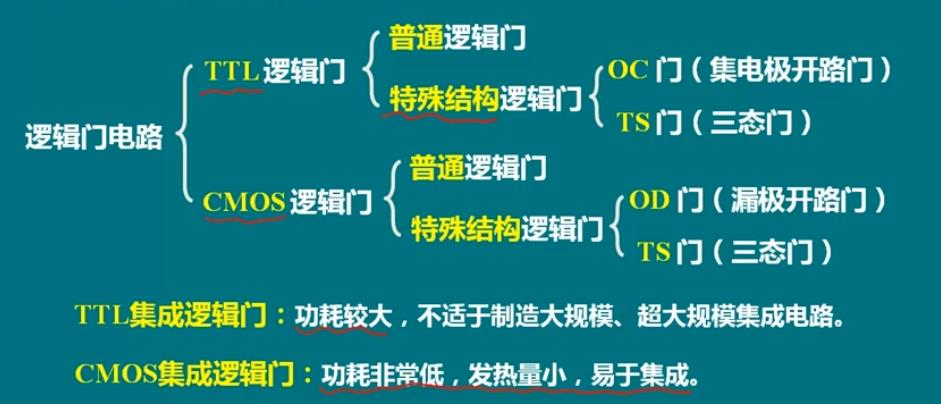

门电路的分类

- 按所用的半导体器件分类

- 分立元件门电路

- 集成门电路

-

双极型集成门(DTL、TTL)

-

MOS集成门

-

- 按所用的半导体器件分类

-

集成电路的分类

-

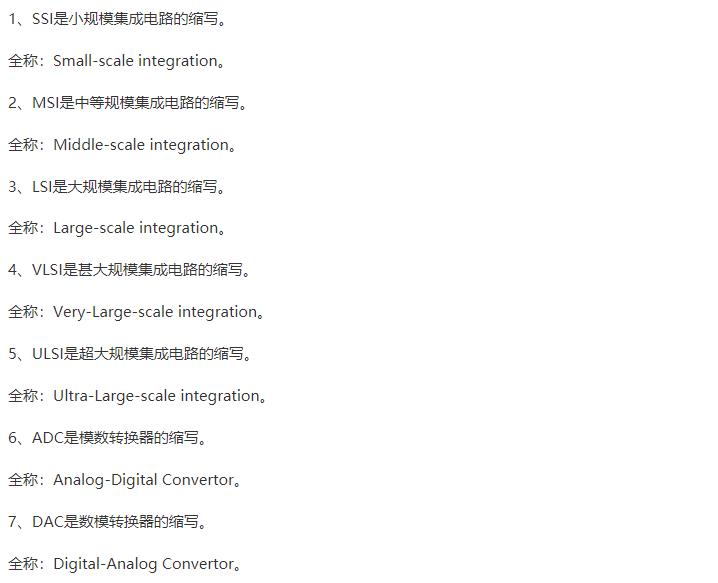

集成电路简称IC(Intergrated Circuit),按规模的大小可分为:

-

小规模集成电路 0~9个二输入门

-

中规模集成电路 10~99个门

-

大规模集成电路 100~10000个门

-

超大规模集成电路 超过10000个门

-

-

二.逻辑电平

实际开关为晶体二极管、三极管以及场效应管等电子器件

逻辑电平“0”,“1”不是物理量,只是物理量的相对表示

- 高电平

V

H

V_H

VH

- 输入高电平 V I H V_{IH} VIH

- 输出高电平 V O H V_{OH} VOH

- 低电平

V

L

V_L

VL

- 输入低电平 V I L V_{IL} VIL

- 输出低电平 V O L V_{OL} VOL

§3.2 半导体元件的开关特性

一.半导体基本知识

参考教程:

1.本征半导体

由硅(Si),锗(Ge)等材料制成的单晶体

-

相邻原子之间共用一对电子(价电子) – 共价键结构

-

自由电子和空穴成对出现 --电子空穴对

-

自由电子运动的运动产生电子电流;价电子递补空穴产生空穴电流

电子、空穴这两种载流子都参与导电

故称之为双极型

-

电子空穴对既产生又复合,一定温度下达到动态平衡

2.杂质半导体

-

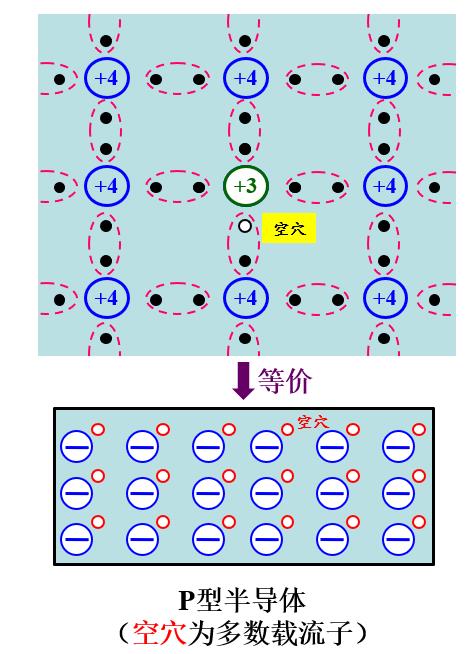

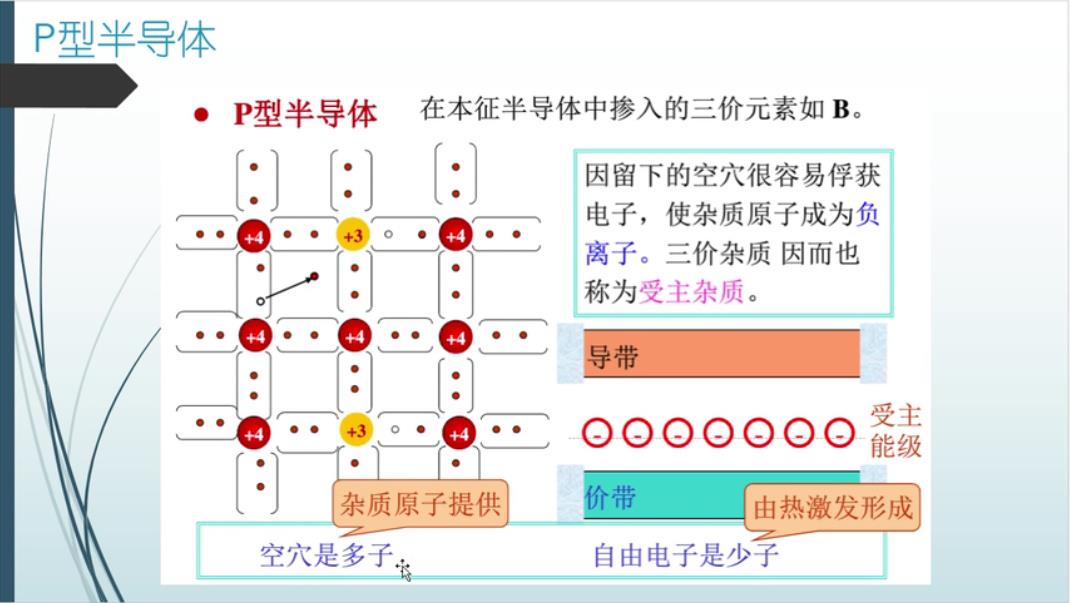

P型半导体(空穴为多数载流子)

-

P:positive

-

-

-

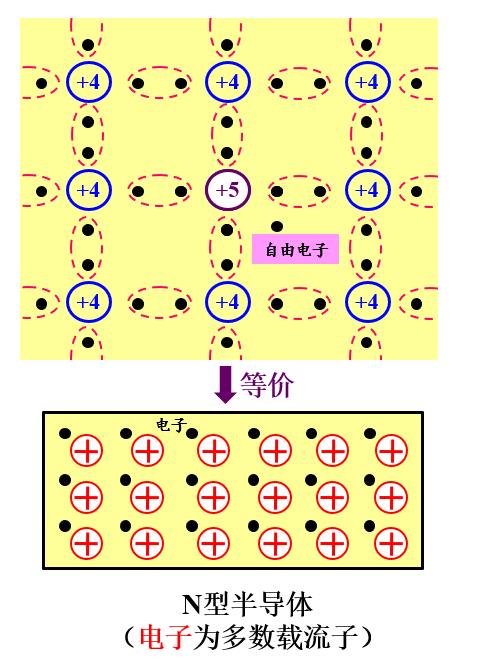

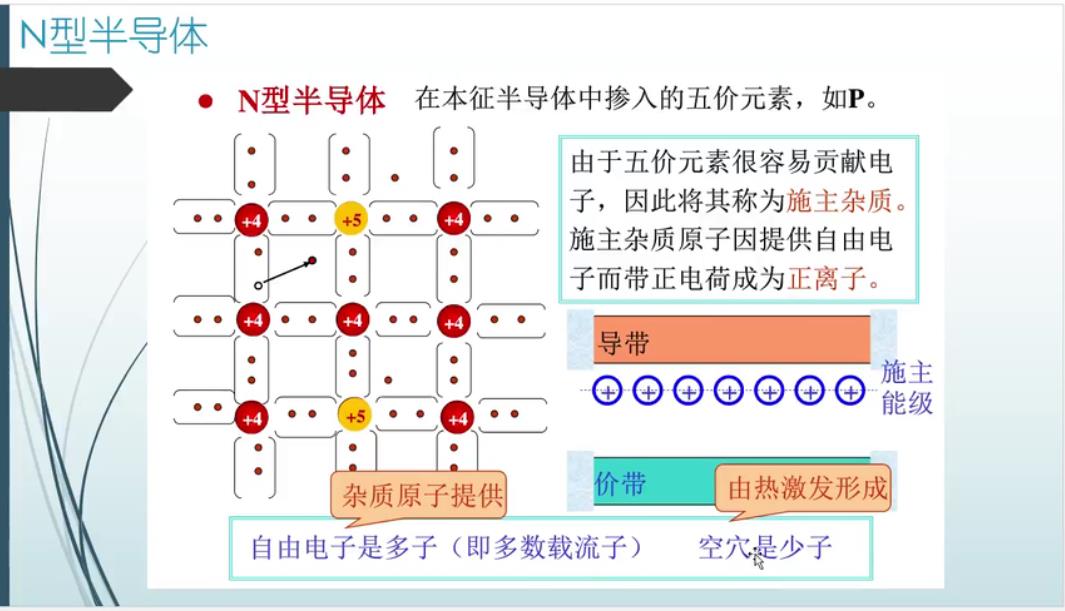

N型半导体(电子为多数载流子)

-

N:negative

-

-

3.PN结及其特性

-

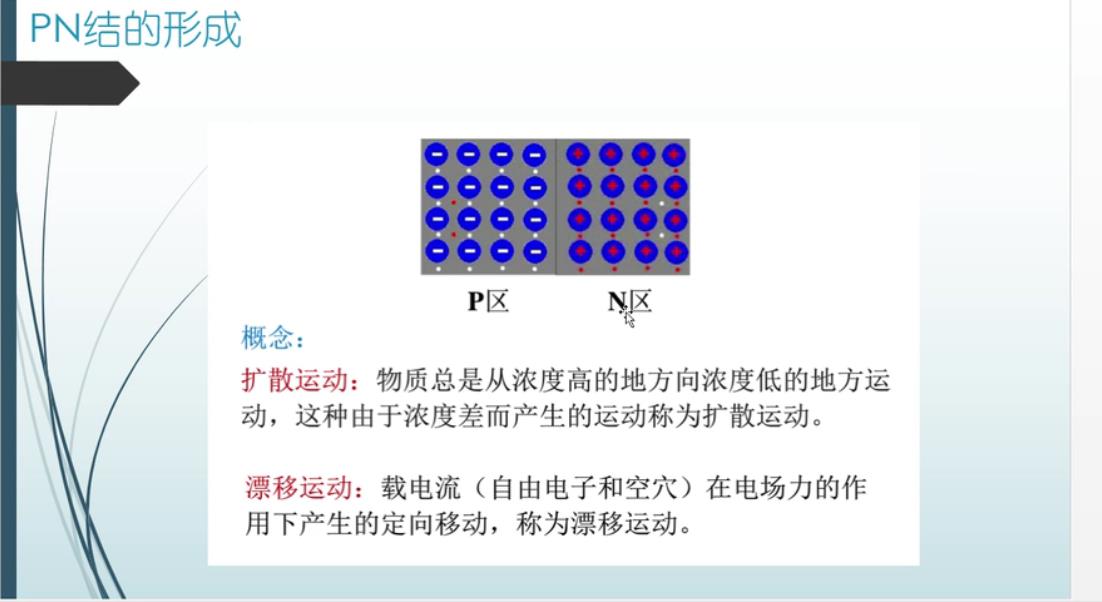

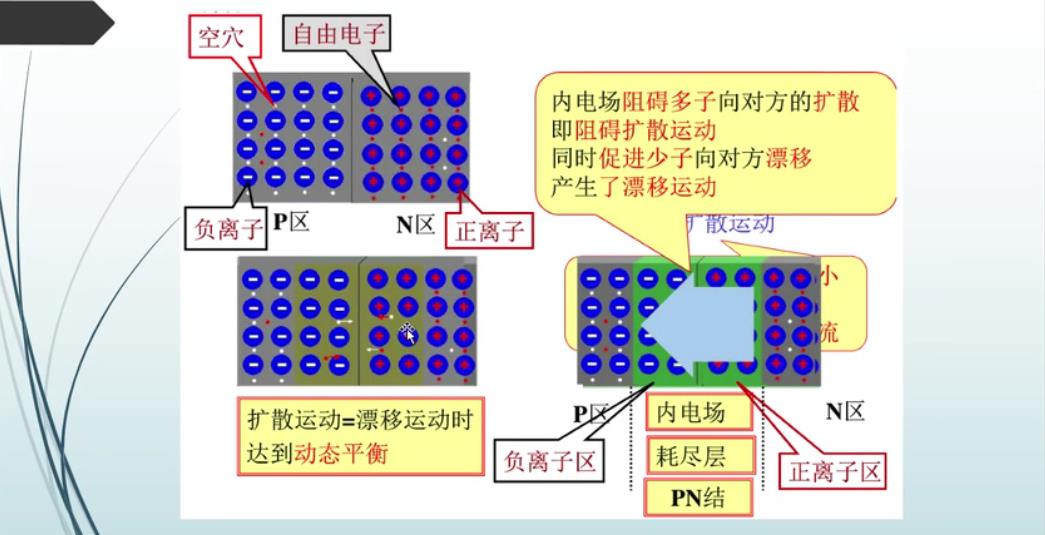

PN结的形成

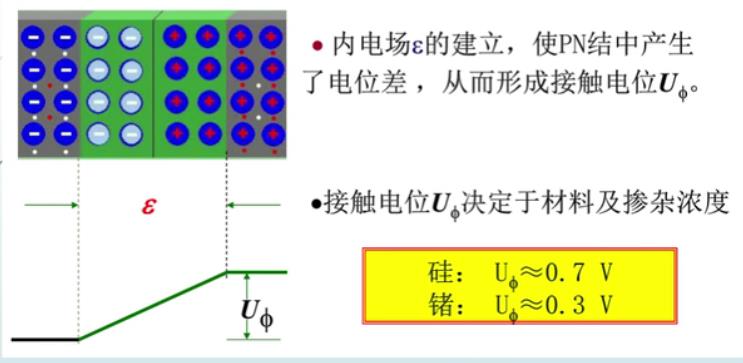

正离子和负离子产生内电场,

内电场阻碍多子的扩散,促进少子的漂移

多子的扩散和少子的漂移达到动态平衡,形成PN结

-

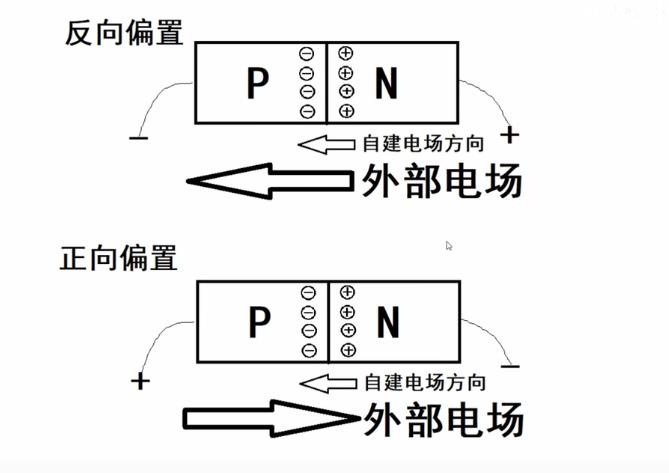

PN结的特性:单向导电性

-

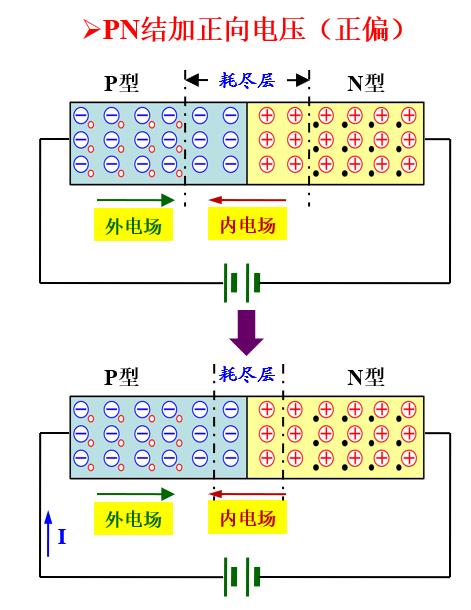

PN结加正向电压(正偏)

偏:偏置

-

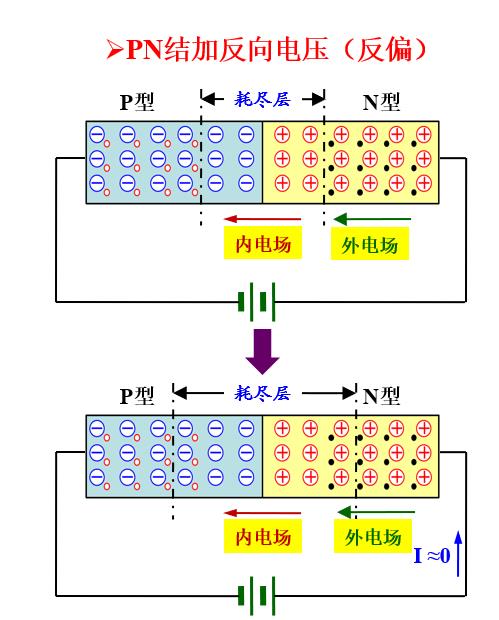

PN结加反向电压(反偏)

反向电压进一步增加了多数载流子通过空间电荷区的难度

只有少数载流子会形成很小的反向饱和电流

PN结具有单向导电性

-

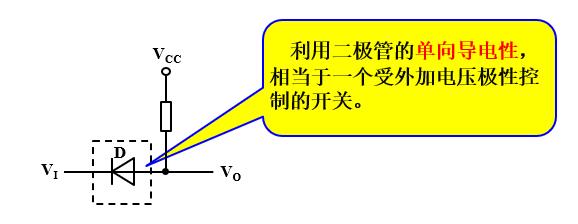

二.半导体二极管的开关特性

半导体二极管是由PN结引出电极和管壳构成的

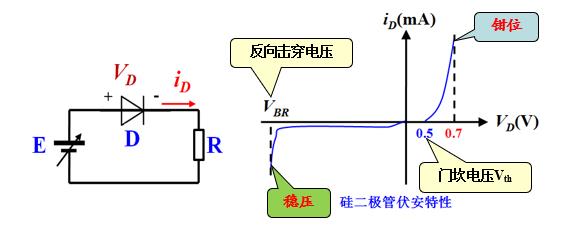

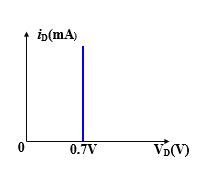

1.二极管伏安特性

三角表示PN结的正偏方向

-

二极管具有单项导电性

-

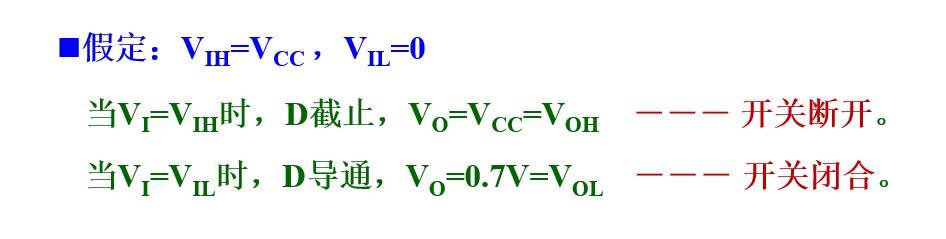

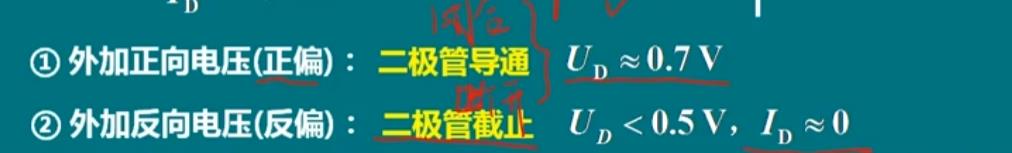

外加正向电压

二极管导通,导通压降约为0.7V

电压稳定在0.7左右,而电流可以有很大变化,称为钳位

-

外加反向电压,二极管截止(电流几乎为0)

击穿之后,积聚的电荷会涌出,所以电流会急剧增大

- 可利用反向击穿特性制成稳压管

-

2.二极管开关特性

三.半导体三极管的特性

晶体管(三极管)

参考:

这个讲的真的好!!!

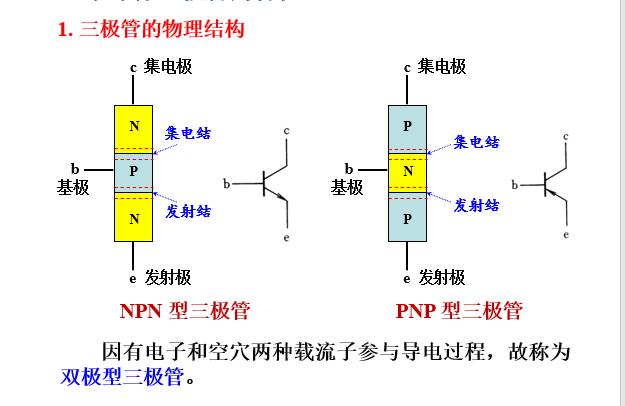

1.三极管的物理结构

因有电子和空穴两种载流子参与导电过程,故称为双极型三极管

集电极和基极之间是集电结, 发射极和基极之间是发射结

箭头是发射结的正偏方向

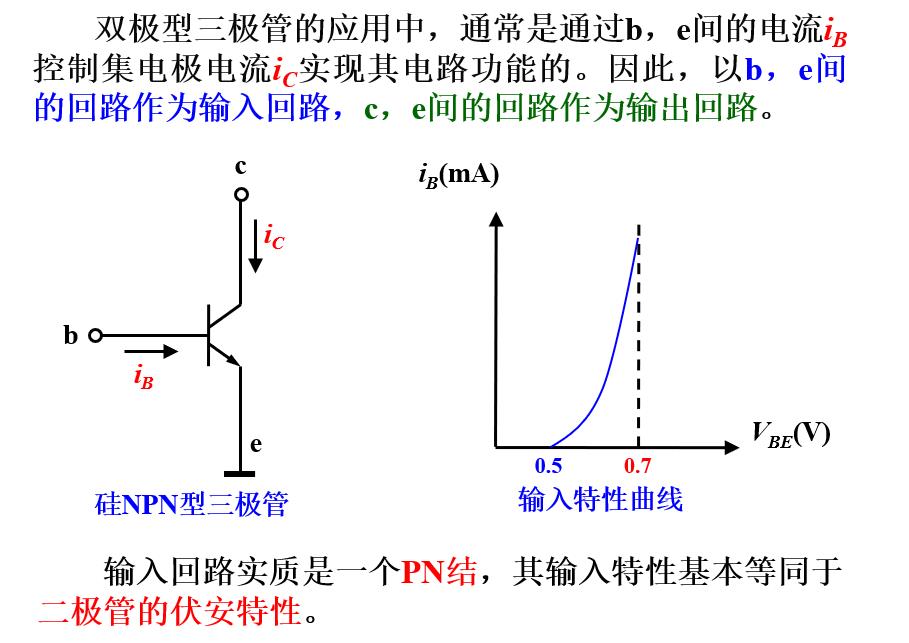

2.三极管输入特性

用基极电流带动集电极电流

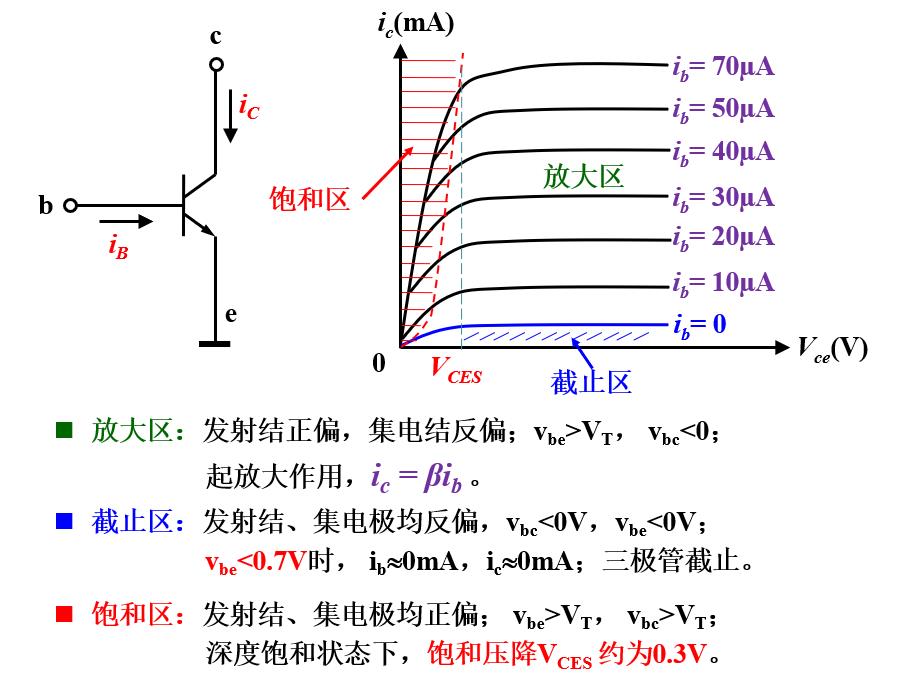

3.三极管的输出特性

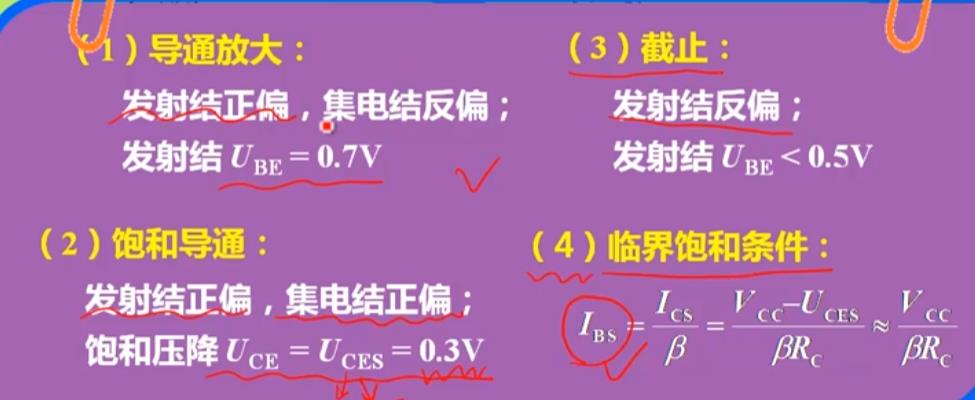

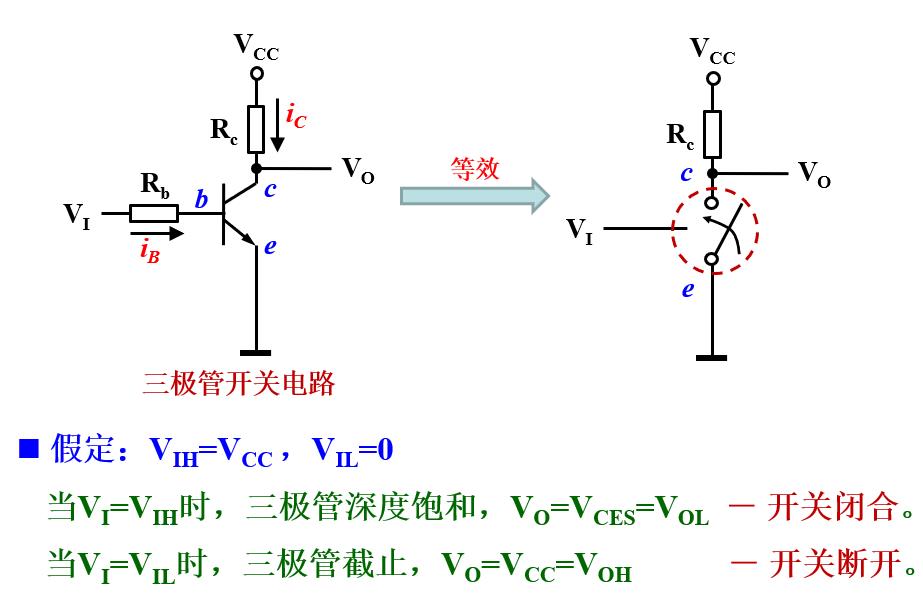

4.三极管的开关特性

数电主要要求掌握开关特性

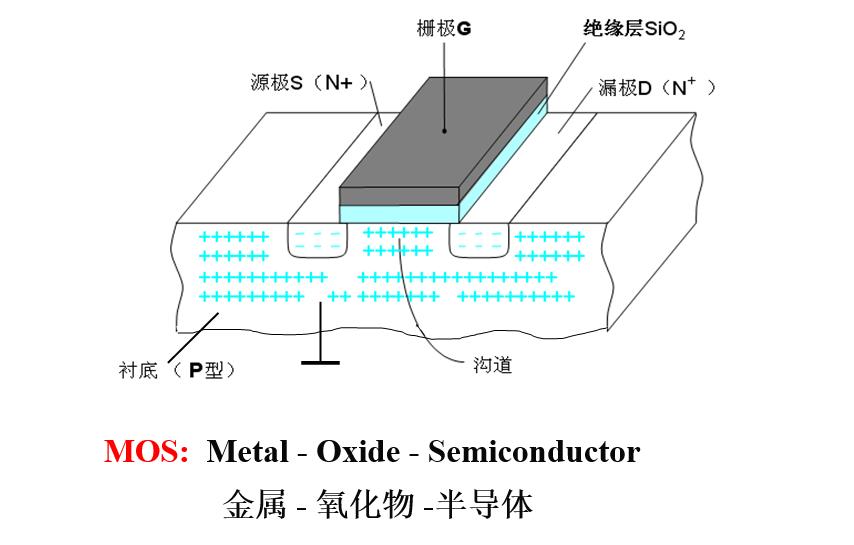

四.MOS场效应管的开关特性

参考:

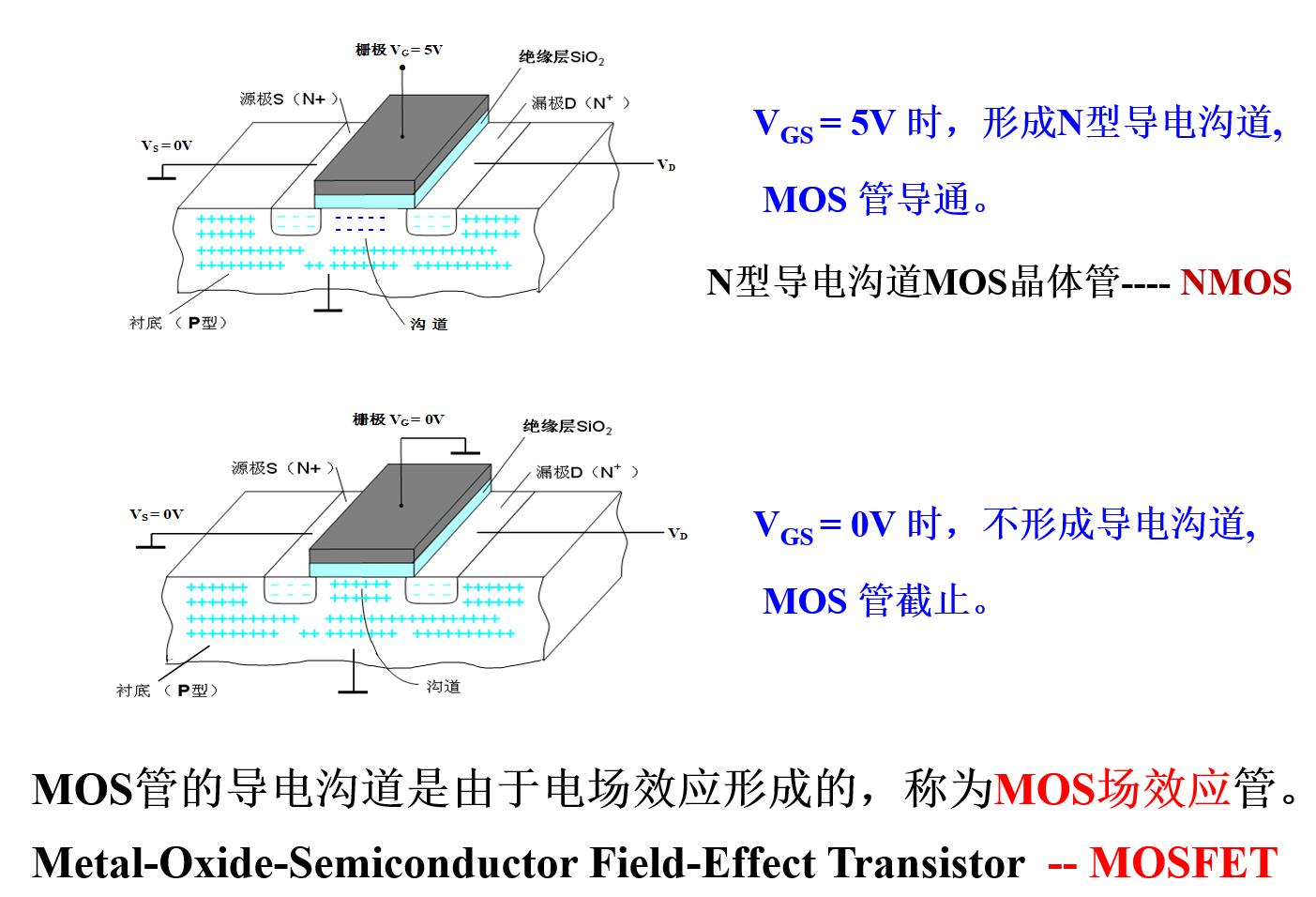

1.NMOS晶体管

物理结构

工作原理

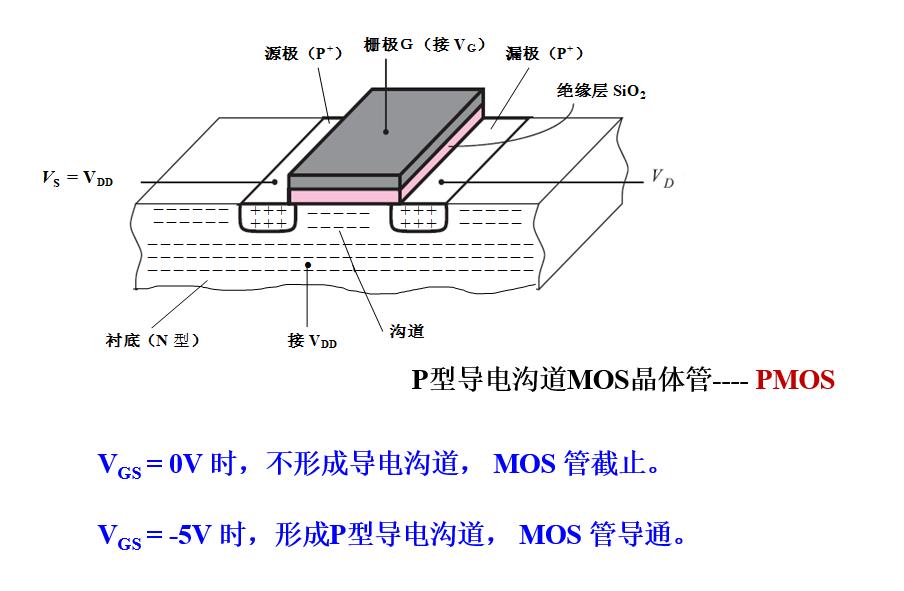

2.PMOS晶体管

结构与工作原理

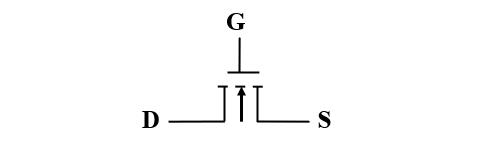

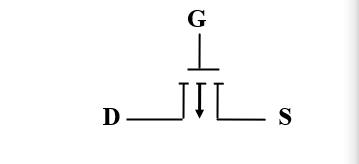

3.MOS晶体管符号

- NMOS晶体管符号

P型衬底指向N型沟道

- PMOS晶体管符号

P型沟道指向N型衬底

NMOS管 N型沟道

PMOS管 P型沟道

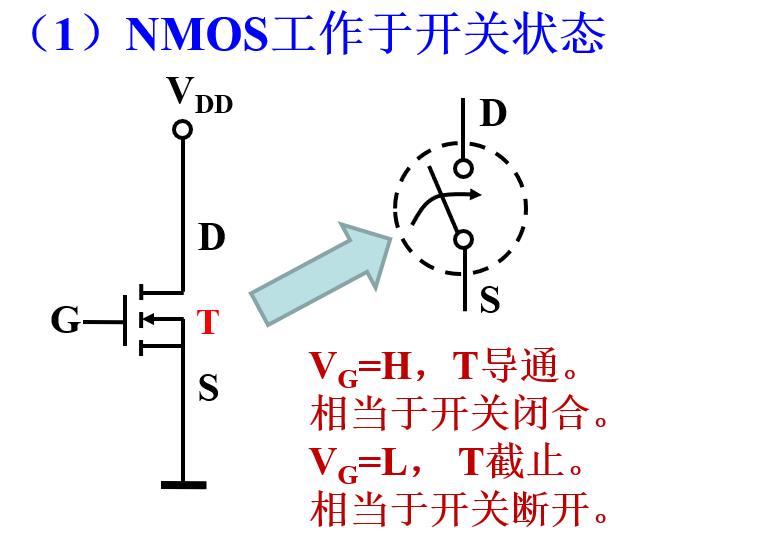

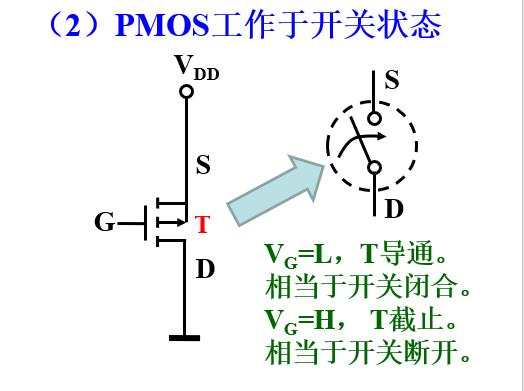

4.MOS晶体管开关特性

-

NMOS工作于开关状态

-

PMOS工作于开关状态

开关特性总结:

二极管的单向导电性

三极管在饱和区相当于开关闭合,在截止区相当于开关断开

§3.3 分立元件门电路

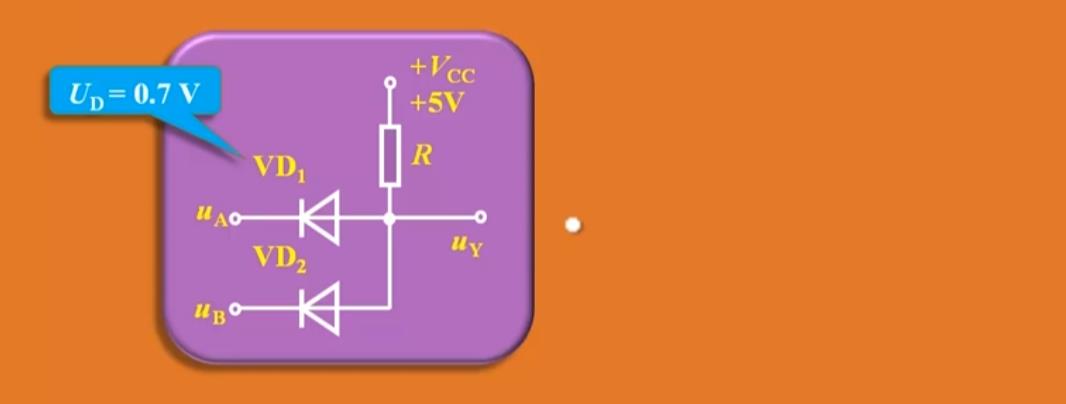

一.二极管门电路

参考:

这一集mooc讲的太棒啦

1.二极管与门

参考:二极管与门:https://blog.csdn.net/gdt_a20/article/details/7229989

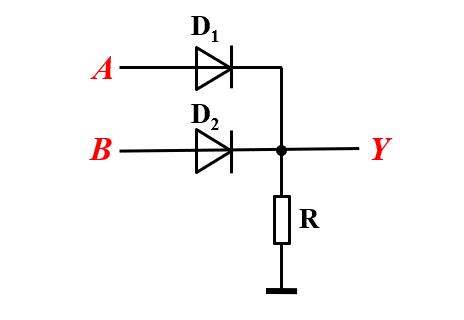

该电路中的元件:

电阻、正5V电压源、两个二极管(导通电压以硅二极管为例,是0.7V)

有两个输入A和B,一个输出Y

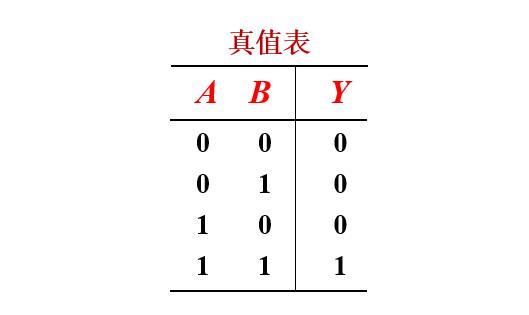

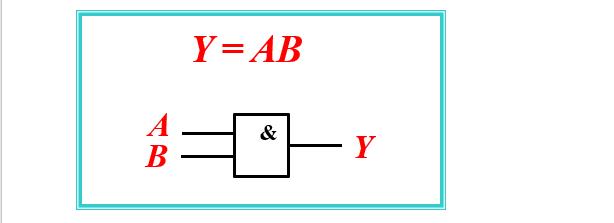

期望达成的逻辑功能就是 Y = A ⋅ B Y=A\\cdot B Y=A⋅B与逻辑功能

各情况逐个分析一下

0、1是根据高低电平范围的逻辑“0”,逻辑“1”

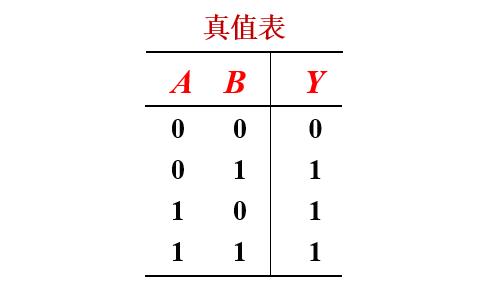

2.二极管或门

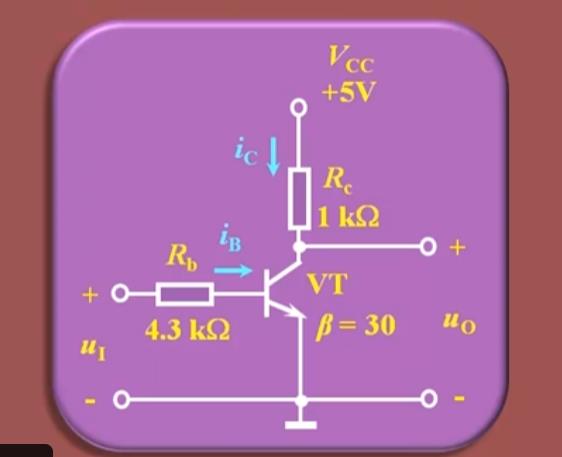

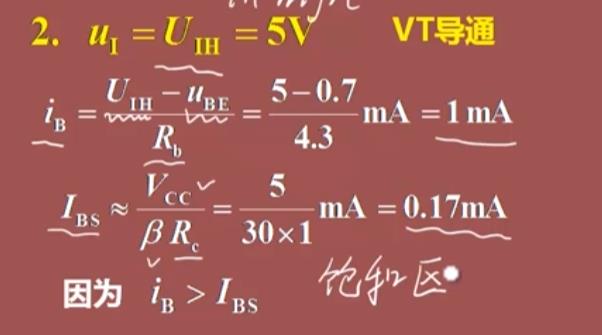

二.三极管门电路

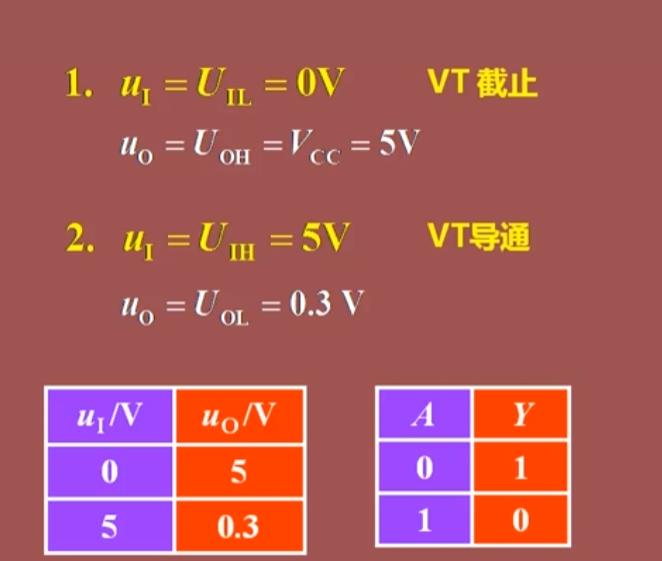

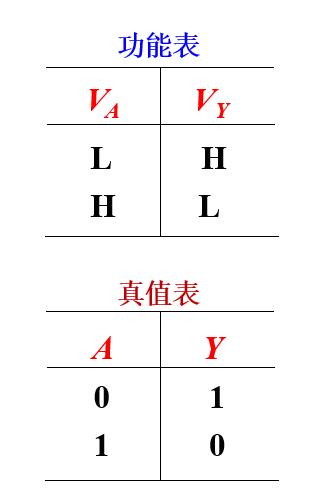

1.三极管非门(反相器)

导通时,直接在饱和区而避免了在放大区工作

在进行电路设计的时候,可通过选取特定的元件参数,使得三极管导通的时候就是饱和导通,从而在数字电路中只体现开关特性

因为饱和工作时,饱和压降 V C E S V_{CES} VCES是0.3V

所以:

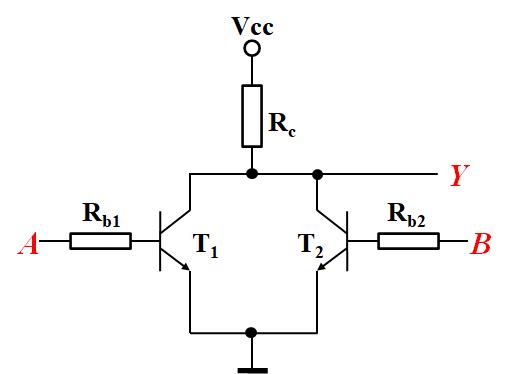

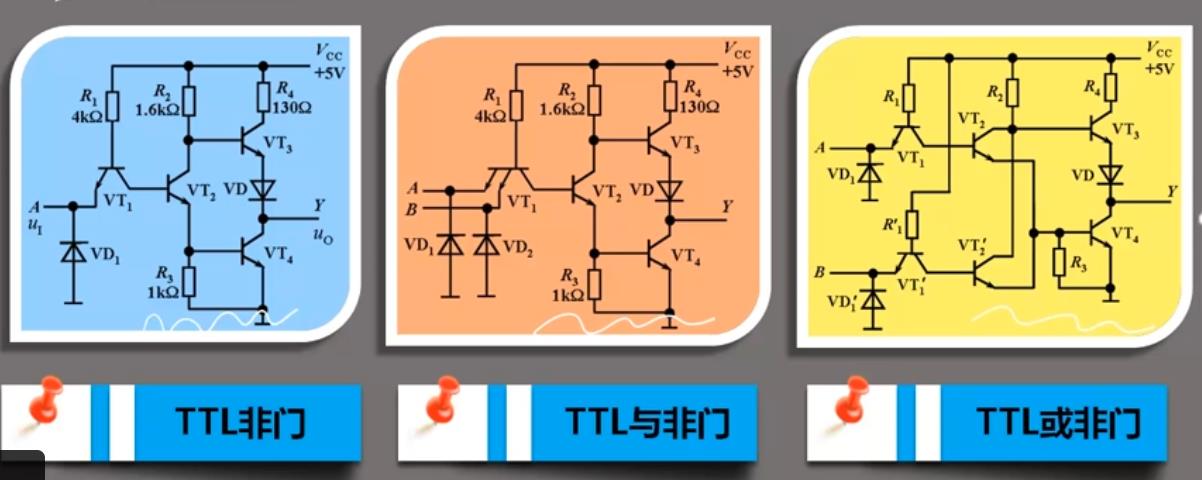

2.三极管或非门

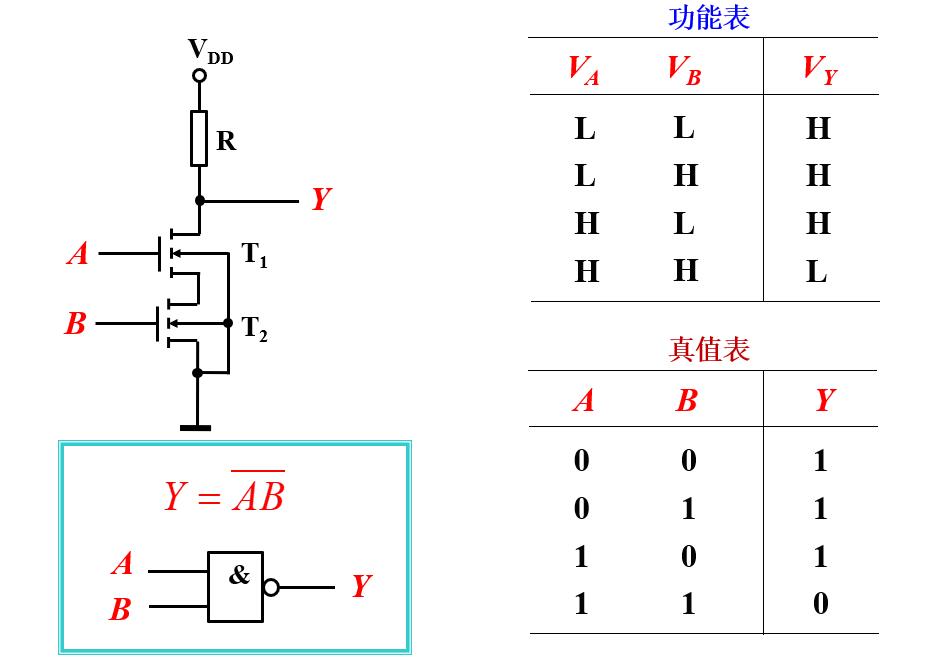

三.MOS门电路

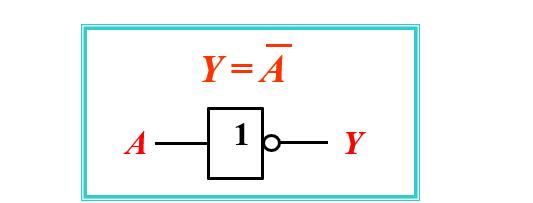

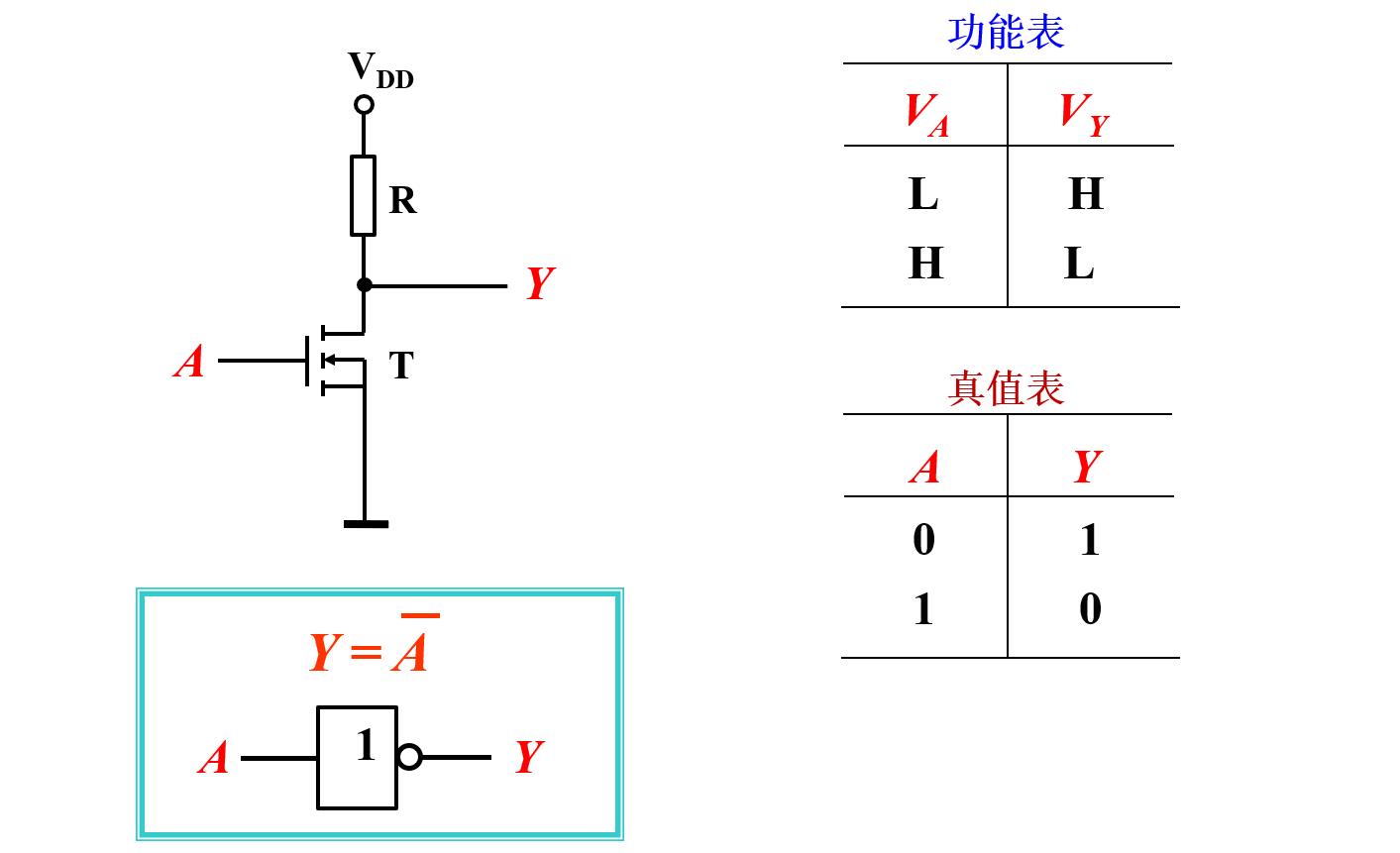

1.MOS非门(反相器)

2.MOS与非门

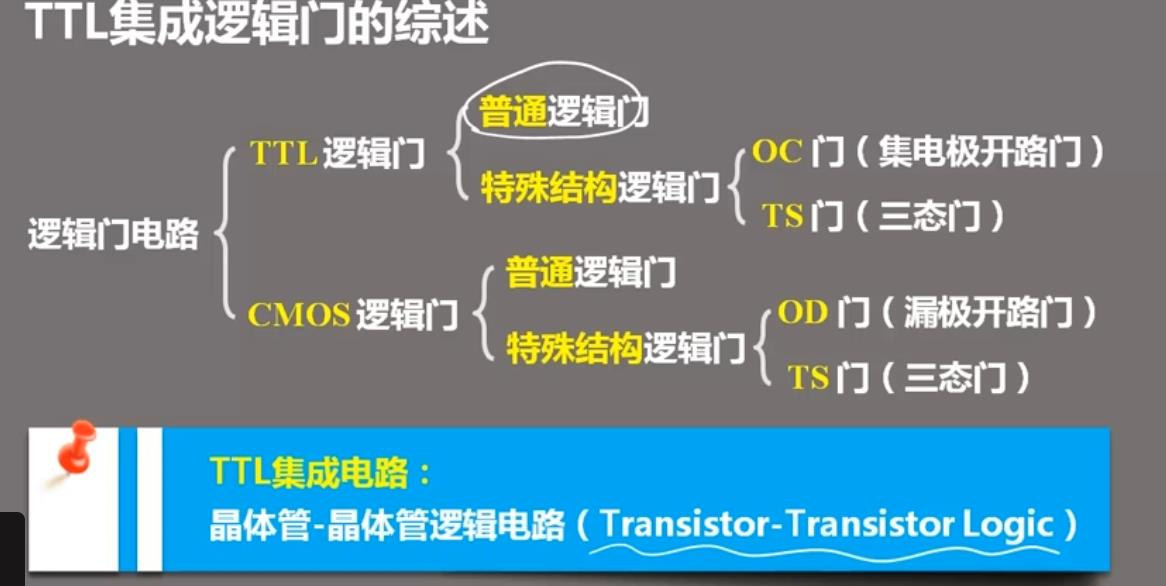

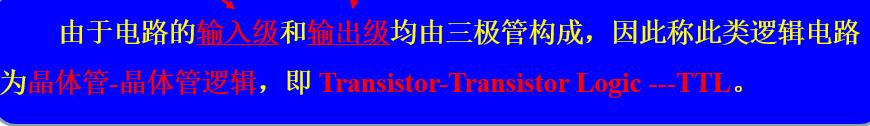

§3.4 TTL集成门电路

一.TTL非门

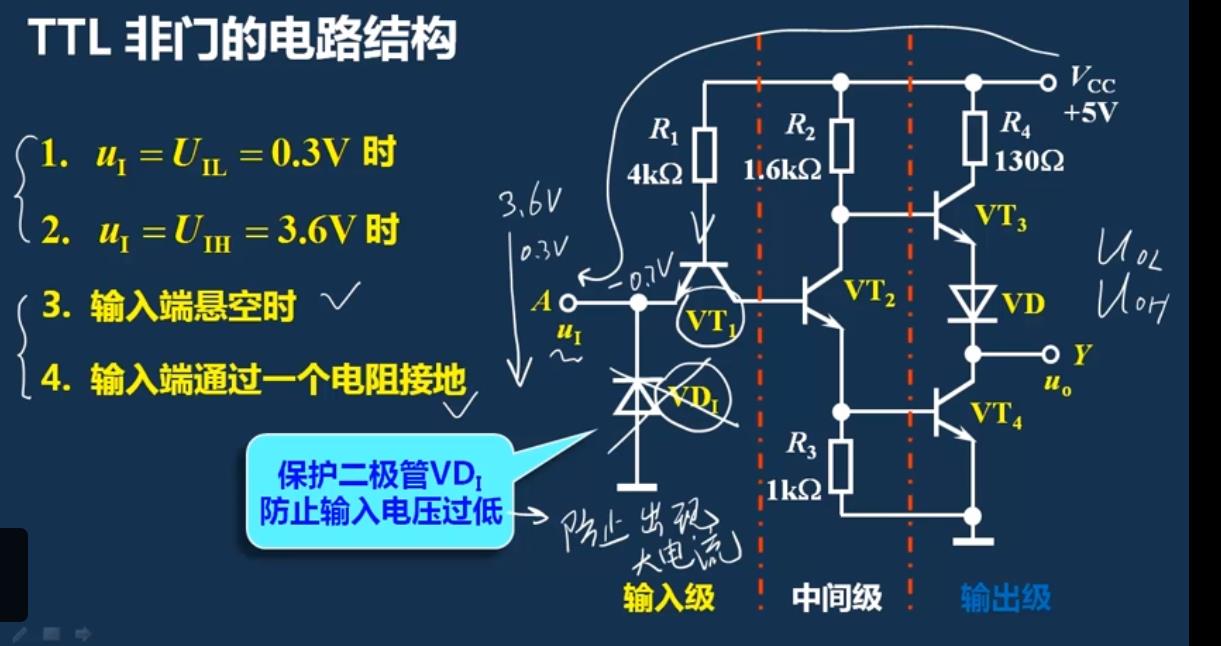

1.TTL非门的电路结构

其中 V D Ⅰ VD_{Ⅰ} VDⅠ是保护二极管,防止输入电压过低,防止出现大电流

2.TTL非门的工作原理

保护二极管没有其他作用,所以下面的图中不展示

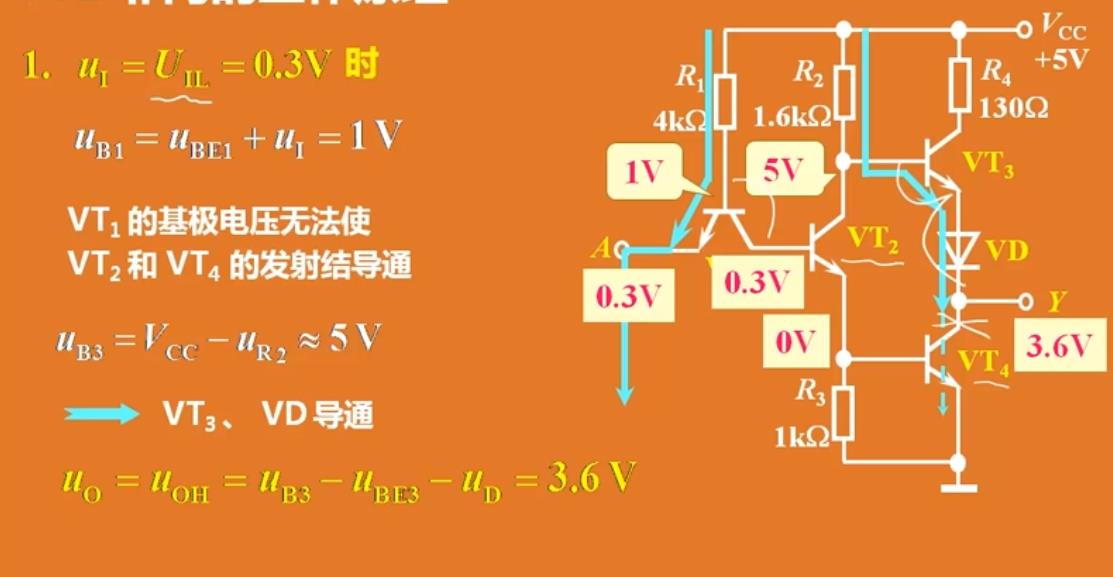

- U I = U I L = 0.3 V U_I=U_{IL}=0.3V UI=UIL=0.3V时(输入低电平时)

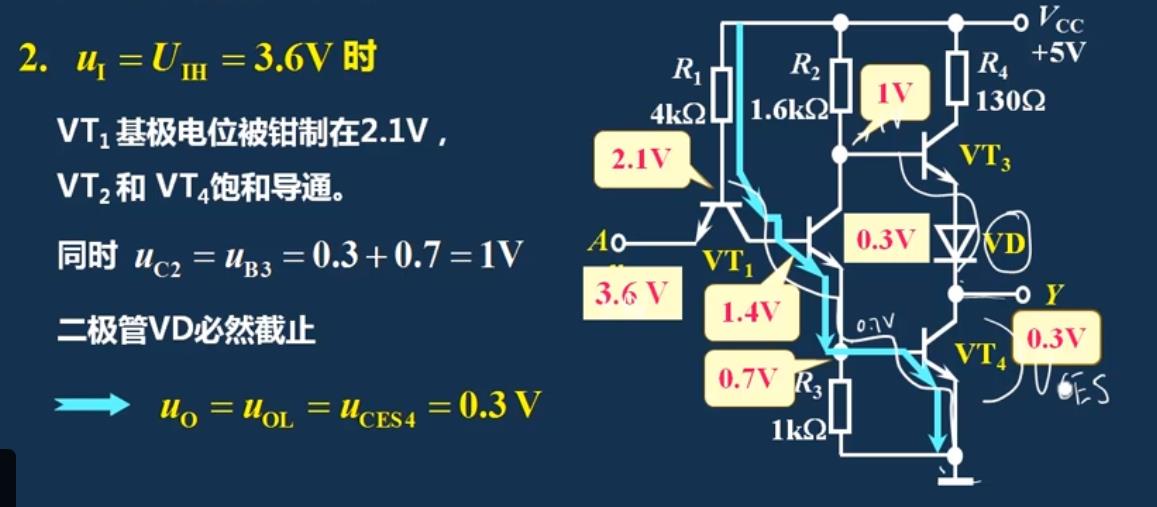

-

U I = U I H = 3.6 V U_I=U_{IH}=3.6V UI=UIH=3.6V时(输入高电平时)

由这种情况和上面一种情况就可以确定该电路完成的是非逻辑功能了

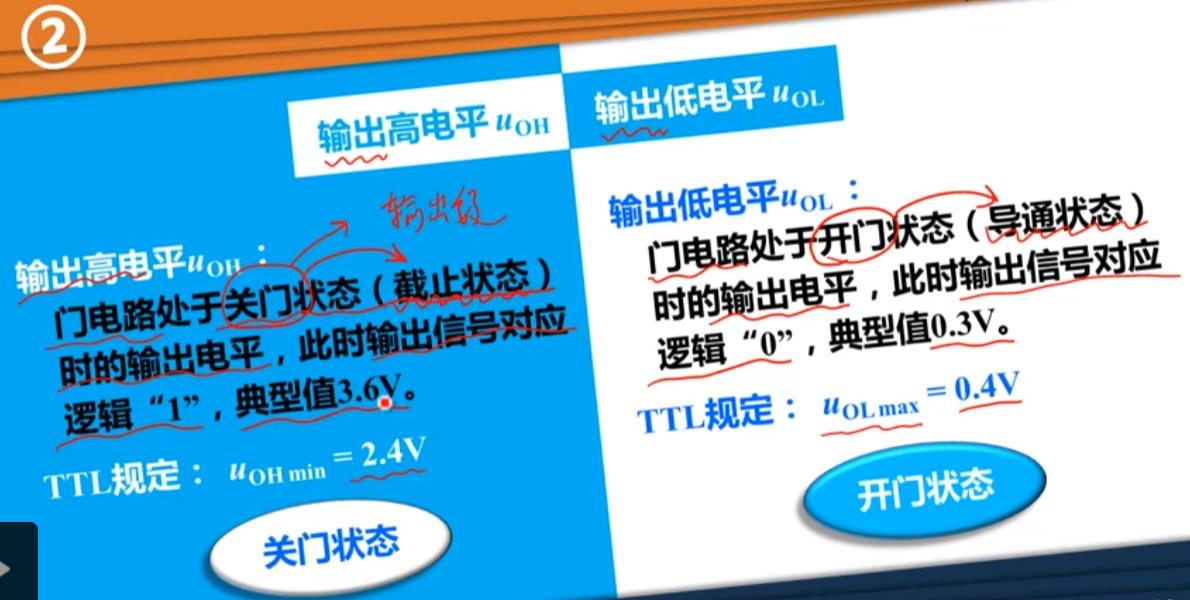

3.输入、输出特性参数

二.TTL与非门

参考:

这个好棒!,还解释了多发射极三极管!

这是个口碑很好的up!

附上合辑链接!❤

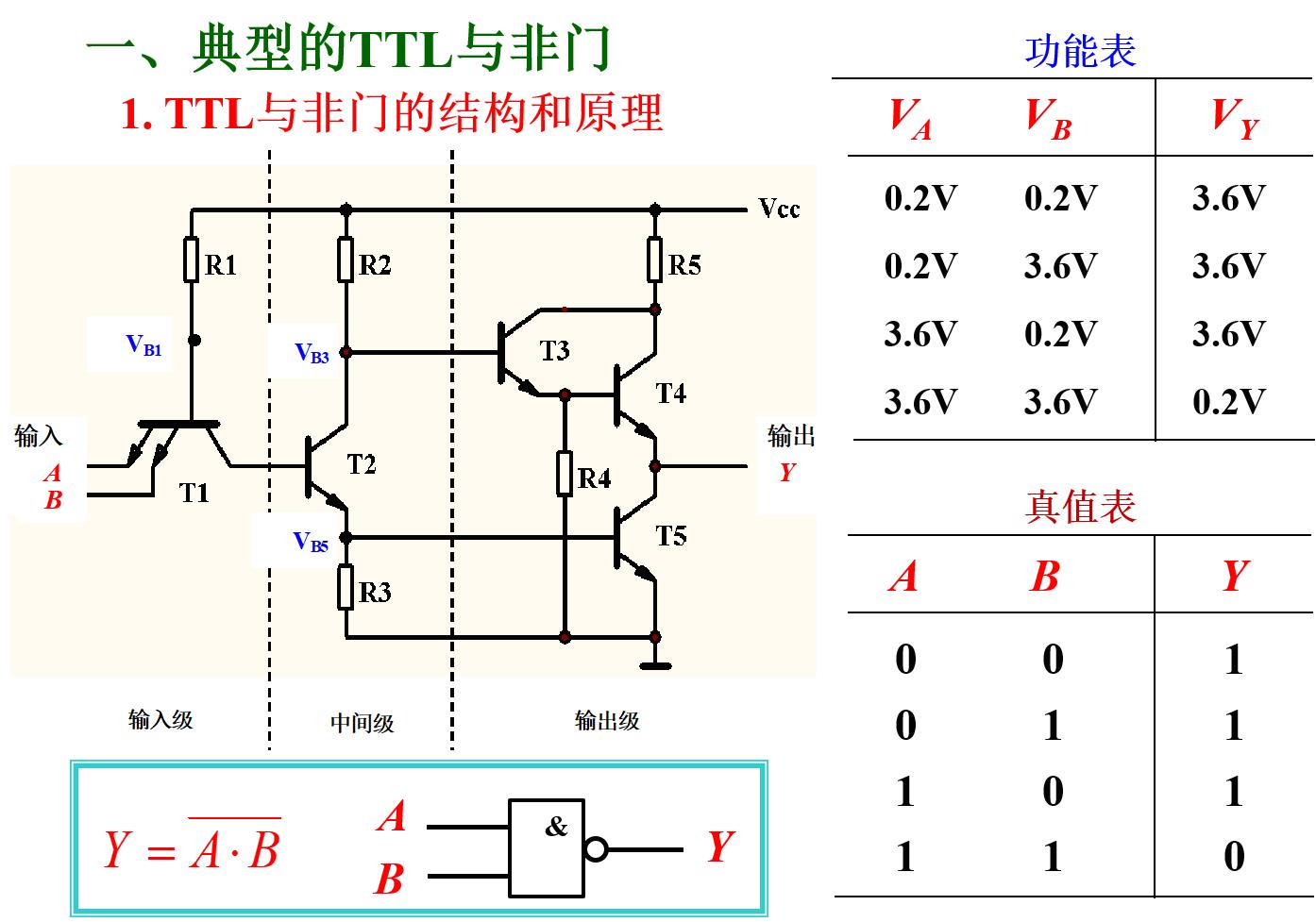

1.TTL与非门的结构和原理

- 输入端使用的是多发射极三极管,多发射极三极管实现的是”与“的功能

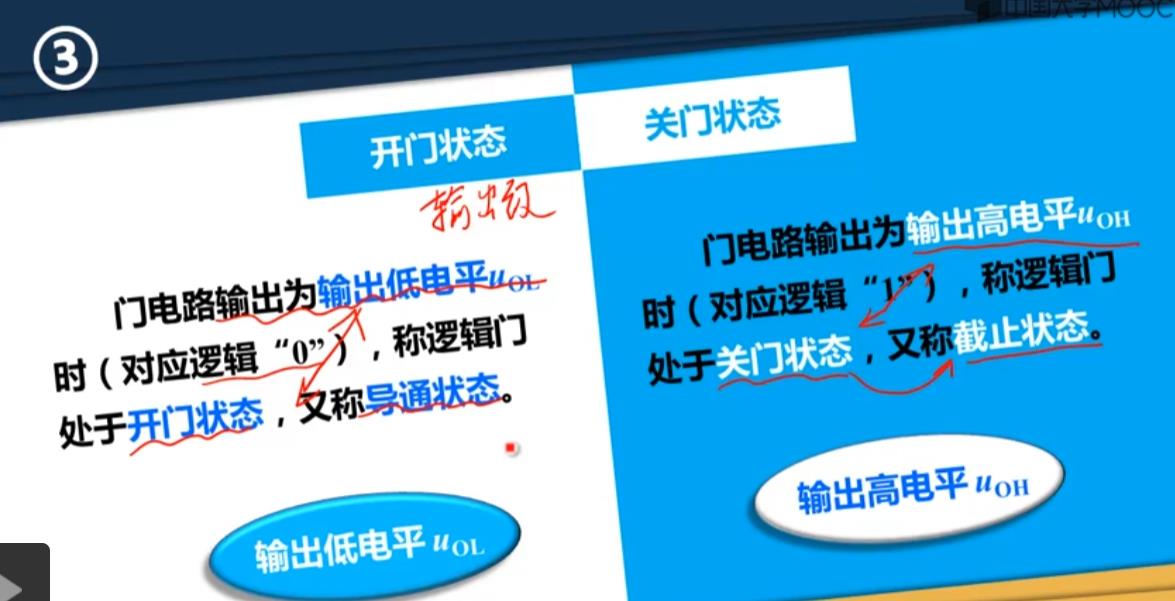

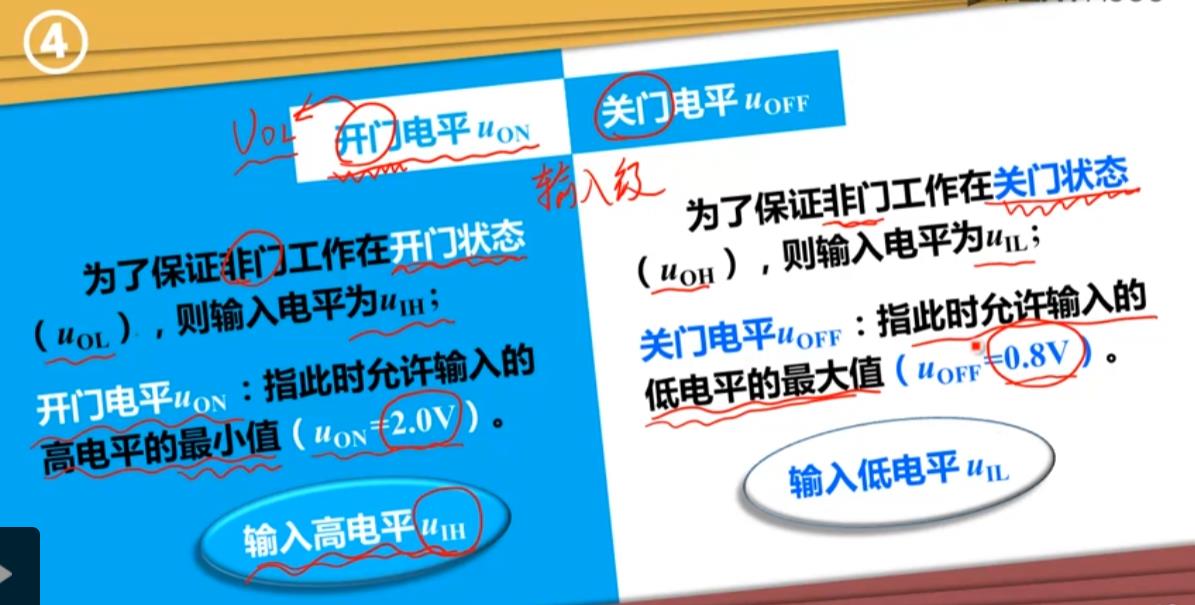

2.TTL与非门的外特性及其参数

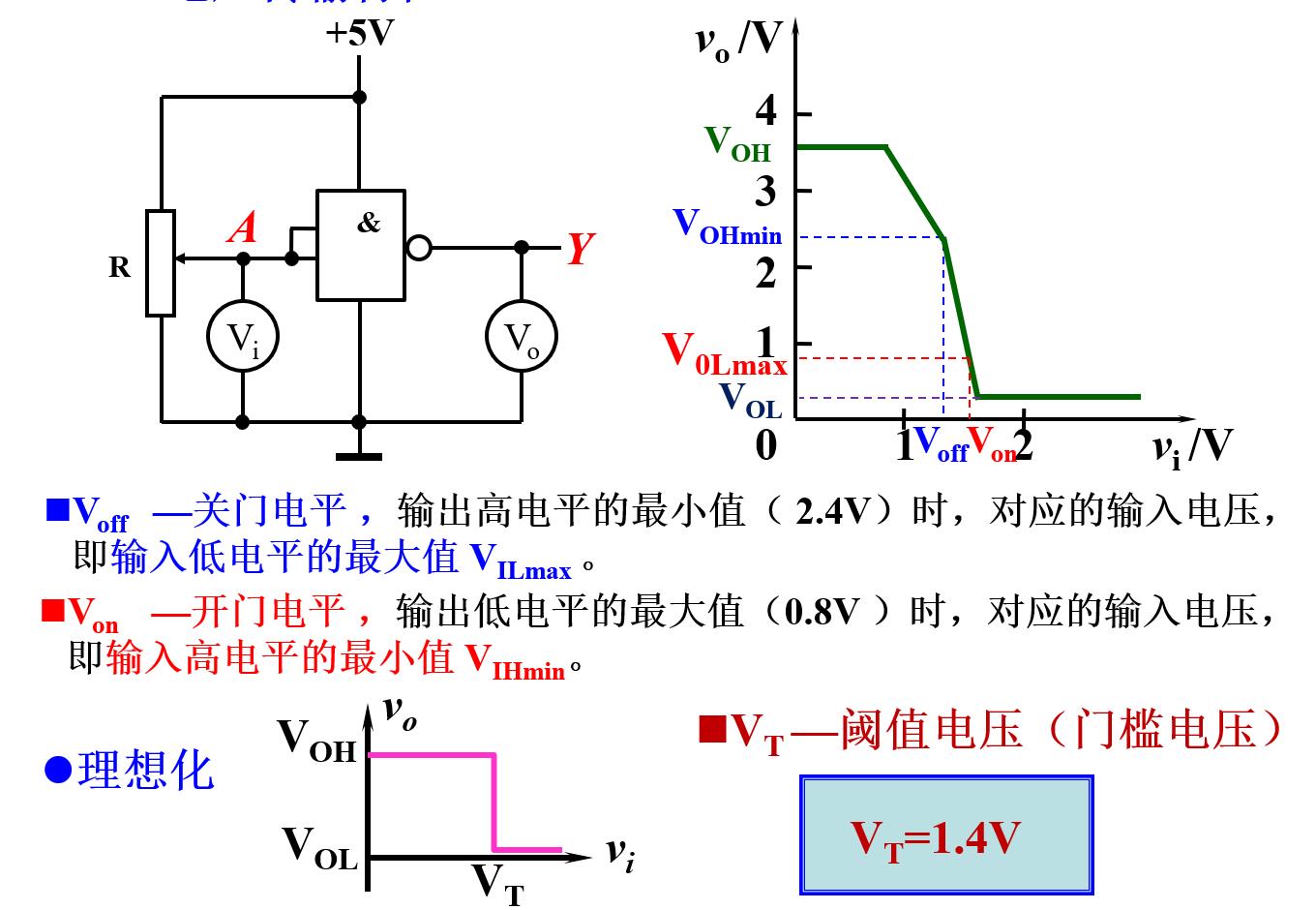

电压传输特性

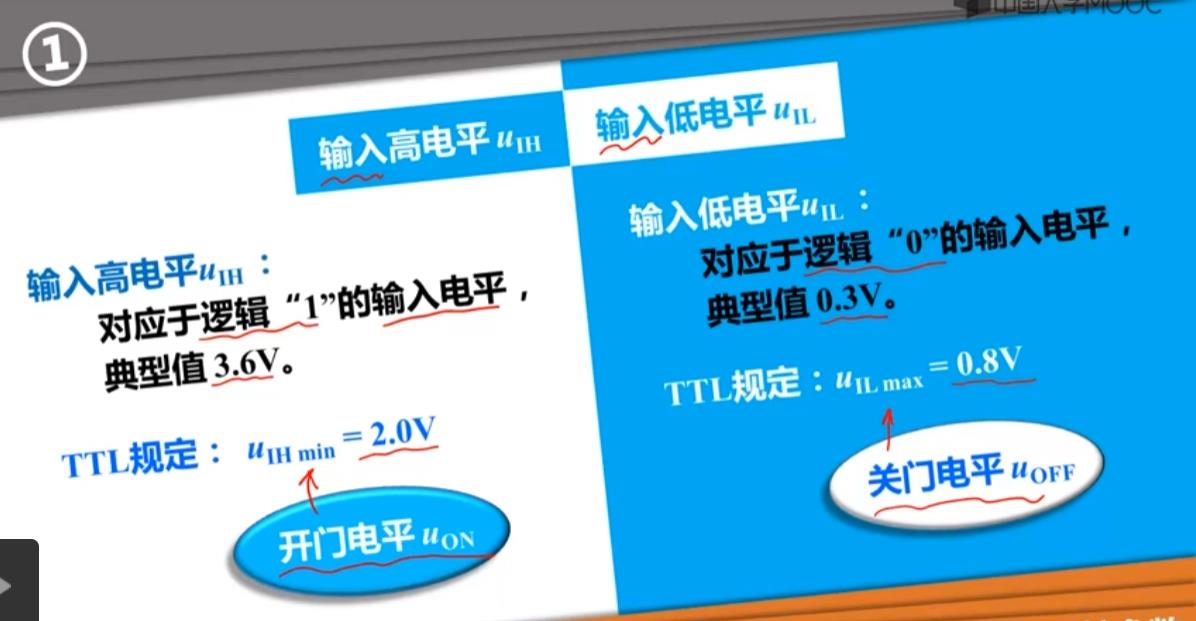

为啥叫关门电平,输入的是低电平(0),对于与非门来讲,输入0,必出1,所以相当于固定了,“把门关起来了”

比开门电平大,门开着

比关门电平小,门关着

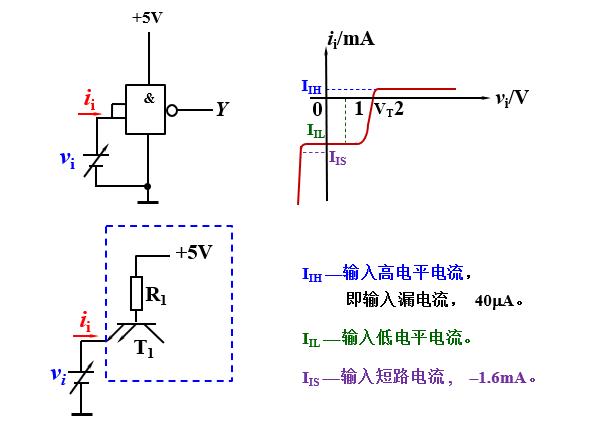

输入伏安特性

输入负载特性

开门电阻是输入端大电阻的下限

开门电平是输入端大电压的下限

关门电阻是输入端小电路的上限

关门电平是输入端小电压的下限

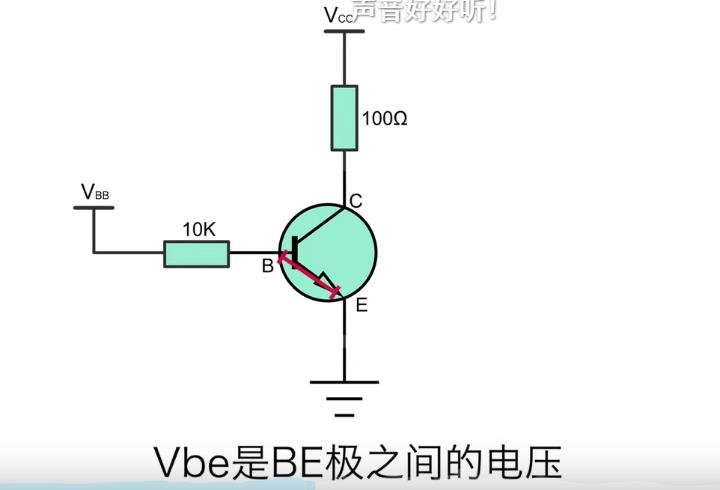

图中的Vbe好像是这个意思?(应该是0.7)

输出负载特性

参考链接:https://blog.csdn.net/zhangfan406/article/details/81909436

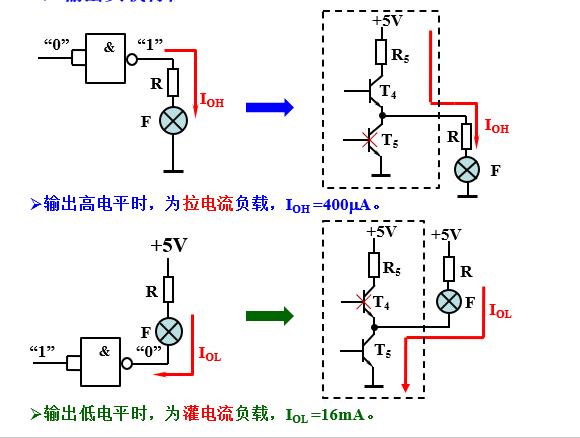

输出高电平的时候,下面的 T 5 T_5 T5是相当于断开的

输出低电平的时候,上面的 T 4 T_4 T4是相当于断开的

GND ground 地,接地

-

拉电流(sourcing current)

对一个端口而言,如果电流方向是向其外部流动的则是“拉电流”

高电平输出时,一般是输出端对负载提供电流,其提供电流的数值叫“拉电流”;

-

灌电流(sink current)

对一个端口而言,如果电流方向是向其内部流动的则是“灌电流”

低电平输出时,一般是输出端要吸收负载的电流,其吸收电流的数值叫“灌(入)电流”。

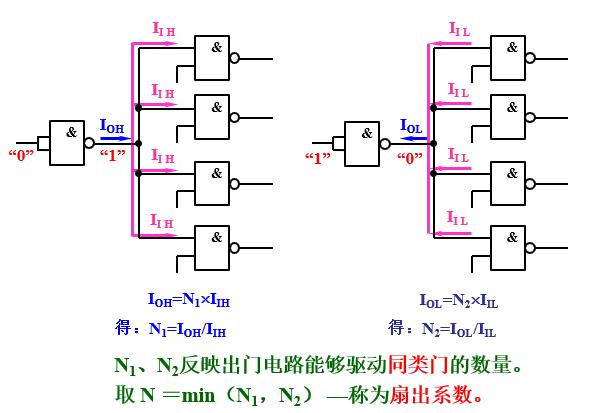

负载能力计算

负载能力:前级门能带动后级门的能力

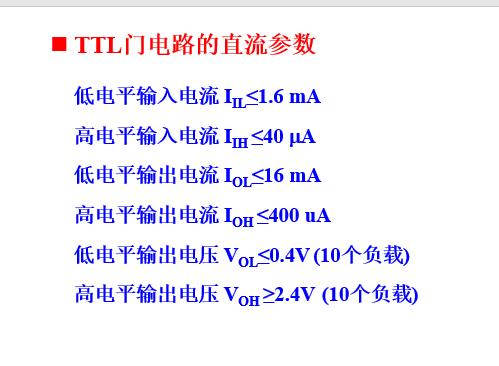

TTL门电路的直流参数

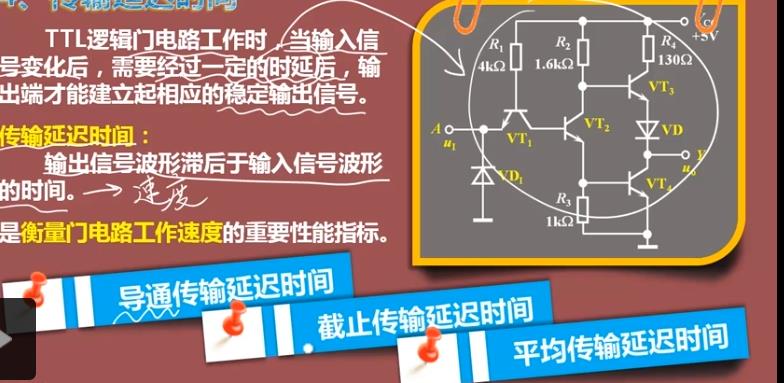

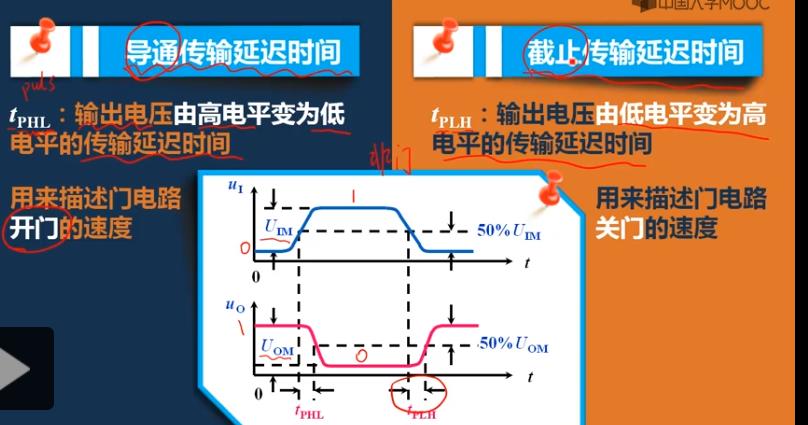

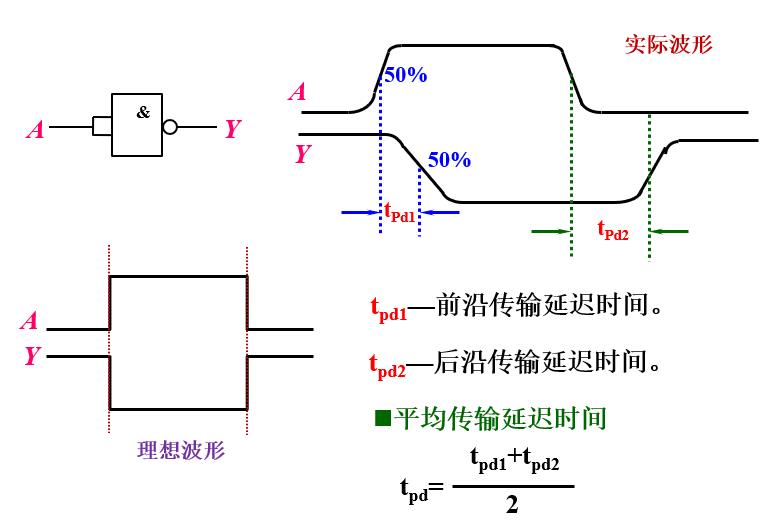

传播延迟时间

这是逻辑门的速度指标

-

导通传输延迟时间、截止传输延迟时间

-

平均传输延迟时间

p:pulse 脉冲

一个逻辑门电路,开门关门速度往往是不一样的,

如TTL与非门,如果输出为低电平,是下半部分工作,饱和导通

之前的 V C E S V_{CES} VCES原来是这个意思/(ㄒoㄒ)/~~

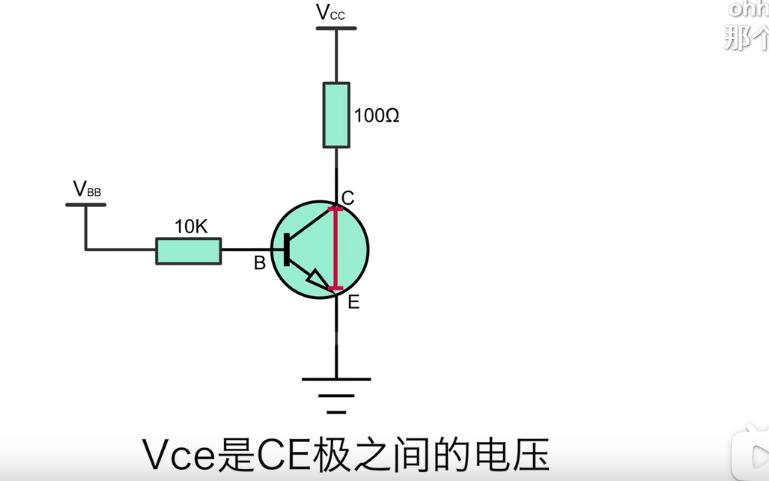

V b e V_{be} Vbe是BE极之间的电压(基极、发射极) , V c b V_{cb} Vcb是CB极之间的电压(集电极、基极), V c e V_{ce} Vce是CE极之间的电压

参考:三极管的饱和与放大

如果输出高电平,是上半部分工作,这也就意味着开门和关门所经过的具体的工作电路不一样,那么速度也不一样

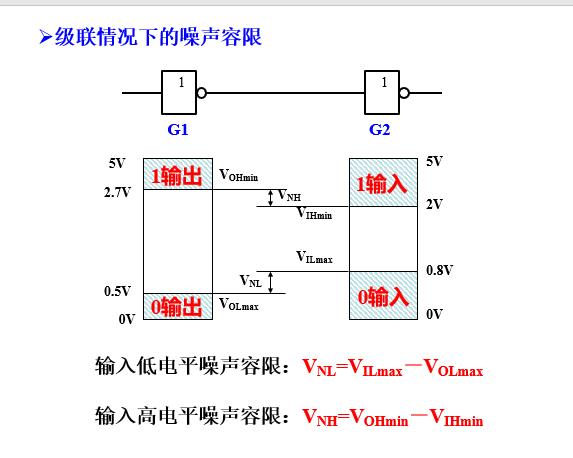

输入噪声容限

-

实际应用中,由于外界干扰、电源波动等原因,可能使输入电平 V I V_I VI偏离规定值。为了保证电路可靠工作,应对干扰的幅度有一定限制,称为噪声容限

-

低电平噪声容限

-

指在保证输出电平正确的前提下,允许叠加在输入低电平上的最大噪声电压(正向干扰),用 V N L V_{NL} VNL表示:

V N L = V I L m a x − V I L V_{NL}=V_{ILmax}-V_{IL} VNL=VILmax−VIL

N在这里是noise的意思

-

-

高电平噪声容限

-

指在保证输出电平正确的前提下,允许叠加在输入高电平上的最大噪声电压(负向干扰),用 V N H V_{NH} VNH表示:

V N H = V I H − V I H m i n V_{NH}=V_{IH}-V_{IHmin} VNH=VIH−VIHmin

-

-

三.集电极开路的门电路(OC门)

1.OC门的由来

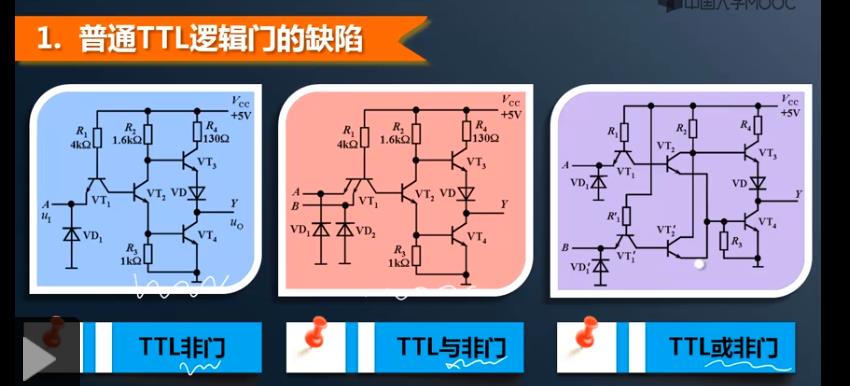

普通TTL逻辑门的缺陷

在看特殊的TTL逻辑门之前,先来看看普通TTL逻辑门的缺陷

(主要集中在输出级)

可以看出中间级和输出级基本是一样的,所以输出级的缺陷具有共性

-

多个普通TTL门的输出端不能共接在同一根导线上