基于 VCS-NLP 的动态低功耗仿真验证介绍

Posted MangoPapa

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于 VCS-NLP 的动态低功耗仿真验证介绍相关的知识,希望对你有一定的参考价值。

🔥点击查看精选 IC 技能树系列文章🔥

🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/129384557】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

- 💬 直达博主:loveic_lovelife 。(搜索或点击扫码)

文章目录

简单记录下基于 VCS NLP 的动态低功耗验证仿真与 Debug 相关内容。

1. 低功耗仿真是什么

低功耗仿真(Low Power Simulation, LPS)是指对做了低功耗设计的芯片进行低功耗相关功能的仿真验证。低功耗仿真通常包括静态仿真和动态仿真,通过低功耗仿真,能够提前发现低功耗相关设计缺陷并减少返工。

1.1 低功耗技术

在低功耗仿真之前需要搞清楚低功耗技术有哪些。以下几篇文章介绍得挺好:

总结下来,常用的低功耗技术有:

- 静态低功耗技术

- 多阈值工艺(Multi-Vt Design)

- 门控电源(Power Gating)

- 体偏置(Body Bias)

- 动态低功耗技术

- 多电压阈(Multi-Voltage Domain)

- 预计算

- 门控时钟(Clock Gating)

- 门级优化技术

- 毛刺的消除

- 逻辑级优化

- 物理级优化

- 控制输入向量

- RTL级的一些低功耗设计方法

- 并行结构与流水结构

- 资源共享与优化编码

- 操作数隔离

1.2 UPF 简介

芯片设计中,为了实现低功耗设计意图,各家有各家的方法。Synopsys 采用统一电源格式 (Unified Power Format, UPF) 文件来描述芯片设计中的低功耗设计意图。关于 UPF 的语法及使用我们不作介绍,可以参考 Synopsys NLP 文档,或参考以下几篇文章:

- Lower power design & UPF 学习

- VCS Native Low Power (NLP) (synopsys.com)

- 低功耗验证(一) CMOS基础,功耗分类,低功耗方法

- 低功耗验证(二)UPF,低功耗流程,VCS NLP

- 低功耗和UPF介绍

- 低功耗设计——基于UPF进行设计

2. 低功耗验证验什么

为了实现低功耗,设计了什么我们就验什么。对于前端验证而讲,我们更关注动态低功耗技术。在仿真的时候,我们较多关注的地方有:

- 电源网络描述是否正确

电压域(Power Domain) 划分是否正确,供电电压是否正确。- 电压域边界的

供电端口(Supply Port) 是否正确,供电网络 (Supply Ner) 连接是否正确。 电源开关(Power Switch) 的输入、输出及使能信号是否正确。

- 电源状态表 (Power State Table, PST) 覆盖率,是否覆盖全,是否出现了非预期的状态切换

- 低功耗单元实现是否正确。

隔离 (Isolation) 单元,确保钳位值(Clamp Value)正确,尤其是防止 Power Off Domain 传播 X/Z 或非预期的值到 Power On Domain。电压转换 (Level Shifting)单元。信号在不同电压域之间传播时需要做电压转换,要确保是否有做,转换方向是否正确。寄存器保持 (Retention) 单元。有些寄存器需要在 Power Off 后保持原来的值,应采用保持寄存器。电源开关单元。

- Power Sequence。Power Sequence 一般是 DV 根据 Power Spec 的要求在 tb 里写的,确保按照该顺序能够正常上下电及正常工作。要确保 PMU 中的 FSM 完全遍历,且能够从不同的 Sleep Mode 唤醒。

- 其他

- Power Domain 上下电、Free-run clock 等的断言

- 形式验证

3. 低功耗仿真流程

VCS 提供了 VC LP (Low Power) 及 NLP (Native Low Power) 这两个工具分别来做静态低功耗检查及动态低功耗仿真。我们只看下基于 VCS NLP 的动态低功耗仿真流程。

VCS NLP 集成了低功耗仿真的功能,能够与 VCS 协同仿真,只需要采用以下方式来指定 UPF 文件即可实现带 UPF 的低功耗仿真:

vcs -upf <upf_file>

3.1 常用 FLow

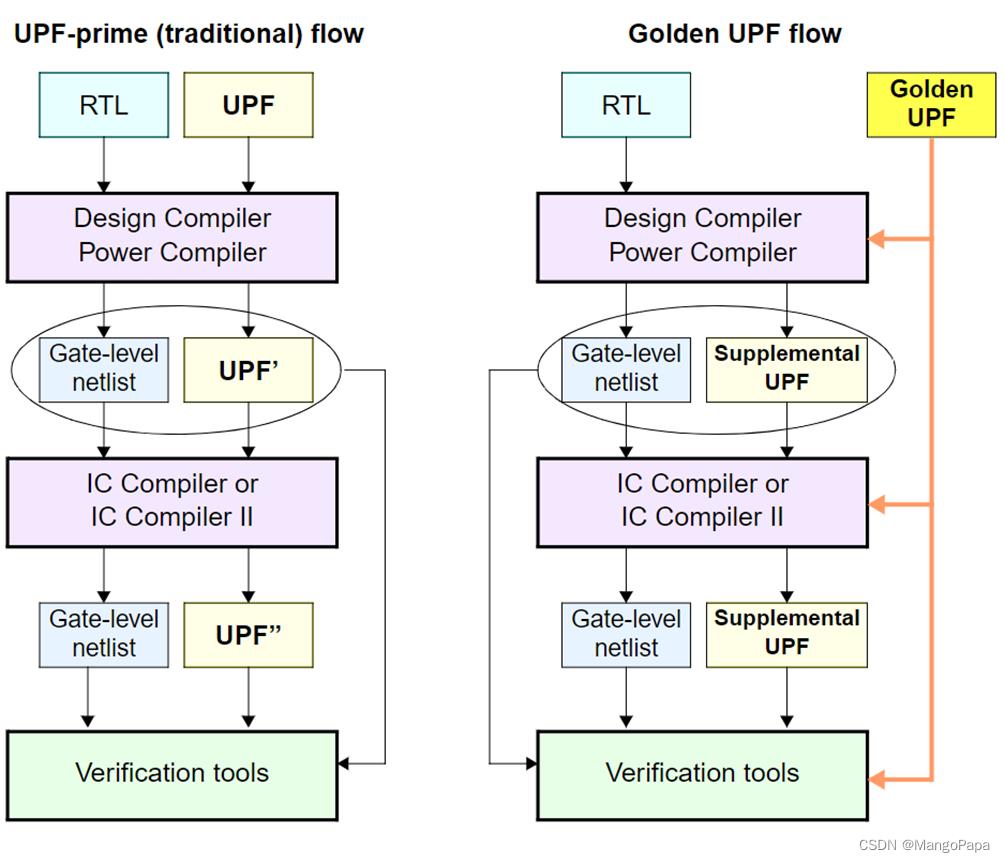

有两种常用的低功耗仿真 Flow:一种是传统的 UPF-prime Flow,该 Flow 需要设计人员在不同阶段提供 3 个不同的 UPF;另一种是 Synopsys 推荐的 Golden UPF Flow,该 Flow 只需要在最开始提供一个能够在前仿和门仿中复用的 Golden UPF。两种 Flow 流程图如下图所示。Golden UPF Flow 详查文档:Golden UPF Flow Application Note。可复用的 Golden UPF 写法参考:Writing Reusable UPF For RTL And Gate-Level Low Power Verification。

总结一下,按照时间顺序,低功耗仿真分为以下几个阶段:

-

RTL+UPF。此时 RTL 为逻辑综合前的 RTL, RTL 还没有插入 Low Power Cell (Isolation, Retention, Level Shifter, Power Switch 等) 和 PG (Power & Ground) Pin,VCS 根据 UPF 插入虚拟 Cell 和 Net。此时的低功耗仿真采用的 RTL 中具备 Power Supply Port 和 Power Domain,采用了具备电源信息的模拟硬核(Hard Macro),具有 X-Propagation 特性,更贴近门仿结果。 -

netlist+UPF’。此时采用 DC 逻辑综合后的门级网表,已经插入了部分 Low Power Cell (Isolation, Retention, Level Shifter),尚未插入 PG 和 Power Switch 。采用的 UPF 为逻辑综合后生成的 UPF’。此步骤非必须,看项目需求。 -

netlist+UPF’’及PG Netlist。此时采用物理实现后的门级网表。一般来讲没必要用 VCS NLP 带 UPF’’ 跑仿真,PG Netlist 里已经包含了各种 Low Power Cell、PG Pin 等 Power Aware 相关供电网络,直接用 vcs 跑 PG Netlist 即可 (不带 UPF)。

3.2 仿真具体步骤

-

找 DE/FEINT 要到 UPF 文件。

-

在 TB 中对 DUT 按照上下电顺序及时序开关电源。一般采用 UPF package 的 supply_on、supply_off 函数给指定端口供电,可以在 initial 块内也可以在 always 块内。示例如下:

// 必须 import UPF:* 才能调用 supply_on, supply_off 函数 import UPF::*; initial beign // Hierarchy 用 ‘/’ 而非 ‘.’,错用不报 Error 报 Warning supply_on("VDD", 1.1); supply_on("VSS", 0); end -

在 UPF 中设置设计属性。

-

该 UPF 通常为 DV 自己新建的 UPF,编译时采用的 UPF 也为该 UPF。该 UPF 中将 DE/FEINT 提供的 UPF load 进来,便于添加自定义的设计属性。

load /xxx/xxx/de_feint.upf -

设置 initial 块的

SNPS_reinit。initial 块常见于 PHY 等 Simulation Behavior Model 内,且 Model 分为带 PG 和不带 PG 两种(独立文件或 macro 隔离)。默认情况下 initial 块默认只执行一次,为确保某 Power Domain 内的 initial 块在 Power ON-OFF-ON 之后能够重新执行,需要在 UPF 内开启 initial 块的 reinit。示例如下:set_design_attributes -attribute SNPS_reinit TRUE \\ -models model1 model2 model3 -transitive TRUE // 设置 -transitive TRUE 后,其他模块相关属性默认为 FALSE。 -

对 ROM 等不受 UPF 掉电影响的模块设置

UPF_dont_touch,确保其 Always On。set_design_attributes -attributes UPF_dont_touch TRUE \\ -models model1 model2 model3 -

其他设计属性

-

-

vcs 编译,根据实际情况添加 vcs 编译选项

-upf <upf_file>指定低功耗仿真所用的 UPF 文件路径(必须)。这样 VCS 在编译的时候会自动调用 NLP 工具。- 指定 Power Top(必须)。一般将 tb top 作为一个 always on 的 power domain 作为 Power Top。指定 Power Top 的两种方式:

- 通过 vcs 编译选项

-power_top <top_module_name>指定; - 或在 UPF 中通过

set_design_top <tb/dut>指定 Power Top。

- 通过 vcs 编译选项

-power指定相关 vcs 编译选项(可选),可多次叠加指定,有两种形式:-power=<opt1>+<opt2>+… 或 -power=<opt1> -power=<opt2>。较为常用的选项有:-power=accurate,跳过插入虚拟 Isolation Cell。-power=attributes_on,开启 vcs_reinit,vcs_dont_reinit,vcs_always_on,vcs_dont_trigger_on_wakeup 属性。-power=cov_pst,开启 PST 覆盖率收集。

-

simv 仿真,根据实际情况添加 vcs 仿真选项。常用选项有:

-power <power_options>指定仿真运行时 upf 相关配置(可选),power_options 可以为 tcl 文件。-xprop打开 X 态传播检查(可选)。建议打开。

-

查看波形及 Log 进行 Debug

- log report 目录名为

mvsim_native_reports,其中的 WARNING 和 ERROR 均需清理。

- log report 目录名为

以下几篇文章讲低功耗仿真流程讲得挺好,可重点参考:

3.3 Verdi Debug 手段

跟 VCS-NLP 仿真配套的,可用 verdi 进行 Power Aware Debug。使用 VCS-NLP 进行仿真跑出的波形,直接用 verdi 打开波形加载 UPF,即可看到相关 Power Aware 信息。Power Aware Debug 中的 Verdi 使用重点参考以下几篇文章:

4. 其他参考及友链

- VCS Native Low Power (NLP) User Guide

- Golden UPF Flow Application Note

- Verdi® Power-Aware Debug User Guide

- Writing Reusable UPF For RTL And Gate-Level Low Power Verification

- VCS带UPF的RTL低功耗仿真介绍

- VCS自带的UPF低功耗仿真demo介绍

- 一个UPF低功耗仿真的简单例子- IC验证讨论

|

|

🔥 精选往期 IC 技能树相关博文,请查看【 数字 IC 技能树】专栏🔥

⬆️ 返回顶部 ⬆️

以上是关于基于 VCS-NLP 的动态低功耗仿真验证介绍的主要内容,如果未能解决你的问题,请参考以下文章