电子电路学习笔记(14)——LDO(低压差线性稳压器)

Posted Leung_ManWah

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了电子电路学习笔记(14)——LDO(低压差线性稳压器)相关的知识,希望对你有一定的参考价值。

一、简介

LDO(low dropout regulator,低压差线性稳压器)。这是相对于传统的线性稳压器来说的。传统的线性稳压器,如78XX系列的芯片都要求输入电压要比输出电压至少高出2V~3V,否则就不能正常工作。但是在一些情况下,这样的条件显然是太苛刻了,如5V转3.3V,输入与输出之间的压差只有1.7v,显然这是不满足传统线性稳压器的工作条件的。针对这种情况,芯片制造商们才研发出了LDO类的电压转换芯片。

二、分类

-

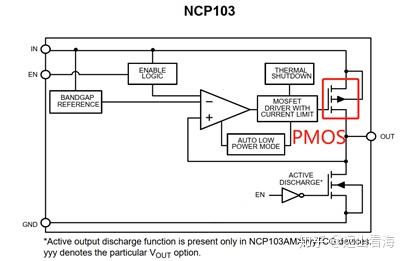

PMOS LDO:

常见的LDO是由P管构成的,由于LDO效率比较低,因此一般不会走大电流。

-

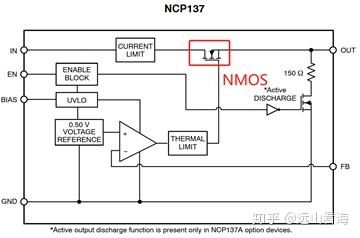

NMOS LDO:

针对某些大电流低压差需求的场合,NMOS LDO应运而生。

-

传统PNP LDO:

正输出电压的LDO(低压降)稳压器通常使用功率晶体管(也称为传递设备)作为 PNP。这种晶体管允许饱和,所以稳压器可以有一个非常低的压降电压,通常为 200mV 左右。

-

传统NPN LDO:

使用 NPN 复合电源晶体管的传统线性稳压器的压降为 2V 左右。负输出 LDO 使用 NPN 作为它的传递设备,其运行模式与正输出 LDO 的 PNP设备类似。

三、工作原理

LDO=low dropout regulator,低压差+线性+稳压器。

- 低压差: 输出压降比较低,例如输入3.3V,输出可以达到3.2V。

- 线性: LDO内部的MOS管工作于线性电阻。

- 稳压器: 说明了LDO的用途是用来给电源稳压。

3.1 内部结构

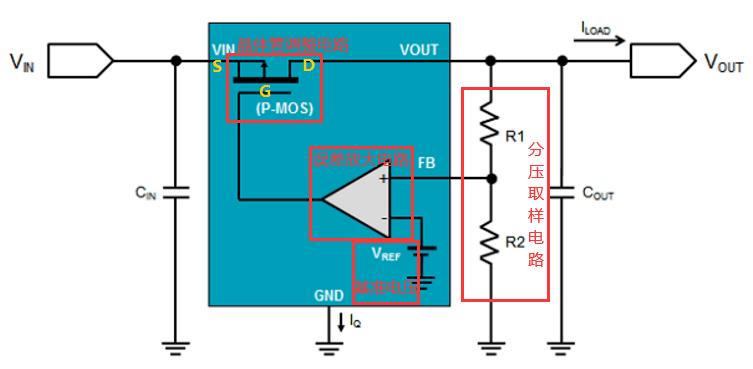

以PMOS LDO为例:

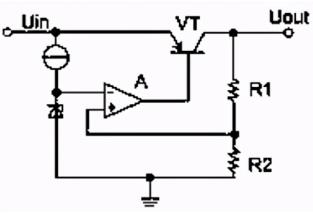

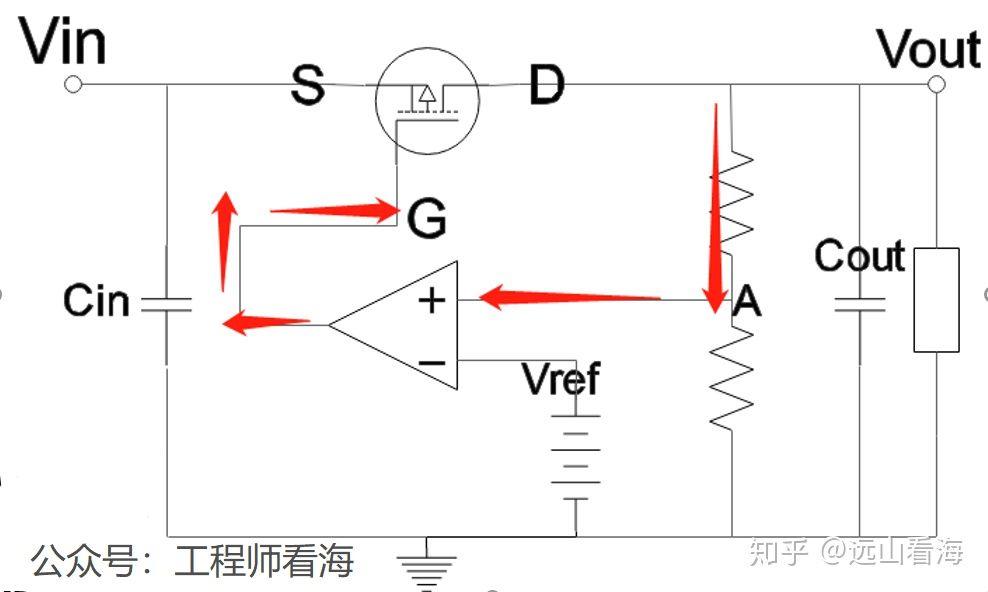

LDO内部基本都是由4大部件构成,分别是分压取样电路、基准电压、误差放大电路和晶体管调整电路。

- 分压取样电路: 通过电阻R1和R2对输出电压进行采集;

- 基准电压: 通过bandgap(带隙电压基准)产生的,目的是为了温度变化对基准的影响小;

- 误差放大电路: 将采集的电压输入到比较器反向输入端,与正向输入端的基准电压(也就是期望输出的电压)进行比较,再将比较结果进行放大;

- 晶体管调整电路: 把这个放大后的信号输出到晶体管的控制极(也就是PMOS管的栅极或者PNP型三极管的基极),从而这个放大后的信号(电流)就可以控制晶体管的导通电压了,这就是一个负反馈调节回路。

3.2 负反馈流程

以PMOS LDO为例:

- 反馈回路

-

当输出电压 V o u t V_{out} Vout由于负载变化或其他原因电压下降时,两个串联分压电阻两端的电压也会下降,进而A点电压下降,A点的电位和基准电压 V R E F V_{REF} VREF电位相比较,误差放大器会减小它的输出,使得PMOS管G极电压下降,PMOS管 V S V_{S} VS电压不变,进而使得 ∣ V G S ∣ |V_{GS}| ∣VGS∣的压差增加(我们用Vgs和Vds的绝对值描述PMOS更直观), I S D I_{SD} ISD会增加,输出电流 I o u t I_{out} Iout增加就会使得输出电压 V o u t V_{out} Vout上升,完成一次反馈控制,使得 V o u t V_{out} Vout又回到正常电位。

过程如下: V o u t ↓ — — > V A ↓ — — > V G ↓ — — > I o u t ↑ — — > V o u t ↑ V_{out}↓——>V_{A}↓——>V_{G}↓——>I_{out}↑——>V_{out}↑ Vout↓——>VA↓——>VG↓——>Iout↑——>Vout↑ -

当输出电压 V o u t V_{out} Vout增大时,A点电压 V A V_{A} VA增大,放大器输出电压增加,PMOS管的G极电压 V G V_{G} VG增大, ∣ V G S ∣ |V_{GS}| ∣VGS∣减小,PMOS的输出电流 I S D I_{SD} ISD减小,输出电压 V o u t V_{out} Vout减小。

过程如下: V o u t ↑ — — > V A ↑ — — > V G ↑ — — I > o u t ↓ — — > V o u t ↓ V_{out}↑——>V_{A}↑——>V_{G}↑——I>_{out}↓——>V_{out}↓ Vout↑——>VA↑——>VG↑——I>out↓——>Vout↓

- PMOS驱动的反馈

-

上面的描述中有两个地方格外介绍下,其一是,当 V A V_{A} VA小于 V R E F V_{REF} VREF时,G点的电位就会减小,通俗点理解,运算放大器总是倾向于使得正(+)负(-)输入端的电压相等,因此,当 V A V_{A} VA小于 V R E F V_{REF} VREF时,运放就会减小输出。

-

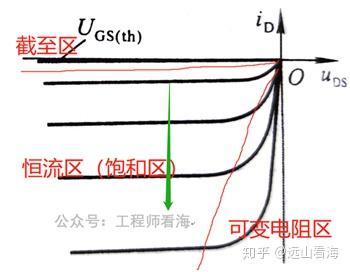

另一点是,G电位下降后为什么 I o u t I_{out} Iout就上升呢?这就涉及到PMOS工作状态,下图是PMOS的输出特性曲线,或者叫做伏安特性曲线,是PMOS本身的一个特性,根据G、D、S电压不同,MOS会工作在不同的区域,即可变电阻区,饱和区(恒流区),截至区。LDO中的MOS是工作在恒流区的。

顺着下图绿色箭头指示方向 ∣ V G S ∣ |V_{GS}| ∣VGS∣逐渐上升, I D I_{D} ID跟着 ∣ V G S ∣ |V_{GS}| ∣VGS∣上升而上升,而这段区域内不管 V D S V_{DS} VDS怎么变换 I D I_{D} ID基本不变,换句话说,恒流区内, I D I_{D} ID只受 ∣ V G S ∣ |V_{GS}| ∣VGS∣控制,因此基于MOS的放大器有时也被叫做跨导放大器。这就是PMOS LDO工作原理的核心部分。

LDO工作原理就一句话:通过运放调节P-MOS的输出。

四、主要参数

-

输入输出压差(Dropout Voltage):

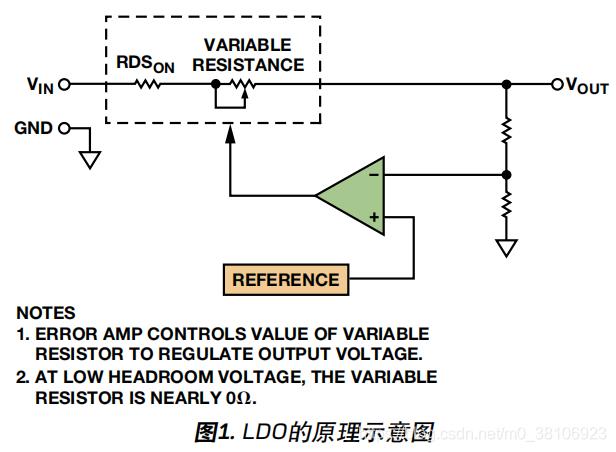

对于LDO来说,输入电压是高于输出电压的,但是两者压差一般都是很小,LDO的输入电流几乎等于输出电流,因此压差越大,效率越低(本身吃掉了很多能量电流×晶体管压降),压差越小,LDO电压转换效率越高以及能量损耗越小。压差( V D R O P O U T V_{DROPOUT} VDROPOUT)是指输入电压进一步下降而造成 LDO 不再能进行调节时的输入至输出电压差。在压差区域内,调整元件作用类似于电阻,阻值等于漏极至源极导通电阻( R D S O N RDS_{ON} RDSON)。

压差用 R D S O N RDS_{ON} RDSON和负载电流表示为:

V D R O P O U T = I L O A D × R D S O N V_{DROPOUT} = I_{LOAD}×RDS_{ON} VDROPOUT=ILOAD×RDSON

-

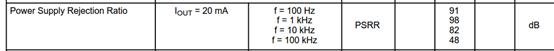

电源抑制比(PSRR):

LDO的 PSRR数据是用来量化LDO对不同频率的输入电源纹波的抑制能力的,它反映了LDO不受噪声和电压波动、保持输出电压稳定的能力。在特定频段内,PSRR越大越好。100K到1MHz内的PSRR非常重要,这个是DCDC的噪声频率范围,LDO经常作为DCDC的下一级,要有能力滤除来自DCDC的大量噪声。

在ADC,DAC,Camera的AVDD供电上,我们要选择PSRR大于80dB(@100Hz)的LDO。LDO的环路控制往往是确定电源抑制性能的主要因素,同时大容量,低ESR的电容对电源一直也非常有用,建议选择陶瓷电容。

PSRR与频率有关,LDO的规格书一般会给出几个频点的PSRR值。

-

噪声(Noise):以上是关于电子电路学习笔记(14)——LDO(低压差线性稳压器)的主要内容,如果未能解决你的问题,请参考以下文章